|

Mihai Budiu -- mihaib+@cs.cmu.edu

http://www.cs.cmu.edu/~mihaib/

7 iunie 1998

Despre hardware reconfigurabil am auzit cu puţina vreme în urmă; atracţia a fost însă imediată. Acest articol va încerca să vă transmită o parte din motivele pentru care domeniul mi se pare demn de atenţie. Unul dintre ele este faptul că relativ puţină cercetare sistematică s-a făcut în domeniul circuitelor reconfigurabile. Noţiunea în sine este destul de veche: primul prototip a fost introdus de firma Xilinx în 1986, deci cu 12 ani în urmă. O serie de conjuncturi au ţinut însă zona în umbră faţă de atenţia marilor companii şi a cercetătorilor. Brusc însă, în urmă cu cîţiva ani, o creştere a activităţii orientate spre acest subiect a putut fi observată. Principalul motiv este tehnologia.

În anii '60 Gordon Moore a observat o interesantă lege de evoluţie a densităţii şi performanţei circuitelor integrate (cele două sunt strîns legate: cu cît un circuit este mai mic cu atît poate fi făcut să funcţioneze mai repede, pentru că semnalele electrice trebuie să circule pe distanţe mai scurte). Moore a pronosticat că densitatea circuitelor se dublează la fiecare 18 luni. Evident, această evoluţie nu poate ţine la infinit, pentru că după o vreme dimensiunile componentelor ar deveni sub-atomice. Dar cît de mult se poate merge cu această rată de îmbunătăţire a tehnologiei? Ei bine, experţii s-au înşelat în numeroase rînduri prezicînd încetinirea evoluţiei: şi la ora actuală legea este valabilă. Se estimează că în următorii cinci-zece ani rata de evoluţie va putea fi menţinută.

Evoluţia tehnologiilor semiconductoarelor însă dă naştere la o creştere în salturi a celorlalte tehnologii. De exemplu, pentru că cipurile de memorii RAM sunt pătrate1, capacitatea lor în general creşte în multipli de 4 (se dublează lăţimea şi lungimea). Deci în loc să se dubleze la fiecare 18 luni, RAM-urile se cvadruplează în capacitate la fiecare 3 ani.

Un salt mai spectaculos este evident în următorul exemplu: la începutul anilor '70 densitatea a devenit suficient de mare pentru a permite plasarea tuturor componentelor unei unităţi centrale pe un singur integrat. Aşa a apărut microprocesorul (primul microprocesor, 4004, a fost creat de firma Intel). La începutul anilor '80 aceeaşi creştere a permis înghesuirea pe o singură pilulă de siliciu a tuturor tranzistorilor (între 25.000 şi 50.000) pentru un microprocesor complex pe 32 de biţi. Atunci cînd poţi pune toate părţile la un loc de fapt saltul calitativ este mult mai mare, pentru că legăturile dintre circuite se reduc substanţial, şi performanţa creşte brusc.

La ora actuală cele mai complexe microprocesoare (Pentium II de pildă) au peste 15,000,000 de tranzistori! Cu aceeaşi rată de evoluţie, în acelaşi spaţiu în 2005 vor încăpea peste 1 miliard de tranzistori.

Tot evoluţia tehnologică a scos şi circuitele reconfigurabile, despre care vorbeam mai sus, din anonimat. Subit ele au devenit suficient de mari şi de complicate pentru a putea implementa în mod eficient aplicaţii interesante.

Două motive fac deci interesant studiul circuitelor reconfigurabile:

Ce este deci hardware-ul reconfigurabil? Înainte de a răspunde la această întrebare voi face o scurtă şi incompletă trecere în revistă a celorlalte paradigme hardware folosite. Prin contrast vom înţelege mai bine care sunt calităţile şi lipsurile noii generaţii de circuite.

Putem distinge două feluri de circuite: care pot fi programate şi care nu. Din prima categorie fac parte microprocesoarele, din a doua circuitele integrate specifice unei aplicaţii (ASIC: Application Specific Integrated Circuits). Vom vedea şi nişte categorii intermediare.

Un microprocesor este practic o colecţie de unităţi funcţionale plasate pe ceea ce se numeşte ``data-path'' (cărare a datelor?). Simplificată la maximum, funcţionarea unui procesor poate fi descrisă în următorii termeni:

Să observăm următoarele caracteristici ale unui microprocesor, pe care le vom contrasta apoi cu cele ale hardware-ului reconfigurabil:

Cu toate acestea, cantitatea de paralelism disponibilă unui procesor este relativ limitată. Un procesor Pentium II poate teoretic lansa în execuţie 4 instrucţiuni simultan, dar în medie, măsurînd performanţa pe programe mari, reuşeşte să execute doar în jur de 2 pe fiecare ciclu de ceas (din felurite motive, cum ar fi instrucţiuni succesive care vor aceeaşi unitate funcţională).

Un microprocesor trebuie să fie ``bun la toate'' şi nu este excelent pentru nimic. Anumite tipuri de calcule nu pot fi făcute cu procesoare din această cauză; este nevoie de ASIC-uri.

Atunci cînd ştii exact ce ai de calculat şi timpul disponibil este foarte puţin, nu ai de ales altceva decît să proiectezi un circuit care face numai acel lucru. Un astfel de integrat, construit să rezolve o singură problemă, se numeşte ASIC.

Un exemplu tipic de ASIC este cipul DES care criptează cu algoritmul de criptografie cu cheie privată Data Encryption Standard. Într-un PC se găsesc o grămadă de ASIC-uri, de la controlerele de magistrală la controlerele perifericelor. (Într-un PC se pot găsi şi mai multe procesoare; unele periferice sunt controlate de procesoare al căror program este fixat odată pentru totdeauna.)

Un ASIC este mult mai simplu, mai ieftin şi mai rapid decît un microprocesor. Dar nu este deloc flexibil: nu poate rezolva decît o singură problemă.

Atît microprocesoarele2 cît şi ASIC-urile sunt construite din fabrică şi aşa rămîn pînă la moarte. Există însă nişte clase de circuite care pot fi modificate de către utilizator, la o scară redusă.

Procesoarele cu set de instrucţiuni complex (CISC: Complex Instruction Set Computer) sunt adesea implementate folosind în interior microcod. Practic acţiunile indicate mai sus: decodificarea instrucţiunii, execuţia, scrierea rezultatului, etc., sunt mult mai complexe pentru un CISC, şi sunt fiecare descompuse la rîndul lor în instrucţiuni mai simple. Pentru fiecare pas se execută deci un progrămel, numit microprogram, care indică fiecărei unităţi funcţionale ce să facă. Microprogramul este de obicei înscris într-o memorie ROM din interiorul procesorului. 'Procesoarele CISC mai vechi uneori permiteau utilizatorilor să schimbe microcodul în timpul funcţionării, permiţînd sinteza de noi instrucţiuni, care nu existau la fabricarea procesorului. Libertatea era însă relativ limitată. (Microprocesorul Pentium Pro permite ``microcode patching'': peticirea microcodului. Aceasta este o tehnologie introdusă de Intel după apariţia celebrului bug din Pentium, care efectua greşit împărţirea. Algoritmul de împărţire era scris în microcod şi avea un bug. Acum Intel poate corecta astfel de erori chiar după ce procesorul a fost livrat utilizatorilor, prin software. Acest subiect însă depăşeşte cadrul acestui articol.)

O altă varietate de circuite configurabile conţine, printre altele, clasa numită PLA: Programmable Logic Array. Acest tip de circuite poate fi modificat ``off-line'' (adică nu în timp ce funcţionează). Un PLA tipic conţine un rînd de porţi SAU şi un rînd de porţi ŞI. Fiecare ieşire de la o poartă SAU este conectată la fiecare intrare la o poartă ŞI, avînd astfel o matrice de conexiuni. Cel care foloseşte circuitul poate suda sau desface unele dintre conexiuni, obţinînd felurite funcţionalităţi. Pentru că orice funcţie logică se poate exprima folosind o conjuncţie de disjuncţii, astfel se poate (teoretic) sintetiza orice circuit. Desigur că metoda nu este practică pentru circuite complicate, dar este folosită cîteodată pentru a sintetiza ``glue logic'': circuite care fac legătura între alte circuite.

Motivul pentru care PLA-urile sunt importante este unul economic: desigur că am putea fabrica un ASIC pentru fiecare funcţionalitate a unui PLA, dar atunci ar costa mult mai mult. Toate PLA-urile sunt de fapt la fel, deci sunt fabricate de o singură linie tehnologică, pe cînd fiecare ASIC care calculează o altă funcţie este diferit, deci are nevoie de propria lui linie de fabricaţie.

Am văzut deci că hardware-ul tradiţional are în general o funcţionalitate fixată de la bun început de către fabricant; această funcţionalitate poate fi controlată şi multiplexată în timp, ca la microprocesoare, pentru a sintetiza funcţii noi, sau poate fi fixată odată pentru totdeauna, ca la ASIC-uri. Anumite genuri de circuite pot fi făcute să facă lucruri pentru care nu au fost proiectate (ca procesoarele cu microcod), sau pot fi schimbate cu un efort considerabil (ca PLA-urile).

Ce-ar fi însă dacă am avea un circuit a cărui funcţionalitate să poată fi schimbată la fel de repede pe cît funcţionează (spre deosebire de PLA, la care treaba asta durează minute sau ore), şi care să permită o flexibilitate totală (spre deosebire de microcod, care poate doar controla unităţile funcţionale existente)? Ce-ar fi dacă circuitele astea s-ar putea configura prin aceleaşi mecanisme folosite pentru a le folosi (spre deosebire de anumite memorii EEPROM care sunt şterse prin expunere la ultraviolete)? Ce-ar fi dacă am avea un circuit care ar putea să-şi schimbe funcţionalitatea în timp ce lucrează?

Există aşa ceva? Da; se numeşte hardware reconfigurabil.

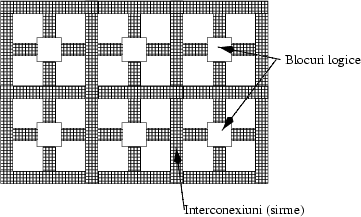

Un circuit hardware reconfigurabil constă din două entităţi distincte: porţi logice şi sîrme care leagă porţile. Spre deosebire de circuitele VLSI obişnuite, funcţionalitatea unei porţi nu este fixată, ci poate fi schimbată dinamic. De asemenea, sîrmele se întind de-a lungul circuitului, iar la fiecare intersecţie se află un mic comutator. Fiecare comutator poate fi închis sau deschis prin software. Un circuit reconfigurabil generic arată cam ca în figura 1.

Tehnologic problema este foarte simplă; ambele dispozitive se pot face reconfigurabile folosind mici celule de memorie.

O poartă logică ``universală'' cu două intrări de 1 bit şi o ieşire de 1 bit se poate sintetiza folosind o memorie cu capacitatea de 4 cuvinte de 1 bit. Cele două intrări sunt adresa cu care se indexează în memorie, iar conţinutul memoriei este ieşirea. Iată de exemplu care cum se pot sintetiza felurite porţi în acest fel:

| Conţinutul memoriei | |||

| adresa | |||

| 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 |

E clar cum lucrează? De pildă, dacă vrem să folosim memoria ca o

poartă SAU (![]() ) o să încărcăm în cei 4 biţi valorile 0, 1,

1, respectiv 1. Atunci cînd vrem să calculăm ``

) o să încărcăm în cei 4 biţi valorile 0, 1,

1, respectiv 1. Atunci cînd vrem să calculăm ``![]() '',

primul bit la intrare va fi 1, iar al doilea 0. Asta formează la un

loc adresa 10 (2 în baza 2); cuvîntul de memorie de la adresa 2 este

1, deci

'',

primul bit la intrare va fi 1, iar al doilea 0. Asta formează la un

loc adresa 10 (2 în baza 2); cuvîntul de memorie de la adresa 2 este

1, deci ![]() . Corect.

. Corect.

În terminologia hardware-ului reconfigurabil, o astfel de memorie folosită pentru a calcula valoarea unei funcţii booleene se numeşte, din motive evidente, ``tabelă de căutare'', Look-Up Table, LUT. Blocurile logice folosite în circuitele comerciale conţin mai multe astfel de ``porţi''.

Cu ajutorul LUT-urilor putem schimba funcţionalitatea unei porţi logice. Cu ajutorul comutatoarelor (switch) putem schimba interconexiunile. Imaginaţi-va o grilă formată din ``sîrme'', iar la fiecare intersecţie de sîrme un tranzistor, cu emitorul pe o sîrmă şi cu colectorul pe cealaltă. Baza tranzistorului este cuplată la o memorie care conţine un singur bit. Dacă în memorie punem un ``1'', atunci tranzistorul va conduce electric între emitor şi colector, realizînd o conexiune între cele două sîrme. Dacă baza este la ``0'', atunci sîrmele sunt izolate electric una de cealaltă. Figura 2 ilustrează cum se poate conecta ieşirea unei porţi la intrarea alteia.

|

Putem deci configura foarte simplu legăturile dintre elementele de procesare, folosind un bit pentru fiecare intersecţie.

Aceste două elemente reconfigurabile, ``porţile'' şi comutatoarele, fac întregul circuit extrem de flexibil. Prin simpla operaţiune de scriere într-o memorie putem schimba dinamic funcţionalitatea circuitului! Din această cauză voi numi astfel de circuite reconfigurabile, prin contrast cu circuitele configurabile: putem oricînd să le schimbăm cu uşurinţă configuraţia, într-un timp relativ scurt.

La ora actuală există mai multe firme care produc circuite integrate reconfigurabile comerciale. Cele mai importante sunt, în ordinea volumului de circuite de acest gen: Xilinx, Altera, AT&T, Actel, Quicklogic. Fiecare din aceste firme produce mai multe tipuri de circuite, folosind tehnologii diferite, cu diferite complexităţi ale tabelelor, cu mici bucăţele de hardware specializat vîrîte printre porţile generice, etc. Ideea de bază însă este cea descrisă mai sus.

Denumirea acestui gen de circuite nu este încă bine împămîntenită; termenul care capătă însă cea mai mare acceptare este cel de ``matrici de porţi logice programabile cu ajutorul cîmpului [electromagnetic]'': Field Programmable Gate Arrays, FPGA.

Înainte de a vedea care sunt deficienţele circuitelor reconfigurabile şi problemele care sunt de rezolvat de către cercetare în ceea ce le priveşte, să aruncăm o privire la domeniile în care aceste circuite sunt foarte necesare.

Trebuie de la bun început înţeles că hardware-ul reconfigurabil nu îşi propune să înlocuiască celelalte paradigme de calcul, ci să le suplimenteze. Locul unităţilor reconfigurabile este alături de cele clasice (procesoare, ASIC-uri), pentru a executa acea parte din treabă care li se potriveşte cel mai bine. Există mai multe propuneri de utilizare a acestui tip de hardware, care diferă prin gradul de integrare cu sistemul. Iată unele dintre posibilităţi enumerate în ordine descrescătoare a integrării:

Putem distinge două clase de aplicaţii: unele care în mod tradiţional sunt rezolvate folosind ASIC-uri, şi altele care necesită procesoare. Iată ce poate ``fura'' de la fiecare din ele noua tehnologie:

Trebuie dinainte spus că dacă putem implementa aceeaşi soluţie pe un ASIC şi pe un circuit reconfigurabil, soluţia cu ASIC-ul va fi mai rapidă în execuţie. Motivele sunt multiple, şi le vom explora în secţiunea consacrată deficienţelor. Cu toate acestea circuitele reconfigurabile nu sunt deloc inutile! Marile lor avantaje faţă de ASIC-uri sunt preţul scăzut şi reconfigurabilitatea.

Iată deci genurile de aplicaţii la care se pretează excelent hardware-ul reconfigurabil:

Hardware-ul reconfigurabil are şansa să bată microprocesoarele în performanţă pentru anumite genuri de aplicaţii. Care sunt acestea? Pentru a răspunde trebuie să înţelegem de fapt unde-şi petrece timpul un program.

Un procesor care rulează la 300Mhz şi lansează în medie 2 instrucţiuni pe ciclu (tipic pentru un Pentium II modern) va executa 600 de milioane de instrucţiuni pe secundă. Mai mult decît numărul total de instrucţiuni din cel mai mare program scris vreodată. Este clar, timpul este petrecut re-executînd o serie de instrucţiuni de multe ori. De fapt orice program are undeva o buclă în care-şi petrece majoritatea timpului. O regulă empirică spune că 90% din timp se execut'a 10% din cod; de fapt numerele sunt mai aproape de 98%/2%.

Asta înseamnă că dacă reuşim să optimizăm acele 2% din program pentru a mearge de 2 ori mai rapid, întreaga durată a programului se reduce aproape la jumătate! Orice cîştig de performanţă în ``cea mai interioară buclă'' (innermost loop) este foarte important.

Dacă vă uitaţi la caracteristicile procesoarelor enumerate mai sus, vedeţi care sunt exact caracteristicile care pot fi exploatate de un circuit reconfigurabil:

De fiecare dată cînd un program are nevoie de astfel de operaţii care se sintetizează greu din instrucţiuni primitive ale unui procesor este un candidat bun la implementarea pe un circuit reconfigurabil.

Această tehnologie este un subiect foarte fierbinte în teoria compilatoarelor, şi se numeşte dynamic code generation: generezi cod abia atunci cînd ştii maximum de informaţie. Compilatoarele de tip JIT (Just In Time), sau Hot-Spot de la Sun de pildă, folosesc chiar această tehnică.

Metoda este cu atît mai eficientă în cazul circuitelor reconfigurabile, pentru că libertatea este mult mai mare decît în cazul unui procesor în ceea ce priveşte ``cărămizile'' de bază.

La ora actuală cele mai rapide cipuri de criptare sunt construite folosind hardware reconfigurabil, tocmai pentru că folosesc toate tehnicile de mai sus: după ce cheia este cunoscută se generează un circuit special care criptează cu o singură cheie, şi care este extrem de eficient.

Alt exemplu interesant: să considerăm setul de instrucţiuni MMX introdus de Intel pentru procesoarele sale. MMX un set de instrucţiuni foarte specializat, destinat procesării de semnale pentru aplicaţii multimedia. Problema principală a lui Intel este de compatibilitate: lumea se fereşte să scrie programe folosind instrucţiuni MMX pentru că acestea nu se pot executa pe procesoare care nu au această extensie (sau se pot executa numai foarte lent, folosind emulare software). MMX sunt exact instrucţiuni care se pot implementa foarte simplu şi eficient în hardware reconfigurabil: se aplică la date de dimensiuni bizare (de obicei pe cîte 8 biţi), sunt destinate unor procesări vectoriale, care poate fi de obicei eficient tradusă în regim de pipe-line. Dacă Intel ar fi avut nişte hardware reconfigurabil în Pentium, nu ar mai fi avut grija compatibilităţii şi eficienţei instrucţiunilor MMX: oricine le putea sintetiza automat la momentul execuţiei, şi eventual, dacă se dovedea că unele dintre instrucţiuni nu erau prea folosite, puteau fi scoase din configuraţie, fără a schimba nimic în linia de fabricaţie a chipului! (Motorola a introdus de curînd o serie de procesoare care conţine astfel de hardware.)

Să nu credeţi că FPGA-urile sunt un panaceu; există o grămadă de probleme caracteristice numai lor; unele pot fi rezolvate, altele sunt probabil intrinseci:

O altă dificultate majoră este proiectarea de programe care folosesc simultan microprocesorul şi o unitate reconfigurabilă auxiliară. Cu tehnologia curentă, programatorul trebuie atunci nu numai să scrie programele pentru ambele procesoare, ci şi să aibă grijă de comunicaţia dintre programul de pe procesor şi cel de pe circuitul auxiliar. Programatorii nu sunt obişnuiţi să gîndească în astfel de termeni.

În al treilea rînd avem o problemă de inadecvare a limbajelor. Un limbaj de nivel înalt, ca C-ul, exprimă uneori concepte care nu sunt uşor sau eficient de modelat pe un circuit reconfigurabil. Luînd exemplul de mai sus, cu inversarea biţilor, un programator nici nu poate scrie aşa ceva în C decît folosind o buclă. Cum ar putea atunci un compilator pentru FPGA să observe că utilizatorul vrea de fapt doar să mişte nişte sîrme? Nu e un lucru evident nici pentru un om. Încă nu este clar ce fel de limbaje ar trebui folosite în domeniu.

Voi încheia acest text cu descrierea sumară a cercetării care se desfăşoară la Universitatea Carnegie Mellon. Proiectul are o pagină de web, dar deocamdată acp;p se află destul de puţină informaţie pentru că încă nu avem rezultate substanţiale4. Puteţi ajunge acolo folosind o legătură din pagina mea personală de web.

Carnegie Mellon are două grupuri care lucrează la un prototip special de circuit reconfigurabil numit PipeRench. Asta vine de la ``pipe'': ţeavă (subliniind natura ``pipelined'' a circuitului) şi ``wrench'': cheie franceză. Circuitul acesta se vrea o unealtă generală pentru a scrie aplicaţii ``pipelined''. Unul dintre grupuri lucrează la proiectarea, depanarea şi construirea unui circuit prototip şi a interfeţei sale cu un sistem de calcul (bazat pe o magistrală PCI), iar celălalt la un compilator care să genereze cod pentru PipeRench. Între cele două grupuri există o oarecare independenţă, în sensul că, deşi pentru moment compilatorul dezvoltat are ca singură ţintă prototipul PipeRench, în mod ideal ar trebui să fie uşor portat şi pentru alte feluri de circuite reconfigurabile, cum ar fi cele comerciale.

De la început au fost făcute o serie de decizii în spaţiul posibilelor design-uri, care limitează aplicabilitatea, dar fac problema tractabilă. Ca oricînd în cercetarea ştiinţifică, nu este clar de la început că aceste decizii au fost cele mai bune; numai viitorul va arăta dacă această cărare este profitabilă, sau dacă rezultatele vor fi foarte specifice.

Voi discuta pe scurt unele dintre deciziile mai interesante, pentru a ilustra natura unora dintre problemele întîlnite şi soluţiile oferite.

Principalele aplicaţii care sunt ţinta implementării pe PipeRench sunt cele care aplică o aceeaşi procesare relativ complicată asupra unui set mare de valori (unui vector). Exemple ideale: compresia, criptarea, codificarea, filtrarea de semnal, analiza statistică, etc. PipeRench va implementa atunci funcţiunea care trebuie aplicată repetat şi datele vor fi trimise una cîte una spre el; la ieşire se vor culege rezultatele.

PipeRench are un controler special care este capabil să genereze adrese pentru magistrală pentru a citi şi scrie singur din memorie. Controlerul are mai multe scopuri:

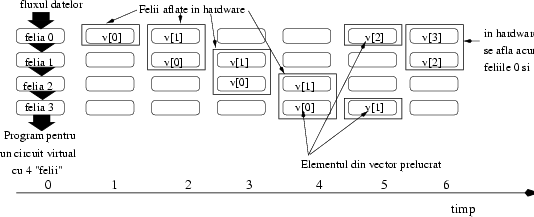

Probabil cea mai interesantă decizie este aceea de a ``virtualiza'' hardware-ul. Aceasta simplifică enorm scrierea de programe, pentru că utilizatorul nu mai trebuie să se preocupe de resursele disponibile. Ideea este asemănătoare cu cea de la memoria virtuală:

În felul acesta circuitul hardware ``alunecă'' (ca în figura 3) peste program. Figura ilustrează primii 6 paşi din procesarea unui vector v[] de valori. Fiecare valoare a vectorului trebuie procesată de un program în 4 paşi. Fiecare ``felie'' virtuală este un pas din program. Datele intră în felia 0, trec apoi prin 1, 2 şi ies din 3, după care sunt scrise în memorie. Aceeaşi operaţie este aplicată tuturor elementelor din vector. Pentru figură deci m=4, n=2.

|

Metoda are o sumedenie de avantaje. De exemplu, atunci cînd apare un circuit mai mare pe piaţă, programele se vor executa mai repede, pentru că vor avea mai mult hardware la dispoziţie. Nu trebuie deloc recompilate. În plus, putem executa azi (mai lent) programe pentru care nu vom avea destul hardware decît mîine.

După cum vedeţi fiecare felie lucrează la un moment asupra altor date de intrare; la fiecare m/n paşi se produce un rezultat.

Din cauză că felia 1 este scoasă cînd apare n+1 e clar că datele pot curge numai într-o direcţie în acest circuit. Acest model este asemănător cu al maşinilor ``data-flow'' (subiectul depăşeşte cadrul acestui articol). În principiu orice aplicaţie poate fi adusă în această formă, dar nu orice aplicaţie este eficient prelucrată astfel.

Pentru a uşura sarcina utilizatorilor dezvoltăm un compilator a cărui ţintă este PipeRench. Există foarte puţină experienţă în a scrie compilatoare pentru limbaje imperative gen C pentru astfel de maşini:

Pentru a fi relativ independent de limbajul sursă (poate va fi Java, poate C, poate ML?) şi de circuitul destinaţie, compilatorul trebuie să folosească nişte abstracţii pentru hardware şi limbajul surşa. Aceste abstracţii trebuie să nu fie atît de generale încît să ascundă complet hardware-ul, pentru că atunci nu se poate obţine eficienţă.

Deocamdată compilatorul nostru ia ca sursă un limbaj intermediar special funcţional (numit DIL: Data Intermediate Language) care descrie eficace calcule pe şiruri de biţi de lungimi arbitrare. Compilatorul traduce programe Dil în asamblare pentru PipeRench. ``Gaura'' dintre C şi Dil este (sperăm) ceva mai uşor de umplut decît direct dintre C şi asamblare; cum se face asta este subiectul cercetării viitoare.

Iată pe scurt în figura 4 care sunt sculele pe care proiectul le-a dezvoltat şi cu care experimentează tot felul de parametri arhitecturali şi tehnici de compilare.

Sculele hardware sunt în partea stîngă a desenului; din programe scrise în Verilog (un HDL) se poate sintetiza fie direct circuitul configurabil, fie se poate simula funcţionarea circuitului.

Sculele desenate cu linie punctată încă nu există. În principiu compilarea va trece prin următorii paşi:

Configuraţia este apoi oferită circuitului reconfigurabil (sau simulatorului), care se execută în tandem cu procesorul.

La ora aceasta o versiune preliminară a tuturor programelor desenate cu linie continuă există şi este în curs de evaluare. Deşi partea din stînga a figurii pare mult mai mică, este extrem de complicată, pentru că hardware-ul reconfigurabil conţine circuitul propriu-zis, controlerul pentru memorie şi configurare, şi o interfaţă pentru o magistrală PCI care este în proiectare.

Hardware-ul reconfigurabil promite un viitor frumos, datorită capacităţii sale de a-şi schimba funcţionalitatea extrem de rapid, poate chiar în timpul funcţionării. Abilitatea de a folosi operaţiuni de bază extrem de simple îl face un candidat pentru a implementa procesări care în mod convenţional nu se pot exprima cu uşurinţă. Capacitatea sa de reconfigurare îi poate da şi alte atribute dezirabile, cum ar fi rezilienţa la erori şi capacitatea de virtualizare a resurselor.

Nu mai este o dilemă dacă circuitele reconfigurabile vor intra sau nu în galeria uneltelor ordinare ale arhitectilor calculatoarelor şi utilizatorilor lor. Singura întrebare este ``cînd'' se va petrece acest lucru. Răspunsul depinde numai de cei care cercetează în acest domeniu: cît de repede vor reuşi să găsească optica cea mai potrivită şi uneltele cele mai eficace pentru a exploata puterea expresivă a acestor circuite.