# One Size Almost FILS ALL

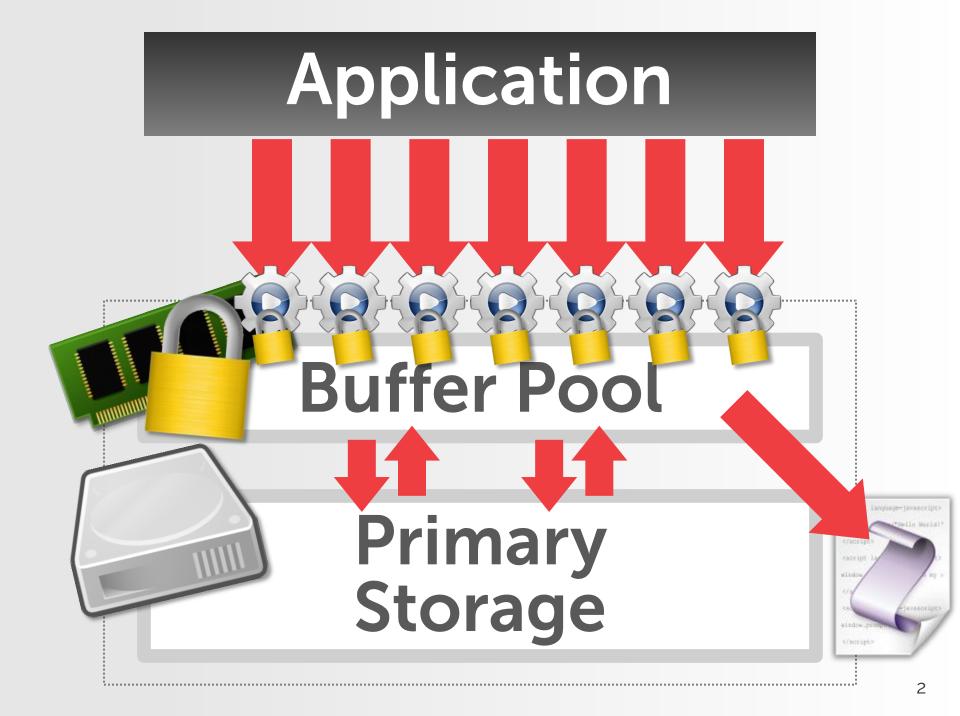

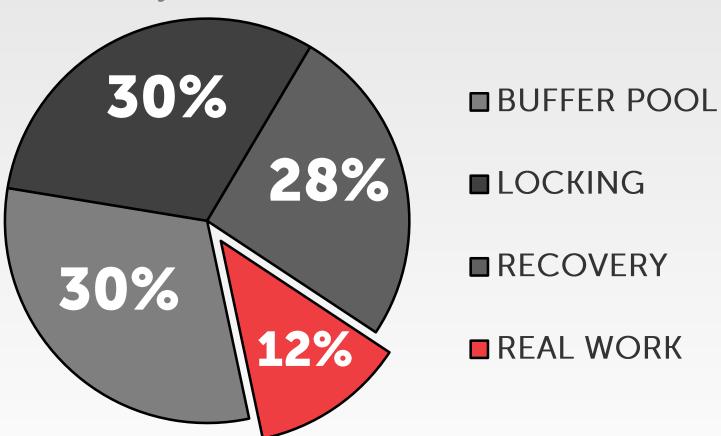

#### **Disk-Oriented Overhead**

Measured CPU Cycles

## DISKORIENTED MAIN MEMORY STORAGE

## = CONCURRENT EXECUTION SERIAL EXECUTION

## HEAVYWEIGHT RECOVERY COMPACT LOGGING

#### STORED PROCEDURE

```

VoteCount:

InsertVote:

SELECT COUNT(*)

INSERT INTO votes

VALUES (?, ?, ?);

FROM votes

WHERE phone num = ?;

run(phoneNum, contestantId, currentTime) {

result = execute(VoteCount, phoneNum);

if (result > MAX VOTES) {

return (ERROR);

execute(InsertVote, phoneNum,

contestantId,

currentTime);

return (SUCCESS);

```

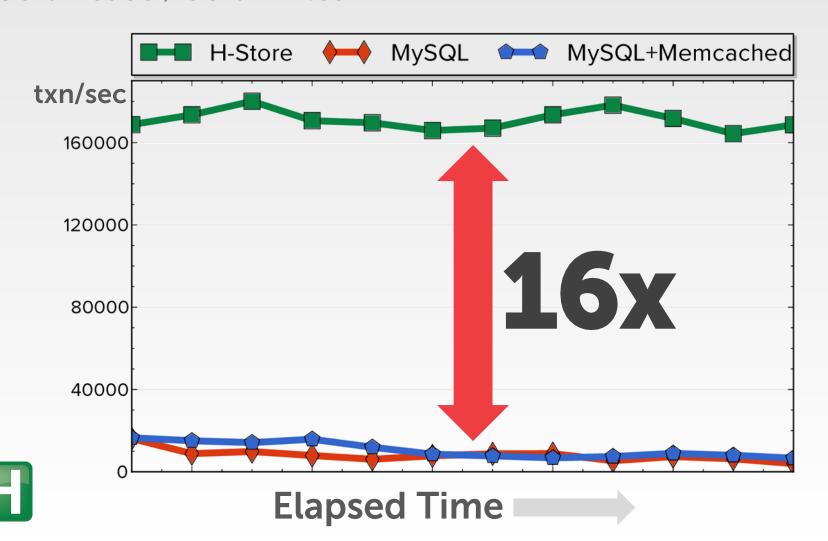

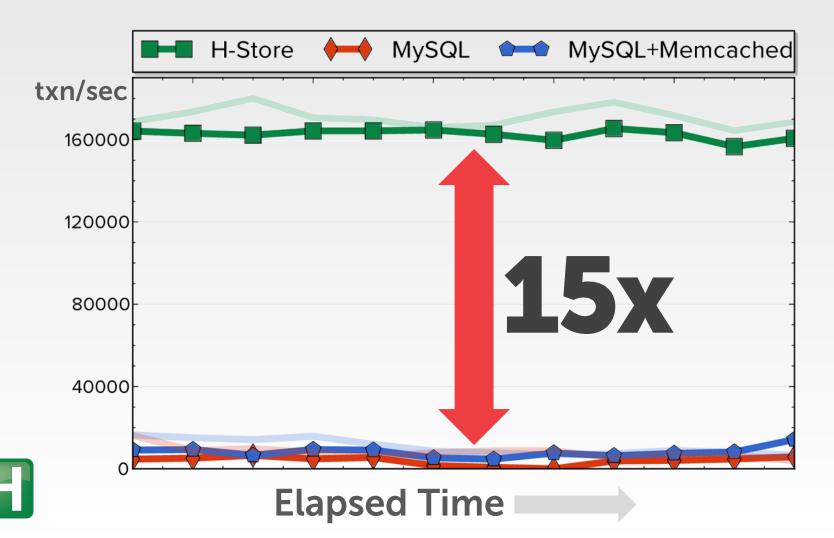

#### **YCSB**

50% Reads / 50% Writes

### YCSB (2x Memory)

50% Reads / 50% Writes

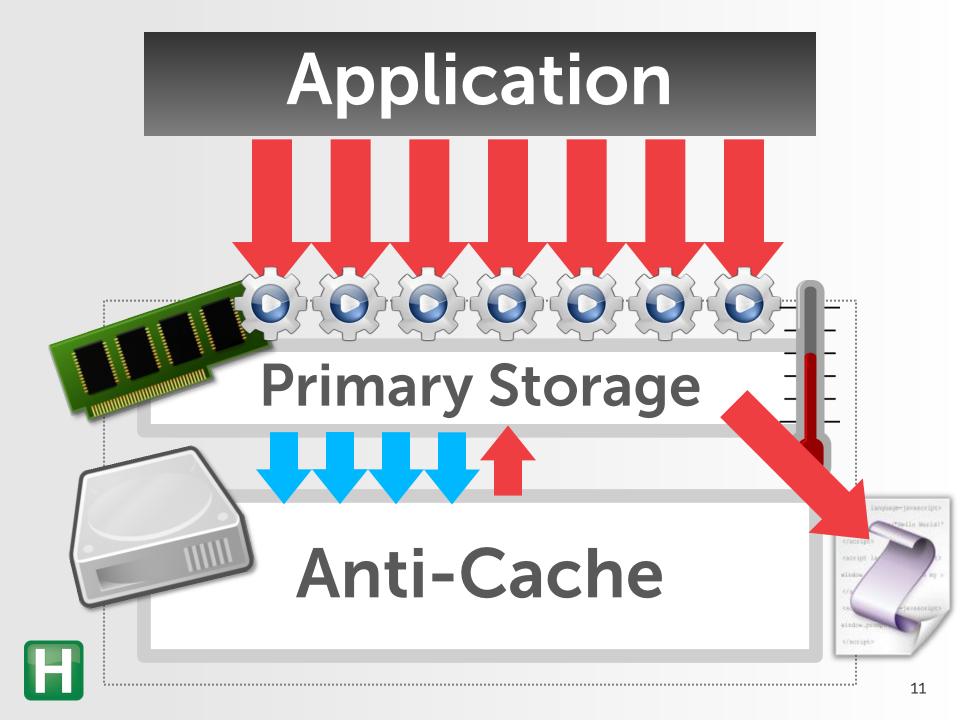

#### **Anti-Caching**

- Overhead Reduction.

- In-Memory Compression.

- Vertical Partitioning.

#### **Next-Generation CPUs**

- Concurrency control

evaluation on +1000 cores

simulated architecture.

- Multiple cores per partition.

H-Store

**S-Store**

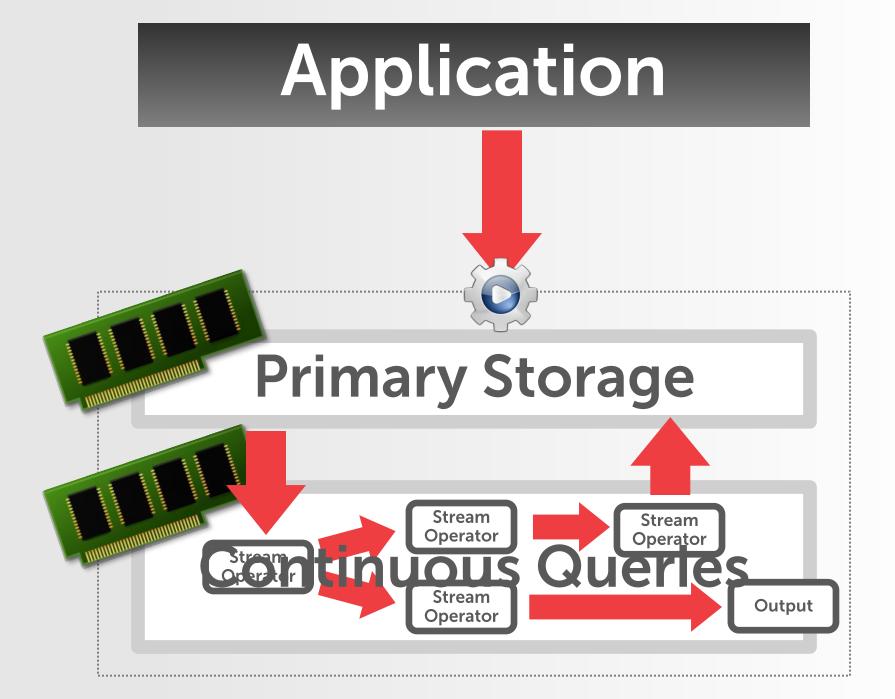

#### S-Store

Integrate distributed stream processing operators directly inside of an OLTP system.

#### Non-Blocking Analytics

- Asynchronous Snapshots.

- In-Memory Column Store.

- Query Decomposition.

#### **Transactions on Streams**

- ACID properties for streams.

- Open Questions:

- -Transaction boundaries?

- -Interaction of streams & tables?

H-Store

S-Store

**N-Store**

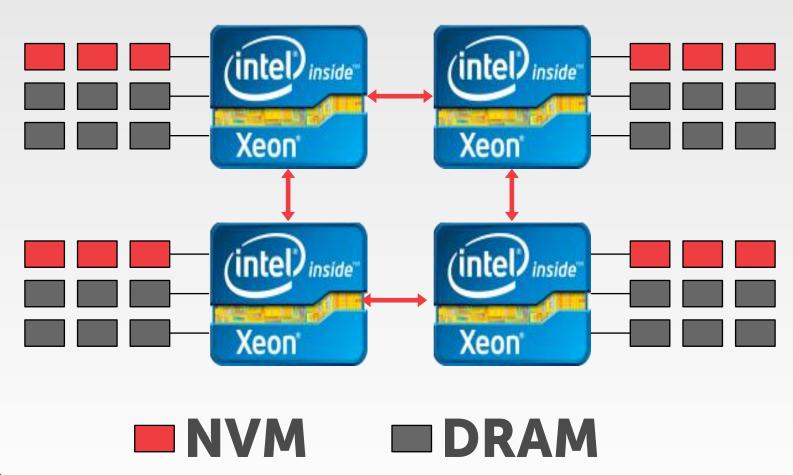

#### **N-Store**

- Transaction processing on non-volatile memory.

- -Memristors / ReRam

- -Phase Change Memory

- -Spintronics

#### Non-Volatile Memory

- NVM Emulator from Intel.

- Tunable Latencies.

- Accessed as a filesystem.

## 4 Socket Platform with 3 DIMMs/channel

#### Non-Volatile Memory

- Stage 1: H-Store + Anti-Cache

- Stage 2: H-Store + mmap()

- Stage 3: N-Store

# Escape From Planet Stonebraker

(i.e., Andy Needs to Get Tenure)

#### Beyond the 'Stores

- Non-Partitionable Workloads.

- The Poor Man's Spanner.

- Scientific Databases.

#### Conclusion

#### Carnegie Mellon University

Andy **Pavlo**

Justin **DeBrabant**

John **Meehan**

"The Thrill" **Stonebraker**

Stan **Zdonik**

Xiangyao **Yu**

George **Bezerra**

Sam **Madden**

Nesime **Tabul**

Ugur **Cetintemel**

Tim **Kraska**

Saman **Amarasinghe**