## CHAPTER 17

# Parallel Algorithms for Shared-Memory Machines

Richard M. KARP

*Department of Computer Science, University of California at Berkeley, Berkeley, CA 94720, USA*

Vijaya RAMACHANDRAN

*Department of Computer Sciences, University of Texas at Austin, Austin, TX 78712, USA*

### *Contents*

|                                                    |     |

|----------------------------------------------------|-----|

| 1. Introduction . . . . .                          | 871 |

| 2. Efficient PRAM algorithms . . . . .             | 873 |

| 3. Models of parallel computation . . . . .        | 894 |

| 4. NC-algorithms and P-complete problems . . . . . | 906 |

| 5. Conclusion . . . . .                            | 931 |

| Acknowledgment . . . . .                           | 932 |

| References . . . . .                               | 932 |

HANDBOOK OF THEORETICAL COMPUTER SCIENCE

Edited by J. van Leeuwen

© Elsevier Science Publishers B.V., 1990

## 1. Introduction

Parallel computation is rapidly becoming a dominant theme in all areas of computer science and its applications. It is likely that, within a decade, virtually all developments in computer architecture, systems programming, computer applications and the design of algorithms will be taking place within the context of parallel computation.

In preparation for this revolution, theoretical computer scientists have begun to develop a body of theory centered around parallel algorithms and parallel architectures. Since there is no consensus yet on the appropriate logical organization of a massively parallel computer, and since the speed of parallel algorithms is constrained as much by limits on interprocessor communication as it is by purely computational issues, it is not surprising that a variety of abstract models of parallel computation have been pursued.

Closest to the hardware level are the VLSI models, which focus on the technological limits of today's chips, in which gates and wires are packed into a small number of planar layers. At the next level of abstraction are those models in which a parallel computer is viewed as a set of processors interconnected in a fixed pattern, with each processor having a small number of neighbors.

At one further remove from physical reality is the parallel random-access machine (PRAM), in which it is assumed that, in addition to the private memories of the processors, there is a shared memory, and that any processor can access any cell of that memory in unit time. The PRAM cannot be considered a physically realizable model, since, as the number of processors and the size of the global memory scales up, it quickly becomes impossible to provide a constant-length data path from any processor to any memory cell. Nevertheless, the PRAM has proved to be an extremely useful vehicle for studying the logical structure of parallel computation in a context divorced from issues of parallel communication, and it is the focus of attention in the present survey. Algorithms developed for other, more realistic, models are often based on algorithms originally designed for the PRAM.

Many studies of algorithms and complexity in the PRAM model focus on the trade-off between the time for a parallel computation and the number of processors required. In a practical situation the number of processors available is fixed, but our theoretical studies are enriched if we let the number of processors grow as a function of the size of the problem instance being solved. Of particular interest are so-called *efficient* algorithms, which run in *polylog time* (i.e., the parallel computation time is bounded by a fixed power of the logarithm of the size of the input), and in which the processor-time product exceeds the number of steps in an optimal sequential algorithm by at most a polylog factor. Section 2 surveys efficient PRAM algorithms for bookkeeping operations such as compacting an array by squeezing out its "dead" elements, for evaluating algebraic expressions, for searching a graph and decomposing it into various kinds of components, and for sorting, merging and selection. These efficient parallel algorithms are typically completely different from the best sequential algorithms for the same problems, and their discovery has required the creation of a new set of paradigms for the construction of parallel algorithms.

In the PRAM model there is the possibility of read- and write-conflicts, in which two

or more processors try to read from or write into the same memory cell concurrently. Distinctions in the way these conflicts are handled lead to several different variants of the model. The weakest of these is the exclusive-read exclusive-write (EREW) PRAM, in which concurrent reading or writing are forbidden; of intermediate strength is the concurrent-read exclusive-write (CREW) PRAM, which allows concurrent reading but not concurrent writing; and strongest of all is the concurrent-read concurrent-write (CRCW) PRAM, which permits both kinds of concurrency. Several varieties of CRCW PRAMs have been defined; they differ in their method of resolving write conflicts. In Section 3 it is shown that, although these variants do not differ very greatly in computation speed, the CREW PRAM is strictly more powerful than the EREW PRAM and strictly less powerful than the CRCW PRAM. It is also shown that certain simple tasks, such as multiplying two  $n$ -bit numbers, inherently require time  $\Omega(\log n / \log \log n)$  even on the strongest PRAM model provided the number of processors is polynomial-bounded in the size of the input.

Section 3 goes on to study the relationship between the PRAM and other abstract models of parallel computation, such as Boolean circuits, alternating Turing machines and vector machines. It turns out that all these models are equivalent in their ability to solve problems in polylog time using a polynomial-bounded number of computing elements (processors or gates). This motivates the definition of NC as the class of problems that can be solved within these resource bounds by deterministic algorithms. Two important refinements of this result are presented, each showing that certain parallel computation models are equivalent in their ability to solve problems in time  $O(\log^k n)$ , where  $k$  is a fixed positive integer, using a polynomial-bounded amount of hardware. For PRAMs the amount of hardware is measured by the number of processors, for Boolean circuits by the number of wires and for alternating Turing machines by the number of possible configurations, which is exponential in the space. The first refinement, by Ruzzo [203], states that alternating Turing machines are equivalent to bounded fan-in circuits; the second, by Stockmeyer & Vishkin [220], states that CRCW PRAMs are equivalent to unbounded fan-in circuits.

Section 4 gives a survey of important problems that lie in the class NC. Among these are the basic arithmetic operations, transitive closure and Boolean matrix multiplication, the computation of the determinant, the rank or the inverse of a matrix, the evaluation of certain classes of straight-line programs, and the construction of a maximal independent set of vertices in a graph. Section 4 also presents randomized algorithms that operate in polylog time using a polynomial-bounded number of processors for problems such as finding a maximum matching in a graph.

The study of parallel complexity within the PRAM model has led to some important negative results. Using a theory of reducibility analogous to the theory of NP-completeness, it has been possible to identify certain problems as P-complete; such problems are solvable sequentially in polynomial time, but do not lie in the class NC unless every problem solvable in sequential polynomial time lies in NC. This is evidence that the P-complete problems are inherently resistant to ultrafast parallel solution. Our survey concludes, in Section 4, by exploring this concept and deriving a number of examples of P-complete problems, including the maximum-flow problem and the

problem of evaluating the output of a monotone Boolean circuit when all the inputs are fixed at constant values.

## 2. Efficient PRAM algorithms

### 2.1. The PRAM model and the concepts of efficient and optimal algorithms

The primary model of parallel computation that we will be working with is the PRAM (*Parallel Random-Access Machine*) (Fortune & Wyllie [85]; Goldschlager [106]; Savitch & Stimson [206]). This is an idealized model, and can be viewed as the parallel analogue of the sequential RAM (Cook & Reckhow [64]). A PRAM consists of several independent sequential processors, each with its own private memory, communicating with one another through a global memory. In one unit of time, each processor can read one global or local memory location, execute a single RAM operation, and write into one global or local memory location.

PRAMs can be classified according to restrictions on global memory access. An Exclusive-Read Exclusive-Write (or EREW) PRAM is a PRAM for which simultaneous access to any memory location by different processors is forbidden for both reading and writing. In a Concurrent-Read Exclusive-Write (or CREW) PRAM simultaneous reads are allowed but no simultaneous writes. A Concurrent-Read Concurrent-Write (or CRCW) PRAM allows simultaneous reads and writes. In this case we have to specify how to resolve write conflicts. Some commonly used methods of resolving write conflicts are

- (a) all processors writing into the same location must write the same value (the COMMON model);

- (b) any one processor participating in a common write may succeed, and the algorithm should work correctly regardless of which one succeeds (the ARBITRARY model);

- (c) there is a linear ordering on the processors, and the minimum numbered processor writes its value in a concurrent write (PRIORITY model).

Even though there is a variety of PRAM models, they do not differ very widely in their computational power. We show in Section 3 that any algorithm for a CRCW PRAM in the PRIORITY model can be simulated by an EREW PRAM with the same number of processors and with the parallel time increased by only a factor of  $O(\log P)$ , where  $P$  is the number of processors; further, any algorithm for a PRIORITY PRAM can be simulated by a COMMON PRAM with no loss in parallel time provided sufficiently many processors are available.

Define  $\text{polylog}(n) = \bigcup_{k > 0} O(\log^k n)$ . Let  $S$  be a problem whose fastest sequential algorithm runs in time proportional to  $T(n)$  (although, by Blum's Speed-up Theorem (cf. Seiferas [210]), there are pathological problems for which no fastest sequential algorithm exists, this phenomenon will not trouble us in practice). Many problems have the property that any algorithm that solves them would have to look at all of the input in the worst case, and hence  $T(n) = \Omega(n)$  in such cases. A PRAM algorithm  $A$  for  $S$ ,

running in parallel time  $t(n)$  with  $p(n)$  processors is *optimal* if

- (a)  $t(n) = \text{polylog}(n)$ ; and

- (b) the work  $w(n) = p(n) \cdot t(n)$  is  $O(T(n))$ .

An optimal parallel algorithm achieves a high degree of parallelism in an optimal way. Analogously, we can define an *efficient* parallel algorithm for problem  $S$  as one for which the work  $w(n)$  is  $T(n) \cdot \text{polylog}(n)$  with the parallel time  $t(n) = \text{polylog}(n)$ ; i.e., an efficient parallel algorithm is one that achieves a high degree of parallelism and comes within a polylog factor of optimal speed-up. A major goal in the design of parallel algorithms is to find optimal and efficient algorithms with  $t(n)$  as small as possible. Clearly it is easier to design optimal algorithms on a CRCW PRAM than on a CREW or EREW PRAM. However, the simulations between the various PRAM models make the notion of an *efficient* algorithm invariant with respect to the particular PRAM model used. Thus this latter notion is more robust.

Consider a computation that can be done in  $t$  parallel steps with  $x_i$  primitive operations at step  $i$ . If we implement this computation directly on a PRAM to run in  $t$  parallel steps, the number of processors required would be  $m = \max x_i$ . If we have  $p < m$  processors, we can still simulate this computation effectively by observing that the  $i$ th step can be simulated in time  $\lceil x_i/p \rceil \leq (x_i/p) + 1$ , and hence the total parallel time to simulate the computation with  $p$  processors is no more than  $\lceil x/p \rceil + t$  where  $x = \sum_i x_i$ . This observation, known as *Brent's scheduling principle* (Brent [42]), is often used in the design of efficient parallel algorithms. It should be noted that this simulation assumes that *processor allocation* is not a problem, i.e., that it is possible for each of the  $p$  processors to determine, on-line, the steps it needs to stimulate. We will see below that this is sometimes a nontrivial task.

Brent's scheduling principle implies that, when processor allocation is not a problem, a parallel algorithm requiring work  $w(n)$  and time  $t(n)$  can be simulated using  $p$  processors in time  $w(n)/p + t(n)$ . In practice,  $p$  is often small compared to  $n$ , and in such cases the ratio  $w(n)/p$  is typically much greater than  $t(n)$ . In view of this fact, Kruskal, Rudolph & Snir [245] suggest that it may be unnecessarily restrictive to concentrate on parallel algorithms with  $t(n) = \text{polylog}(n)$ , and they emphasize instead the concept of polynomial speed-up. For a problem requiring sequential time  $T(n)$ , a parallel algorithm running in time  $t(n)$  is said to have *polynomial speed-up* if, for some  $\varepsilon < 1$ ,  $t(n) = O(T(n^\varepsilon))$ . Algorithms with polynomial speed-up are further classified according to their *inefficiency*. For a problem whose best sequential algorithm runs in time  $T(n)$ , a parallel algorithm that performs an amount of work  $w(n)$  is said to have *constant inefficiency* if  $w(n) = O(T(n))$ , *polylog inefficiency* if

$$w(n) = O(T(n) \text{ polylog}(T(n)))$$

and *polynomial inefficiency* if  $w(n)$  is bounded by a polynomial in  $T(n)$ . Kruskal, Rudolph & Snir argue that algorithms with polynomial speed-up and constant or polylog inefficiency may be extremely useful, even if they do not run in polylog time.

For PRAM algorithms we would like to have simple algorithms that are easy to specify and code. Most of the algorithms we describe will have this feature.

There are a few key methods that have emerged as fundamental subroutines in the

design of efficient and optimal parallel algorithms. In the following subsections, we review these basic techniques and algorithms.

## 2.2. Basic PRAM techniques

### 2.2.1. Prefix sums

The first problem we consider is *prefix sums*. Let  $*$  be an associative operation over a domain  $D$ . Given an array  $[x_1, \dots, x_n]$  of  $n$  elements from  $D$ , the prefix sums problem is to compute the  $n$  prefix sums  $S_i = x_1 * x_2 * \dots * x_i = \sum_{j=1}^i x_j$ ,  $i = 1, \dots, n$ . This problem has several applications. For example, consider the problem of compacting a sparse array: given an array of  $n$  elements, many of which are zero, we wish to generate a new array containing the non-zero elements in their original order. We can compute the position of each non-zero element in the new array by assigning value 1 to the non-zero elements, and computing prefix sums with  $*$  operating as regular addition. An application to the problem of adding two  $n$ -bit numbers is given in Section 4.2. Further, recognition of any regular language whose input size is restricted to  $n$  can be viewed as a prefix sums problem [150].

There is a simple sequential algorithm to solve the prefix sums problem using  $n-1$  operations, by computing  $S_i$  incrementally from  $S_{i-1}$ , for  $i = 2, \dots, n$ . Unfortunately this algorithm has no parallelism in it since one of the two operands for the  $i$ th  $*$  operation is the result of the  $(i-1)$ st operation.

We now describe a simple parallel algorithm to compute prefix sums in parallel (Ladner & Fischer [150]). For simplicity we assume that  $n$  is a power of 2.

#### PARALLEL PREFIX ALGORITHM

*Input:* an array  $[x_1, \dots, x_n]$  of elements from domain  $D$ .

**if**  $n = 1$  **then**  $S_1 := x_1$  **else**

(1) **for**  $i = 1, \dots, n/2$  **compute**  $y_1 := x_{2i-1} * x_{2i}$

(2) **recursively compute** prefix sums  $S_i$ ,  $i = 1, \dots, n/2$ , **for** the new array

$[y_1, \dots, y_{n/2}]$

(3) **for even**  $i$  in  $\{1, 2, \dots, n\}$  **set**  $S_i := S_{i/2}$

(4) **for odd**  $i$  in  $\{1, 2, \dots, n\}$  **set**  $S_i := S_{(i-1)/2} * x_i$ .

This algorithm runs on an EREW PRAM since there are no conflicts in the memory accesses. The parallel time  $t(n)$  satisfies the recurrence  $t(n) = t(n/2) + O(1)$  with  $t(1) = 0$ , and the work satisfies the recurrence  $w(n) = w(n/2) + O(n)$  with  $w(1) = 0$ . Thus  $t(n) = O(\log n)$  and  $w(n) = O(n)$ . By invoking Brent's scheduling principle we see that this is an optimal EREW PRAM algorithm for  $p(n) = O(n/\log n)$ . Processor allocation is straightforward in this case and we illustrate it by a standard technique used to implement Brent's principle: Let the number of processors available be  $p \leq n/\log n$ , and let  $q = \lceil n/p \rceil$ . We first assign the  $i$ th processor to elements  $x_{(i-1) \cdot q + 1}, x_{(i-1) \cdot q + 2}, \dots, x_{i \cdot q}$ ,  $i = 1, \dots, p$ . The  $i$ th processor stores these values in an array in its local memory, combines these  $q$  values (sequentially) using  $*$  in  $O(q)$  time and places the result in  $y_i$ . Now the array has only  $p$  elements in it, and the parallel prefix algorithm is

used to compute these prefix sums in  $O(\log n)$  time using  $p$  processors. Finally, in additional  $O(n/p)$  time, the  $i$ th processor computes the prefix sums for its local array with  $S_{i-1}$  as the first element of the array. This algorithm runs in  $O(n/p)$  time with  $p$  processors on an EREW PRAM for  $p \leq n/\log n$ .

On a CRCW PRAM, the above algorithm can be modified to run optimally in  $O(\log n/\log \log n)$  time when the  $x_i$  are  $O(\log n)$ -bit numbers and  $*$  is ordinary addition (Reif [196]; Cole & Vishkin [56]).

Since the prefix sums problem is an important one, much attention has been given to fine-tuning the constants in the time and processor bounds (see, e.g., [150, 80]).

### 2.2.2. List ranking

A problem closely related to the prefix sums problem is the *list ranking problem*: Given a linked list of  $n$  elements, compute the suffix sums of the last  $i$  elements of the list,  $i = 1, \dots, n$ . This is a variant of prefix sums, in which the ordered sequence of elements is given in the form of a linked list rather than an array, and the sums are computed from the end, rather than from the beginning. The term “list ranking” is usually applied to the special case of this problem in which all elements have value 1, and  $*$  stands for addition (and hence the result of the list ranking computation is to obtain, for each element, the number of elements ahead of it in the list, i.e., its rank in the list); however, the technique we shall present easily adapts to our generalization.

We assume that the linked list is represented by a contents array  $c[1, \dots, n]$  and a successor array  $s[1, \dots, n]$ : here,  $c(i)$  gives the value of the element at location  $i$ , and  $s(i)$  gives the location  $j$  of the successor to  $c(i)$  on the list. Without loss of generality we assume that our domain has a zero element  $z$ , that the last element on the list  $c(i_l)$  has value  $z$ , and that  $s(i_l) = i_l$ . The following simple algorithm solves the list ranking problem on an EREW PRAM in  $O(\log n)$  time with  $n$  processors (see, e.g., [242]).

#### BASIC LIST RANKING ALGORITHM

```

for  $\lceil \log n \rceil$  iterations repeat

in parallel for  $i = 1, \dots, n$  do

$c(i) := c(i)*c(s(i));$

$s(i) := s(s(i));$

for  $i = 1, 2, \dots, n$  output  $c(i)$  as the rank of element  $i$ .

```

The operation used in this algorithm of replacing each pointer  $s(i)$  by the pointer’s pointer  $s(s(i))$  is called *pointer jumping*, and is a fundamental technique in parallel algorithm design. Let the *rank*  $r(i)$  of the element in location  $i$  be the distance of this element from the end of the input linked list. The correctness of this algorithm follows from the observation that at the start of each step,  $c(i)$  equals the sum of elements in the input list with ranks  $r(i), r(i)-1, \dots, r(s(i))+1$  for the current  $s(i)$ ; and after  $\lceil \log n \rceil$  iterations,  $s(i) = i_l$  for all  $i$ . By assigning a processor to each location  $i$ , we obtain an  $n$ -processor  $O(\log n)$  time parallel algorithm. Observe, however, that the work done by this algorithm is  $\Theta(n \log n)$  and hence this algorithm as it stands does not lead to an optimal parallel algorithm (since there is a simple linear-time sequential algorithm for the list ranking problem).

The list ranking problem is similar to the prefix sums problem, which has a simple optimal parallel algorithm. The optimal parallel prefix algorithm reduces the problem of computing prefix sums on  $n$  elements to one of computing prefix sums on the  $n/2$  elements at even positions on the array. This reduction is done in constant time and is data-independent in the sense that the locations of the  $n/2$  elements in the reduction list are predetermined. If we try to implement a list ranking algorithm with this property, we run into the problem that a given element has no way of knowing whether it is at an odd or even position on the list. Except for the beginning and end elements, there is no way to determine this information from the local environment of an element.

In order to overcome this problem, we note that we need not necessarily locate the elements at even positions. It suffices to construct a set  $S$  of no more than  $c \cdot n$  elements in the list, with  $c < 1$ , such that the distance in the list between any two consecutive elements of  $S$  is small. The list ranking problem can then be solved as follows:

- (i) *List contraction*: Create a contracted list composed of the elements of  $S$ , in which each element of  $S$  has as its successor the first element of  $S$  that follows it in the original list, and a value equal to its own value in the original list, plus the sum of the values of the elements that lie between it and this successor;

- (ii) Recursively, solve the list ranking problem for the contracted list. The suffix sum for each element in the contracted list is the same as its suffix sum in the original list;

- (iii) Extend this solution to all elements of the original list. The time to do this is proportional to the maximum distance between two elements of  $S$  in the original list, and the work is proportional to the length of the original list.

We shall present an optimal  $O(\log n)$  time randomized list ranking algorithm that takes this approach, but with the following exception: once a contracted list of length less than  $n/\log n$  is obtained, list contraction is no longer used; instead, the list ranking problem for this contracted list is solved using the Basic List Ranking Algorithm. This requires time  $O(\log n)$  using  $n/\log n$  processors.

It is necessary to specify how the list contraction step is carried out. This entails giving a method for choosing the set  $S$ , and a method for the compaction process needed to place the elements of  $S$  in consecutive locations, in preparation for the recursive solution of the list ranking problem on the compacted list.

We can construct  $S$  by the following simple randomized algorithm (see e.g., Vishkin [235]; Miller & Reif [171]) called the *random mate algorithm*. Each element chooses a gender, female or male, with equal probability. An element is in set  $S$  if and only if it is female or has a male predecessor. It is easy to see that, with probability  $1 - o(1)$ , the size of  $S$  is not more than  $15n/16$ , and each element in  $S$  can find its successor in  $S$  in constant time, since the distance to its successor is at most 2. With random mating each list contraction tends to shrink the length of the list by a constant factor, and thus the number of contractions needed to pass from the original list of length  $n$  to a list of length less than  $n/\log n$  is  $O(\log \log n)$ .

The process of compacting  $S$  into consecutive locations could be done by the  $O(\log n)$  time optimal method for prefix sums that we saw earlier, but this method would lead to a list ranking algorithm, running in time  $O(\log n \log \log n)$ , since  $\log \log n$  list contractions need to be performed. Instead, we can use either an optimal  $O(\log \log n)$  time randomized algorithm on an ARBITRARY CRCW PRAM that approximately

compacts an array (Miller & Reif [171]), or the optimal  $O(\log n / \log \log n)$  time deterministic prefix sums algorithm of Cole & Vishkin [56], which runs on a COMMON PRAM. Either of these leads to a method that, with high probability, solves the list ranking problem in time  $O(\log n)$  and work  $O(n)$ . Thus, using Brent's scheduling principle, one obtains an optimal  $O(\log n)$  time randomized list ranking algorithm using  $n / \log n$  processors.

In order to obtain an optimal  $O(\log n)$  time deterministic list ranking algorithm it is necessary to replace the random mating procedure by a deterministic method of isolating a contracted set of elements  $S$ . A symmetry breaking technique known as *deterministic coin tossing* can be used for this purpose (Cole & Vishkin [55]). The technique is based on the concept of an *r-ruling set* [55]. Given an  $n$ -element list, a subset  $S$  of these elements is an *r-ruling set* if  $S$  contains no two adjacent elements of the list, and every element not in  $S$  is at a distance no more than  $c \cdot r$  on the list from an element in  $S$ , where  $c$  is a suitable constant.

Define  $\log^{(k)} n$  to be the log function iterated  $k$  times, and let  $r = \log^{(k)} n$ . The following algorithm finds an *r-ruling set* in an  $n$ -element linked list in  $O(k)$  time using  $n$  processors [55] (see also Goldberg, Plotkin & Shannon [102]). We assume that the linked list is doubly linked with successor pointer  $s(i)$  and predecessor pointer  $p(i)$ .

#### RULING SET ALGORITHM

*Input:*  $n$ -element linked list with successor pointers  $s(i)$  and predecessor pointers  $p(i)$ ; integer  $k$  to set  $r = \log^{(k)} n$ .

(1) **for**  $i = 1, \dots, n$  initialize  $c(i) := i$ .

(2) **for**  $k$  iterations **do**

**in parallel for** each  $i$  **do**

determine the rightmost bit position  $q$  such that the  $q$ th bit of  $c(i)$  differs from the  $q$ th bit of  $c(s(i))$ ; let  $b$  be the  $q$ th bit of  $c(i)$ ;  $c(i) := b$  concatenated with the binary representation of  $q$ ;

(3) **in parallel for** each  $i$  **do**

**if**  $c(p(i)) \leq c(i)$  **and**  $c(s(i)) \leq c(i)$  **then** assign  $i$  to the ruling set.

It is straightforward to verify that in this algorithm  $c(i) \neq c(s(i))$  at every iteration. Further, the maximum value of any  $c(i)$  at the end of the  $j$ th iteration is  $B_j = O(\log^{(j)} n)$ . Finally, the distance between two local maxima at the end of the  $j$ th iteration is no more than  $2 \cdot B_j$ , and hence at the end of the algorithm, any element on the list is within distance  $O(\log^{(k)} n)$  of an element in the ruling set.

Two special cases of the ruling set algorithm deserve special attention. When  $k = c$ , a constant, the algorithm obtains an  $O(\log^{(k)} n)$  ruling set in constant time using  $n$  processors. Define  $\log^* n$  as the minimum value of  $k$  such that  $\log^{(k)} n \leq 3$ ;  $\log^* n$  is a very slowly growing function of  $n$ . Using the ruling set algorithm we can obtain an  $O(1)$  ruling set in  $O(\log^* n)$  time with  $n$  processors. Since no two elements in a ruling set are adjacent, the size of any *r-ruling set* is at most one more than half the number of elements in the list. In additional  $O(r)$  time, each element in the ruling set can locate its successor in the ruling set by following the successor pointers in the linked list, thus forming a contracted list.

The ruling set algorithm with appropriately chosen values of  $k$  has been used in rather elaborate procedures to obtain optimal  $O(\log n)$  deterministic EREW PRAM algorithms for list ranking (Cole & Vishkin [58]; Anderson & Miller [12]).

### 2.2.3. Tree contraction

There are several applications that require computation on a rooted tree. One such problem is the *expression evaluation problem*: Given a parenthesized arithmetic expression (using  $+$  and  $\cdot$  operations) with values assigned to the variables, evaluate  $E$  and all subexpressions of  $E$ . Note that the prefix sums problem is the expression evaluation problem on the parenthesized expression  $(\dots (x_1 + x_2) + x_3 \dots) + x_n$ .

Associated with a parenthesized expression is a binary tree with  $n$  leaves that specifies the parenthesization. As in the prefix sums problem there is a simple linear-time sequential algorithm for the expression evaluation problem: compute the values on the internal nodes of the expression tree from the leaves upward to the root. The value at the root gives the value of the expression, and the value at each internal node is the value of the subexpression rooted at that node. However, if the tree is highly imbalanced, i.e., its height is large in relation to its size, then this method performs poorly in parallel.

*Tree contraction* is a method of evaluating expression trees efficiently in parallel. The method transforms the input tree in stages using local operations in such a way that an  $n$ -node tree is contracted into a single node in  $O(\log n)$  stages, each of which takes constant time on a PRAM. An efficient method for tree contraction was first introduced by Miller & Reif [171]. There are several optimal tree contraction algorithms that run in  $O(\log n)$  time on EREW PRAM (Gibbons & Rytter [98]; Cole & Vishkin [57]; Abrahamson, Dadoun, Kirkpatrick & Przytycka [1]; Kosaraju & Delcher [145]; Gazit, Miller & Teng [97]). We describe the method reported independently in [1] and [145].

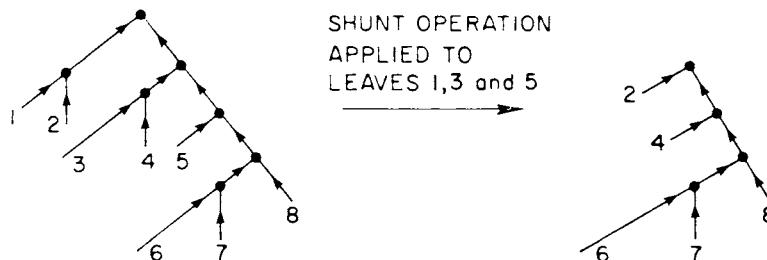

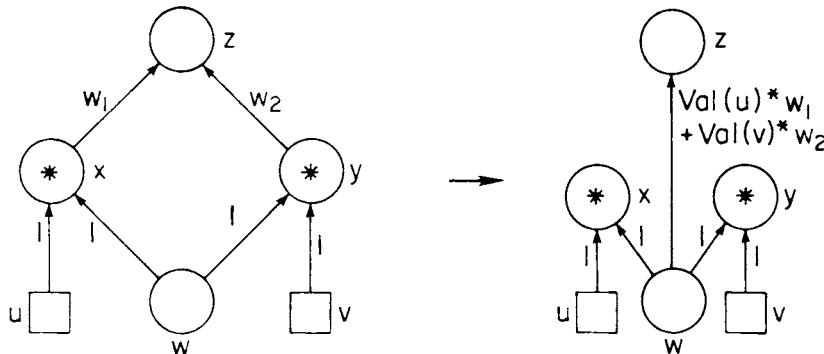

The tree contraction algorithm works on a rooted, ordered binary tree, i.e., a rooted ordered tree in which every vertex is either a *leaf*, having no children, or an *internal node*, having exactly two children, and each arc points from a child to its parent. Let  $l$  be a leaf in an  $n$ -leaf binary tree  $T$ . The SHUNT operation applied to  $l$  results in a contracted tree  $T'$  in which  $l$  and  $p(l)$ , the parent of  $l$  in  $T$ , are deleted, and the other child  $l'$  of  $p(l)$  has the parent of  $p(l)$  as its parent, while leaving the relative ordering of the remaining leaves unchanged (see Fig. 1).

We now describe the tree contraction algorithm.

Fig. 1. The SHUNT operation.

## TREE CONTRACTION ALGORITHM

*Input:* a rooted, ordered, binary  $n$ -leaf tree  $T$ .

- (1) *Preprocess:* label the leaves in order from left to right as  $1, \dots, n$ .

- (2) **for**  $\lceil \log n \rceil$  iterations **do**

- (a) apply SHUNT in parallel to all odd numbered leaves that are the left child of their parent;

- (b) apply SHUNT in parallel to all odd numbered leaves that are the right child of their parent;

- (c) shift out the rightmost bit in the labels of all remaining leaves.

It is straightforward to see that the operations in this algorithm can be implemented on an EREW PRAM. After each iteration, half of the leaves are deleted from the current tree, and no new leaves are created. Hence after  $\lceil \log n \rceil$  iterations, the tree is contracted to a single node.

Step 1 can be implemented optimally in  $O(\log n)$  time on an EREW PRAM using the *Euler tour technique* (Tarjan & Vishkin [221]), which we describe in Section 2.3. Then, in constant time, the leaves can be placed in an array  $A$  in the order in which they will be processed. The total work done in step 2 is

$$O\left(\sum_{i=1}^{\lceil \log n \rceil} n/2^i\right) = O(n)$$

and processor allocation is no problem since we have the array  $A$ . Thus this gives an optimal  $O(\log n)$  tree contraction algorithm on an EREW PRAM.

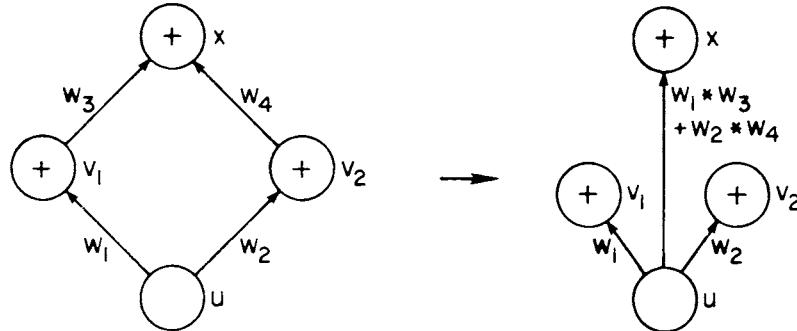

By associating appropriate computations with the SHUNT operation, we can evaluate an arithmetic expression while performing tree contraction on its associated tree. We associate with each arch  $(u, v)$  an ordered pair of values  $(a, b)$  with the interpretation that if the value of  $u$  is  $x$ , then the operand supplied to  $v$  along arc  $(u, v)$  is  $a \cdot x + b$ . Initially, every arc has the ordered pair  $(1, 0)$ . Thus, initially, the value of each node in the tree is exactly the value of its subexpression.

Now consider a SHUNT operation on a leaf  $l$  with parent  $p$ , sibling  $s$  and grandparent  $q$ . Let the value of leaf  $l$  be  $v$ , and let arc  $(l, p)$  have value  $(a_1, b_1)$ , arc  $(s, p)$  have value  $(a_2, b_2)$  and arc  $(p, q)$  have value  $(a_3, b_3)$ . In the contracted tree, all three of these arcs are deleted and replaced by the arc  $(s, q)$ . Let  $a$  and  $b$  be constants such that

$$a \cdot y + b = a_3 \cdot ((a_1 \cdot v + b_1) * (a_2 \cdot y + b_2)) + b_3,$$

where  $*$  represents the operation at  $p$  and  $y$  is an indeterminate. Then it is easy to see that assigning the value  $(a, b)$  to the newly introduced arc  $(s, q)$  leaves the values of the vertices remaining in the new tree unaltered. Thus we obtain an optimal  $O(\log n)$  time EREW PRAM algorithm for expression evaluation. All subexpressions in the expression tree can be evaluated within the same bounds by having an expansion phase at the end, similar to that in the parallel prefix algorithm. This technique works for the evaluation of expressions over a semiring, ring or field (in the case of a field, the value on each edge is an ordered set of four values, to represent the ratio of two linear forms). If the input is in the form of a parenthesized expression, the tree form can be extracted from it optimally in  $O(\log n)$  time using an algorithm by Bar-On & Vishkin [24].

In addition to expression evaluation, tree contraction has been applied to a wide variety of problems. The technique easily generalizes to arbitrary (nonbinary) trees, and has been used to derive parallel algorithms for various graph-theoretic computations on trees such as maximum matching, minimum vertex cover and maximum independent set [115]. Other applications of tree contraction and its variants can be found in [101, 171, 189]. A generalization of the SHUNT operation is used in the more general problem of straight-line program evaluation, or evaluation of a DAG (see Section 4); in fact, the SHUNT operation was first introduced in this more general setting [170].

#### 2.2.4. Conclusion

We have described optimal parallel algorithms for three basic problems: prefix sums, list ranking and expression evaluation.

In Section 3 we show that it requires  $\Omega(\log n)$  time to compute the OR of  $n$  bits on a CREW PRAM, regardless of the number of processors available. Since the three problems we considered in this section are at least as difficult as the OR function, the lower bound applies for these problems as well. Thus the results we have given are optimal with maximum possible speed-up.

A lower bound of  $\Omega(\log n/\log \log n)$  time holds for computing the parity of  $n$  bits on a PRIORITY CRCW PRAM with a polynomial number of processors (Beame & Hastad [29]). Since we could solve the parity problem if we could solve an arbitrary prefix sums, list ranking or tree contraction problem, this lower bound applies to these problems as well. While an optimal  $O(\log n/\log \log n)$  time CRCW PRAM algorithm is known for the prefix sums problem under certain conditions, it is not known if the list ranking and tree contraction problems have sublogarithmic time algorithms on a CRCW PRAM with a polynomial number of processors.

### 2.3. Efficient graph algorithms

Graphs play an important role in modeling real-world problems, and sequential algorithms for graph problems have been studied extensively. Almost without exception, all of the optimal (i.e., linear-time) sequential algorithms for these problems use one of two methods to search a graph: *depth-first search* or *breadth-first search*. At present, neither of these techniques has an efficient parallel algorithm. The best polylog-time PRAM algorithm known for breadth-first search of an  $n$ -node graph uses  $M(n)$  processors, where  $M(n)$  is the number of processors required to multiply two  $n \times n$  matrices over a general ring in  $O(\log n)$  time. The best upper bound presently known for  $M(n)$  is  $O(n^{2.376})$  (Coppersmith & Winograd [66]). For depth-first search there is currently no deterministic polylog-time parallel algorithm known that uses a polynomial number of processors. For more on parallel breadth-first search and depth-first search, see Section 4.

The early work on parallel graph algorithms [48, 76, 192, 205, 221, 224] used various methods to circumvent the lack of an efficient parallel method of searching a graph. More recently, a new efficient graph searching technique called *ear decomposition* [241, 156, 168, 162] has been developed for undirected graphs. Using this technique, efficient

parallel algorithms for several graph problems including strong orientation, biconnectivity, triconnectivity, four-connectivity, and  $s-t$  numbering have been developed. Several of these algorithms also have optimal sequential implementations, thus giving us new algorithms for the sequential case. This is an example of a new emerging discipline enriching an existing one. We briefly survey the results in the following, where we assume that the input graph  $G$  has  $n$  vertices and  $m$  edges.

### 2.3.1. Connected components

The problem of computing connected components is often considered the most basic graph problem. While it is not known how to apply depth-first search or breadth-first search to obtain an efficient parallel connected-components algorithm, the following approach (Hirschberg, Chandra & Sarwate [118]) does give an efficient parallel algorithm for the problem. The algorithm works in  $O(\log n)$  stages. At each stage, the vertices of  $G$  are organized in a forest of directed trees, with a directed arc from each vertex to its parent in the tree. All vertices in any given tree in the forest are known to be in the same connected component of  $G$ . In the first stage of the algorithm, each vertex is in a tree by itself, and at the end of the last stage, all vertices in a connected component are in a tree of height 1. In going from stage  $i$  to stage  $i + 1$ , some of the trees containing adjacent vertices in  $G$  are linked by a *hooking* process and then the heights of the resulting new trees are compressed by pointer jumping, i.e., each vertex that is not a root or a child of a root in the new tree chooses the parent of its parent to be its new parent. The hooking process has to be implemented properly in order to maintain the tree structure and to guarantee termination of the algorithm in  $O(\log n)$  stages. Various implementations of the above basic idea for the CREW PRAM [118], EREW PRAM (Nath & Maheshwari [176]) and CRCW PRAM (Awerbuch & Shiloach [21]; Shiloach & Vishkin [212]) are available. The implementation bound is  $O(\log n)$  time using  $O(m + n)$  processors on an ARBITRARY CRCW PRAM (recall that by the simulations between the PRAMs, this implies an  $O(\log^2 n)$  time algorithm using  $O(m + n)$  processors on an EREW PRAM). This algorithm is easily extended to obtain a spanning tree for  $G$  with the same time and processor bounds.

By applying more elaborate techniques based on those for optimal list ranking to the basic algorithm we have outlined, the connected components of a graph can be determined on an ARBITRARY CRCW PRAM in  $O(\log n)$  time with

$$O((m + n)\alpha(m, n)/\log n)$$

processors (Cole & Vishkin [56]), where  $\alpha(m, n)$  is the inverse Ackermann function, which is an extremely slowly growing function of  $m$  and  $n$ . There is also a randomized optimal  $O(\log n)$  algorithm for finding connected components on an ARBITRARY CRCW PRAM (Gazit [94]).

### 2.3.2. Euler tour technique

The starting point for most other graph algorithms is the construction of a rooted spanning tree  $T$ , and the computation of simple tree functions such as pre- and postorder numbering of vertices in the tree, the level and height of each vertex in the tree, and the number of descendants of each vertex in the tree. For this, we can use the

*Euler tour technique on trees* (Tarjan & Vishkin [221]), which we describe below. This method works by reducing the computation of these tree functions to list ranking.

Given an unrooted tree  $T$  we can convert it into an Eulerian directed graph  $D$  by replacing each edge  $\{u, v\}$  by two directed arcs, one from  $u$  to  $v$  and the other from  $v$  to  $u$ . Let  $E = \langle e_1, e_2, \dots \rangle$  be an Euler tour of  $D$ , with  $e_1$  being the directed arc from  $u$  to  $v$ . Then it is easy to see that  $E$  represents a depth-first search traversal of  $T$  with  $u$  as the root. Each undirected edge  $\{x, y\}$  appears once on the list as the directed arc  $(x, y)$ , and once as the directed arc  $(y, x)$ . If  $(x, y)$  appears before  $(y, x)$  in  $E$ , then  $x$  is the parent of  $y$  in  $T$  rooted at  $u$ , since in this case,  $(x, y)$  represents the forward traversal of the edge in the depth-first search and  $(y, x)$  represents the backtracking along the edge in the depth-first search. Thus parent-child relationships in  $T$  rooted at  $u$  can be determined once we have ranked the elements in list  $E$ .

Given a tree  $T$ , finding an Euler tour  $E$  for its directed Eulerian version is very simple. We assume that the tree is specified by an adjacency list for each vertex, which can be interpreted as a list of outgoing arcs from that vertex. This automatically gives us two arcs directed in opposite directions for each edge. We assume that there is a pointer from each edge to its reversal. With this representation we can obtain an Euler tour  $E$  in constant time with  $n$  processors by specifying, for each edge  $e$ , its next edge on  $E$  as the edge next to  $\bar{e}$ , the reversal of  $e$ , in the adjacency list containing  $\bar{e}$  (if  $\bar{e}$  is the last edge on its adjacency list, its next edge is the first edge on this list). To obtain a depth-first search from a given root  $u$ , we simply pick any arc  $(u, v)$  as the starting arc of the tour. Now we can use list ranking to determine the position of each arc in  $E$ , and hence the parent-child relation. Other tree functions such as preorder number, level, and number of descendants of each vertex can be determined by list ranking using appropriate initial weights. For instance, to compute preorder numbers, we can assign a weight of 1 to forward arcs and a weight of 0 to back arcs. Then, for each forward arc  $(u, v)$ , the preorder number of  $v$  is  $n - 1 -$  (the weighted rank of  $(u, v)$  in the list). The optimal list ranking algorithm implies optimal  $O(\log n)$  time EREW PRAM algorithms for these problems.

We can also use the Euler tour technique on trees to implement the preprocessing step in the Tree Contraction Algorithm of the previous section optimally. For this we merely need to give a weight of 1 to leaves and a weight of 0 to internal nodes, and then compute the weighted rank of each leaf in the Euler tour.

The Euler tour technique on trees generalizes to finding Euler tours in general Eulerian graphs with the same complexity bounds as the connected-components algorithm (Atallah & Vishkin [18]; Awerbuch, Israeli & Shiloach [20]). For this, we construct the tour  $E$  as above by specifying for each edge, the edge that follows it in  $E$ . For a general Eulerian graph, this results in a collection of edge disjoint (possibly nonsimple) cycles. Two cycles having a common vertex  $u$  can be “stitched together” by swapping the successor edges of the two incoming arcs to  $u$  in the Euler tour  $E$ . The algorithm obtains an Euler tour for the graph by stitching all the cycles together into a single connected structure through an appropriate choice of such swaps.

### 2.3.3. Ear decomposition

An *ear decomposition*  $D = [P_0, \dots, P_{r-1}]$  of an undirected graph  $G = (V, E)$  is a partition of  $E$  into an ordered collection of edge-disjoint simple paths  $P_0, \dots, P_{r-1}$

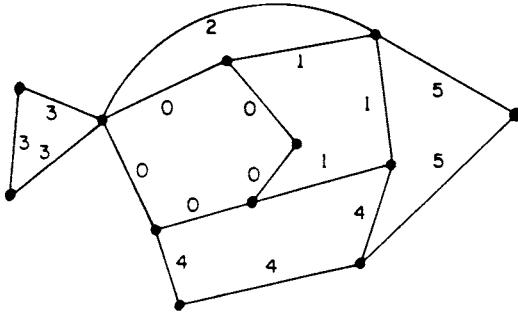

Fig. 2. An ear decomposition.

called *ears*, such that  $P_0$  is a simple cycle, and for  $i > 0$ ,  $P_i$  is a simple path (possibly a simple cycle) with each endpoint belonging to a lower-numbered ear, and with no internal vertices belonging to lower-numbered ears (see Fig. 2). An ear with no internal vertex is called a *trivial ear*.

An *open ear decomposition* is an ear decomposition in which none of the  $P_i, i > 0$ , is a simple cycle.

It is known that a graph has an ear decomposition if and only if it is 2-edge connected and a graph has an open ear decomposition if and only if it is biconnected, i.e., 2-vertex connected (Whitney [241]).

Let  $T$  be a spanning tree of an undirected, 2-edge connected graph  $G = (V, E)$ , and let  $N$  be the set of non-tree edges in  $G$ , i.e., the edges in  $G - T$ . Then each edge  $e$  in  $N$  completes exactly one cycle in  $T \cup \{e\}$ , called a *fundamental cycle of  $G$  with respect to  $T$* . It is easy to see that the number of ears in any ear decomposition or open ear decomposition of an  $n$ -vertex,  $m$ -edge graph is  $m - n + 1$ , which is also the number of fundamental cycles in the graph. In the ear decomposition algorithm presented below (Maon, Schieber & Vishkin [162]; Miller & Ramachandran [168]), each ear is generated as part of a fundamental cycle of  $G$  with respect to  $T$ , and contains the non-tree edge in that fundamental cycle.

#### EAR DECOMPOSITION ALGORITHM

*Input:* Undirected, 2-edge connected graph  $G = (V, E)$ .

- (1) *Preprocess  $G$ :*

- (a) Find a spanning tree  $T$  for  $G$ ;

- (b) Root  $T$  and number the vertices in preorder;

- (c) label each non-tree edge by the least common ancestor (lca) of its endpoints in  $T$ .

- (2) *Assign ear numbers to non-tree edges:* number non-tree edges from 0 to  $r - 1$  in nondecreasing order of their lca labels.

- (3) *Assign ear numbers to tree edges:* number each tree edge with the number of the minimum-numbered non-tree edge whose fundamental cycle it belongs to.

The correctness of this algorithm follows from a straightforward induction on ear number. It is easy to see that the edges with ear number 0 form a simple cycle passing

through the root of  $T$ , and if we assume inductively that edges with ear numbers 0 to  $i$  satisfy the definition of an ear decomposition, it is not difficult to show that the edges with ear number  $i+1$  have the desired properties as well.

All of the steps in the algorithm can be implemented using the Euler tour algorithm, together with efficient parallel algorithms for finding a spanning tree, sorting, prefix sums, and finding lca's. The algorithm runs in  $O(\log n)$  time while performing  $O(m+n \log n)$  work. If consecutive ear numbers are not required, but only distinct labels from a totally ordered set, then the parallel sorting algorithm is not required and the algorithm can be implemented to run in  $O(\log n)$  time while performing the same amount of work as the connected-components algorithm, i.e.,  $O((m+n)\alpha(m,n))$  work, by using an optimal  $O(\log n)$  time parallel algorithm to find lca's (Schieber & Vishkin [207]). A randomized version of the ear decomposition algorithm with consecutive ear numbers runs in  $O(\log n)$  time while performing  $O(m+n)$  work, by using optimal  $O(\log n)$  time randomized parallel algorithms for connectivity (Gazit [94]) and for sorting integers in the range 1 to  $n$  (Reif [196]).

The ear decomposition algorithm, in general, does not give an open ear decomposition, but can be modified to do so (Maon, Schieber & Vishkin [162]; Miller & Ramachandran [168]) with the same parallel complexity by refining the numbering in step 2 so that non-tree edges with the same lca labels are further ordered in such a way that the resulting ear numbers give an open ear decomposition.

### 2.3.4. Applications of ear decomposition

The efficient parallel ear decomposition algorithm implies efficient parallel algorithms for 2-edge connectivity and biconnectivity. Other efficient parallel algorithms for biconnectivity are known [48, 221].

We describe two other applications of ear decomposition. A *strong orientation* of an undirected graph  $G=(V, E)$  is an assignment of a direction to each edge of  $G$  such that the resulting directed graph is strongly connected. A graph has a strong orientation if and only if it is 2-edge connected. To strongly orient a 2-edge connected graph, we find an ear decomposition for it, and then orient the edges in each ear from one (arbitrary) endpoint of the ear to the other. Parallel algorithms for strong orientation are reported in [13, 236].

We now briefly describe how to use open ear decomposition to obtain an efficient parallel algorithm to test triconnectivity, and to find the triconnected components of a biconnected graph (Miller & Ramachandran [169]). Let  $D=[P_0, \dots, P_{r-1}]$  be an open ear decomposition of a biconnected graph  $G=(V, E)$ . If  $G$  is not triconnected, then it contains a pair of vertices  $x, y$  whose removal separates the graph into two or more pieces. For such a pair of vertices  $x, y$ , it is easy to see that there must be some ear  $P_i$  in  $D$  that contains both of them, such that the portion of  $P_i$  between  $x$  and  $y$  is separated from the rest of  $P_i$  when  $x$  and  $y$  are removed from  $G$ . The triconnectivity algorithm tests if such a separating pair of vertices exists by looking for them in each ear in parallel. It does so by constructing, for each nontrivial ear, its *ear graph*, which is a graph derived from the input graph that contains the necessary information about separating pairs of vertices, if any, on the ear. The algorithm then further processes the ear graph to obtain its *coalesced graph*, using which all separating pairs on the ear can

be determined quickly. Efficient parallel algorithms for finding the ear graphs of all nontrivial ears and the coalesced graph of each ear graph are given in [169, 190], leading to a parallel graph triconnectivity algorithm that runs in  $O(\log n)$  time with  $O(m \cdot \log^2 n)$  work on a CRCW PRAM. These ideas generalize to efficient parallel algorithms for finding all separating pairs of vertices in a biconnected graph and for finding the triconnected (or Tutte) components of a biconnected graph. These ideas also generalize to testing for graph four-connectivity (Kanevsky & Ramachandran [129]) giving a parallel algorithm that runs in  $O(\log^2 n)$  time with  $O(n^2)$  processors on an ARBITRARY CRCW PRAM. This approach also gives an  $O(n^2)$  sequential algorithm for the problem, which is an improvement over previously known sequential algorithms for the problem.

Open ear decomposition has been used to obtain a parallel algorithm for finding an  $s-t$  numbering in a biconnected graph (Maon, Schieber & Vishkin [162]) with the same complexity as the connected-components algorithm. This efficient parallel  $s-t$  numbering algorithm has been used in conjunction with an efficient parallel implementation of PQ trees, to obtain a parallel planarity algorithm (Klein & Reif [143]) that runs in  $O(\log^2 n)$  time using  $O(m + n)$  processors on a CREW PRAM.

At present there is no efficient graph search technique known for directed graphs. Thus for most problems on directed graphs, including the basic one of testing if one vertex is reachable from another in a directed graph, the best polylog-time parallel algorithm currently known needs on the order of  $M(n)$  processors.

### 2.3.5. Conclusion

In this section we have presented efficient parallel algorithms for several problems on undirected graphs.

Using the fact that graph problems are typically at least as hard as computing the OR of  $n$  bits or the parity of  $n$  bits, it follows from the lower bounds of Section 3 that graph problems need  $\Omega(\log n)$  parallel time on a CREW or EREW PRAM with no restriction on the number of processors, and  $\Omega(\log n / \log \log n)$  parallel time on a CRCW PRAM with a polynomial number of processors. In practice, graph problems seem to need at least  $\log^2 n$  time on a CREW and EREW PRAM and  $\log n$  time on a CRCW PRAM. We have stated many of the results in this section only for CRCW PRAMs, when it is the case that, by the simulations between the various types of PRAMs, this gives the best bounds known for CREW and EREW PRAMs as well.

## 2.4. Sorting, merging and selection

In this section we discuss parallel algorithms for which the input is an array of  $n$  elements from a linearly ordered set. In the sorting problem, the task is to rearrange the elements into nondecreasing order. In the merging problem, the input array is partitioned into two subarrays, each of which is known to be in nondecreasing order, and the task is to rearrange the entire array into nondecreasing order. In the selection problem an integer  $k$  between 1 and  $n$  is given, and the task is to find the  $k$ th-smallest element of the array. Except for a brief remark in Section 2.4.3. we restrict attention to comparison algorithms, in which the only means of gathering information about the

elements is through pairwise comparisons (i.e., tests of the form “is  $x$  less than  $y$ ?", where  $x$  and  $y$  are elements of the array). For convenience we also assume that the  $n$  elements are distinct.

Valiant [229] proposed a model of parallel comparison algorithms in which, at each step,  $p$  comparisons are performed, where  $p$  is a parameter that we shall call the *degree of parallelism*. It is not required that the  $p$  pairs of elements compared at a given step be disjoint. The choice of the  $p$  comparisons to be performed at a given step can depend in an arbitrary manner on  $n$ , the number of elements, and on the outcomes of previous comparisons. The algorithm terminates when it has acquired enough information about the input to specify the answer (the identity of the  $k$ th smallest element in the case of selection, and the permutation required to put the elements in increasing order, in the case of sorting or merging). The execution time of an algorithm is the number of steps performed. This model is called the *parallel comparison model*.

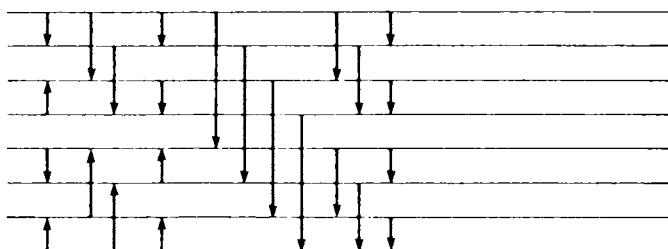

A second model, the *comparator network*, is a restriction of the parallel comparison model. The basic operation in a comparator network is the  $i-j$  comparison-exchange operation, where  $i$  and  $j$  are distinct integers between 1 and  $n$ . Such an operation has the following interpretation: compare the contents of location  $i$  with the contents of location  $j$ ; store the smaller of the two values in location  $i$  and the larger of the two in location  $j$ . If a comparator network has degree of parallelism  $p$ , then each of its steps is specified by at most  $p$  disjoint  $i-j$  pairs, and consists of the simultaneous execution of the comparison-exchange operations corresponding to these pairs. The network is oblivious, in the sense that the set of pairs of locations compared in any given step does not depend on the outcomes of the comparisons performed at earlier steps. A comparator network can be represented by a diagram reminiscent of a sheet of music paper, in which each memory cell is represented by a horizontal line and each  $i-j$  comparison-exchange operation is represented by a vertical line segment between horizontal lines  $i$  and  $j$ , with an arrow directed toward  $i$ , the line that will receive the smaller of the two values being compared. The order in which the comparison-exchange operations affecting a given cell are executed is given by the left-to-right order of the corresponding vertical line segments. From this description it should be clear that, in contrast to the more general parallel comparison model, comparator networks can easily be realized in hardware.

A comparator network is called a *sorting network* if it is guaranteed to rearrange the contents of locations 1 to  $n$  into nondecreasing order. Figure 3 depicts an 8-element

Fig. 3. A sorting network.

comparator network with degree of parallelism 4 and execution time 6. Our discussion of bitonic sort in Section 2.4.2 will establish that this network is a sorting network.

A third model is the comparison PRAM. This is a PRAM for which the input is an array of  $n$  elements from a linearly ordered set. In addition to its usual instruction set, the comparison PRAM is provided with instructions for comparing the elements of the input array and for moving them around in memory. Elements of the input array have no interpretation as bit strings or integers, and thus cannot be used as addresses or as arguments for the arithmetic or shift instructions of the PRAM. The comparison PRAM is a more realistic model than the parallel comparison model, because the time required to move data around, as well as the time required to decide which comparisons are to be performed and which processors will perform them, are counted in the cost of computation along with the cost of the comparisons themselves.

Since the parallel comparison model is more permissive than the comparator network or comparison PRAM, lower bounds on the complexity of comparison problems within that model are valid for the other models as well.

#### 2.4.1. *The complexity of finding the maximum and merging*

In this section we derive tight upper and lower bounds on the complexity of two problems: finding the largest element in an array and merging two sorted arrays. Our lower bounds are for the parallel comparison model, and our upper bounds are for the comparison PRAM. Much of our discussion is based on [229].

We begin by presenting an algorithm for finding the maximum of  $n$  elements on a COMMON CRCW comparison PRAM with  $p$  processors. At a general step within the algorithm, the search for the maximum will have been narrowed down to a set  $S$  of elements from the input array. Initially,  $S$  consists of all  $n$  elements, and the computation terminates when  $S$  becomes a singleton set.

Let  $x$  be the smallest integer such that, when  $S$  is partitioned into  $x$  blocks of size  $\lfloor |S|/x \rfloor$  or  $\lceil |S|/x \rceil$ ,  $p$  comparisons suffice for the direct comparison of each pair of elements that lie in a common block. Then, in one step, the algorithm determines the maximum element in each block of such a partition, and thus eliminates all but  $x$  elements of  $S$ .

It can be shown that, when  $n/2 \leq p \leq \binom{n}{2}$ , the number of iterations required to reduce the cardinality of  $S$  from  $n$  to 1 is  $\log \log n - \log \log(2p/n) + O(1)$ . Also, the computations required at each step for each of the  $p$  processors to determine which pair of elements to compare and for the set of block maxima to be assembled into an array can be carried out in constant time. This establishes that the complexity of finding the maximum on a  $p$ -processor COMMON CRCW comparison PRAM is  $O(\log \log n - \log \log(2p/n))$ .

To prove a lower bound in the parallel comparison model we use a graph-theoretic argument. At the beginning of any step of any comparison-based algorithm, there will remain a set  $S$  of candidates for the maximum; an element will lie in  $S$  if it has never been compared with a larger element. At a general step, the comparisons performed between candidate elements can be represented by the edges of a graph  $G$  whose vertices are the candidate elements. An adversary can choose any set  $S'$  which is independent in  $G$  (i.e., no two elements of  $S'$  are compared with each other in the step), and can consistently

specify the outcomes of comparisons so that all the elements of  $S'$  remain candidates. A theorem of Turan in extremal graph theory shows that, in any graph  $G$  having  $v$  vertices and  $e$  edges, there is an independent set of size at least  $v^2/(v+2e)$ . Thus, the adversary can ensure that the candidate set  $S'$  is of size at least  $|S|^2/(|S|+2p)$ . It follows that, against such an adversary strategy, any algorithm requires  $\log \log n - \log \log(2p/n) + O(1)$  steps when  $n/2 \leq p \leq \binom{n}{2}$ . Hence, for this range of values of  $p$ , the algorithm described above is optimal in the parallel comparison model and optimal within a constant factor on a COMMON CRCW comparison PRAM. Interestingly, on a CREW comparison PRAM, finding the maximum requires time  $\Omega(\log n)$ , even when no limit is placed on the number of processors, and there is a simple optimal  $O(\log n)$  time EREW PRAM algorithm for the problem.

For the problem of selecting the median of  $n$  elements with degree of parallelism  $n$ , a lower bound of  $\Omega(\log \log n)$  is implied by the lower bound for the maximum problem. A matching upper bound for the comparison model has been given by Ajtai, Komlós, Steiger & Szemerédi [6] building on earlier work by Cole & Yap [59]. It follows from [29] (Beame & Hastad) that finding the median on a CRCW comparison PRAM using a polynomial-bounded number of processors requires time  $\Omega(\log n / \log \log n)$ .

We now turn to the problem of merging nondecreasing sequences of lengths  $n$  and  $m$ , where  $n \leq m$ . We begin by giving an algorithm within the parallel comparison model that has degree of parallelism  $n+m$  and execution time  $O(\log \log n)$ . Let the two sequences be  $A$  and  $B$ , where  $A = (a_1, a_2, \dots, a_n)$  and  $B = (b_1, b_2, \dots, b_m)$ . The algorithm is as follows.

- (1) Divide  $A$  into  $\sqrt{n}$  blocks of length  $\sqrt{n}$ , and  $B$  into  $\sqrt{m}$  blocks of length  $\sqrt{m}$  (here we ignore the simple modifications needed when the length of  $A$  or the length of  $B$  is not a perfect square).

- (2) Let  $\alpha_i$  be the first element of the  $i$ th block of  $A$ , and  $\beta_j$  the first element of the  $j$ th block of  $B$ . **In parallel**, compare each  $\alpha_i$  with each  $\beta_j$  (the number of processors required is  $\sqrt{n}\sqrt{m}$ , which is at most  $(m+n)/2$ ).

- (3) **In parallel** for each  $\alpha_i$  do

- let  $j(i)$  be the unique index such that  $\beta_{j(i)} < \alpha_i < \beta_{j(i)+1}$  (here we use the convention that  $\beta_0 = -\infty$  and  $\beta_{\sqrt{m}+1} = +\infty$ ).

- (4) Compare  $\alpha_i$  with each element of the block starting with  $\beta_{j(i)}$ .

At this point, the algorithm has determined where each  $\alpha_i$  fits into  $B$ , and thus the problem has been reduced to a set of disjoint merging problems, each of which involves merging a block of length  $\sqrt{n}$  from  $A$  with some consecutive subsequence of  $B$ . Recursively, solve each of these subproblems, using a degree of parallelism equal to the number of elements.

Let  $T(n)$  be the time required by this algorithm to merge a sequence of length  $n$  with a sequence of length  $m$ , where  $n \leq m$ , using  $n+m$  processors. Since the parallel computation model charges only for the comparison steps, and not for the bookkeeping involved in keeping track of the results of comparisons and determining which comparisons to perform next, we have  $T(1) = 1$  and  $T(n) \leq 2 + T(\sqrt{n})$ . This gives  $T(n) = O(\log \log n)$ .

This algorithm can be implemented to run in time  $O(\log \log n)$  time with  $n+m$  processors on a CREW PRAM, although the processor allocation problems are not entirely trivial (Borodin & Hopcroft [41]).

Following Borodin & Hopcroft we now prove that, in the parallel comparison model, the time required to merge two sequences of length  $n$  using  $2n$  processors is  $\Omega(\log \log n)$ . In order to prove the lower bound we consider the following generalization of the problem: given ordered sequences  $A_1, B_1, A_2, B_2, \dots, A_k, B_k$ , each of length  $s$ , and the information that, for  $i = 1, 2, \dots, k-1$ , each element of  $A_i \cup B_i$  is less than each element of  $A_{i+1} \cup B_{i+1}$ , merge each of the pairs  $A_i, B_i$  using  $cks$  processors. We refer to this problem as the  $c, k, s$  problem.

Let the worst-case time to solve this problem in the parallel comparison model be  $t(c, k, s)$ , and let  $T(c, s) = \min_k t(c, k, s)$  where  $k$  ranges over the positive integers. We shall use an adversary argument to prove that  $T(c, s) \geq 1 + T(16c/7, s')$  where  $s' = \sqrt{s/8c}$ . Consider the first step in solving a  $c, k, s$  problem. We have  $ks \times s$  merging problems and  $cks$  processors. For  $i = 1, 2, \dots, k$ , partition  $A_i$  into  $2\sqrt{2cs}$  blocks  $A_i^1, A_i^2, \dots, A_i^{2\sqrt{2cs}}$ , each of size  $s'$ , partition  $B_i$  similarly, form a  $2\sqrt{2cs} \times 2\sqrt{2cs}$  matrix  $M_i$ , and mark the  $[a, b]$  cell of this matrix if some element of  $A_i^a$  is compared with some element of  $B_i^b$  at the first step. Each of the  $M_i$ ,  $i = 1, \dots, k$  has  $8cs$  cells, so that the total number of cells in all matrices is  $8cks$ . At most  $cks$  of these cells are marked. Also, each matrix has  $4\sqrt{2cs} - 1$  diagonals parallel to the main diagonal. By a simple averaging argument, it is possible to choose a diagonal in each of these matrices, such that the number of unmarked cells in the chosen diagonals is at least  $7k\sqrt{2cs}/8$ . An adversary can specify the outcomes of these comparisons so that each unmarked cell on the selected diagonals corresponds to an independent  $s' \times s'$  merging problem at the next step. It follows that the adversary can leave the algorithm with  $k'$  independent merging problems to solve, each of which is  $s' \times s'$ , where  $k' = 7k\sqrt{2cs}/8$ . The number of processors is  $cks$ , which is equal to  $16ck's'/7$ . This leads to the inequality  $T(c, s) \geq 1 + T(16c/7, s')$ . It follows that  $T(c, s) \geq d \log \log c s$ , where  $d$  is a certain positive constant. In particular, the complexity of merging two ordered sequences of length  $n$  with  $2n$  processors is at least  $T(2, n)$  which is  $\Omega(\log \log n)$ . This establishes that the algorithm we have given is optimal up to a constant factor, both for the parallel comparison model and the CREW comparison PRAM.

#### 2.4.2. Sorting networks

One of the classic parallel sorting methods is Batcher's bitonic sorting network [26]. This network is based on the properties of certain sequences. Let  $A = (a_1, a_2, \dots, a_n)$  be a sequence of distinct elements of a linearly ordered set. For  $i = 2, 3, \dots, n-1$ , call element  $a_i$  a *local minimum* if both  $a_{i-1}$  and  $a_{i+1}$  are greater than  $a_i$ , and a *local maximum* if both  $a_{i-1}$  and  $a_{i+1}$  are less than  $a_i$ . The sequence  $A$  is called *unimodal* if it has at most one element that is a local minimum or local maximum, and *bitonic* if it is a cyclic shift of a unimodal sequence. The following lemma is due to Batcher.

LEMMA. Let  $A = (a_1, a_2, \dots, a_{2N})$  be a bitonic sequence of even length. Define the sequence  $L(A)$  and  $R(A)$  as follows:

$$L(A) = (\min(a_1, a_{N+1}), \min(a_2, a_{N+2}), \dots, \min(a_N, a_{2N}))$$

and

$$R(A) = (\max(a_1, a_{N+1}), \max(a_2, a_{N+2}), \dots, \max(a_N, a_{2N})).$$

Then the sequences  $L(A)$  and  $R(A)$  are bitonic, and each element of  $L(A)$  is less than each element of  $R(A)$ .

The lemma suggests a parallel method of sorting a bitonic sequence  $A$  whose length  $n$  is a power of 2: if  $A$  is of length 1 then halt; else compare corresponding elements of the left and right half of  $A$  and form the arrays  $L(A)$  and  $R(A)$ ; in parallel, sort  $L(A)$  and  $R(A)$ . This algorithm can be realized by a comparator network with degree of parallelism  $n/2$  and execution time  $\log n$ .

Batcher's bitonic sorting network is built upon this algorithm for sorting a bitonic sequence. Starting with an unsorted  $n$ -element array, which can be regarded as a list of  $n/2$  bitonic sequences of length 2, the algorithm constructs a list of  $n/4$  bitonic sequences of length 4, then a list of  $n/8$  bitonic sequences of length 8, and so forth until the array has been transformed into a single bitonic sequence of length  $n$ , which may then be sorted. The algorithm exploits the fact that the concatenation of an increasing sequence with a decreasing sequence is a bitonic sequence. Thus, to convert a list of  $n/2^i$  bitonic sequences of length  $2^i$  into a list of  $n/2^{i+1}$  bitonic sequences of length  $2^{i+1}$ , it suffices to sort the sequences of length  $2^i$  alternately into increasing and decreasing order, using the algorithm for sorting a bitonic sequence. Figure 3 shows a bitonic sorting network for 8 elements.

We now analyze the execution time of the bitonic sorting algorithm. Let  $B(n)$  be the time required to sort a bitonic sequence of length  $n$  using degree of parallelism  $n/2$ , and let  $S(n)$  be the time required to sort an array of length  $n$ , again using degree of parallelism  $n/2$ . Then  $B(2^k) = k$ , and

$$S(2^k) = \sum_{i=1}^k B(2^i) = \binom{k+1}{2}$$

Thus bitonic sort requires time  $O(\log^2 n)$  to sort  $n$  elements using degree of parallelism  $n/2$ . Bitonic sort is also easily implemented on an EREW comparison PRAM. Again, it runs in time  $O(\log^2 n)$  using  $n/2$  processors. As an aside, we mention that bitonic sort can also be implemented very neatly to run within these time and processor bounds on certain fixed-degree networks, such as the butterfly and shuffle-exchange network.

Batcher's bitonic sorting network requires  $\Theta(n \log^2 n)$  comparators. Since there exist sequential sorting algorithms that require only  $O(n \log n)$  comparisons in the worst case, it was natural to ask whether one could improve on Batcher's construction by exhibiting sorting networks requiring only  $O(n \log n)$  comparators. In 1983 this question was answered affirmatively by Ajtai, Komlós & Szemerédi [7]. The family of sorting networks given by these three authors also has theoretical advantages for parallel computation, since they execute in time  $O(\log n)$  using degree of parallelism  $n/2$ . However, despite the substantial improvements obtained by later researchers (Paterson [183]), the constant implied by the "big O" is so large that bitonic sort is

preferable for all practical values of  $n$ . Since the Ajtai–Komlós–Szemerédi networks are presented in detail in [186], we shall not attempt to describe them here.

#### 2.4.3. Sorting on a PRAM

Since the sequential complexity of sorting by comparisons is  $\theta(n \log n)$ , it is of interest to investigate methods for sorting on a comparison PRAM that run in polylog time and have a processor–time product that is  $O(n \log n)$ . Randomized methods that use  $O(n)$  processors and run in  $O(\log n)$  time with high probability are given in [201, 200]. The first deterministic method to achieve such performance was an EREW comparison PRAM algorithm based on the Ajtai–Komlós–Szemerédi sorting network. It achieves an execution time of  $O(\log n)$  using  $O(n)$  processors; however, the constant factor in the time bound is so large as to render the method impractical. Using a new version of bitonic merging, Bilardi & Nicolau [35] give a sorting algorithm for the EREW comparison PRAM that achieves a processor–time product of  $O(n \log n)$  using  $O(n/\log n)$  processors. Moreover, the constant factor in the time bound is small, so that the method is attractive for practical use. Cole [53] has given a practical deterministic method of sorting on an EREW comparison PRAM in time  $O(\log n)$  using  $O(n)$  processors. His algorithm can be viewed as a pipelined version of merge sort. Finally, we point out that when the elements to be sorted are integers in a limited range, better bounds are achievable by using bucket sorting methods rather than comparison algorithms [196, 111].

The rest of this section is devoted to a presentation of Cole’s sorting algorithm. For simplicity, we confine ourselves to describing a version of the algorithm that runs on a CREW comparison PRAM. We assume for convenience that the number of elements to be sorted is a power of 2. Let the  $2^k$  elements to be sorted be placed in correspondence with the leaves of a complete binary tree  $T$  of height  $k$ ; hereafter, we make no distinction between a leaf and the corresponding element. Each internal node  $v$  within  $T$  is the root of a subtree; let  $T_v$  be the set of leaves of that subtree. Then the task of node  $v$  is to arrange the elements of  $T_v$  into a sorted list.

An obvious method of creating the required lists would be to move up the tree level-by-level from the leaves to the root, using the merging algorithm of Section 2.4.1 to create the list for each node by merging the lists for its two children. Using the fact that the time to merge two sorted lists of length  $t$  using  $2t$  processors is  $O(\log \log t)$ , a simple analysis shows that this obvious method runs in time  $O(\log n \log \log n)$  using  $O(n)$  processors. Cole improves on this approach by having the algorithm work on many levels of the tree at once, creating successively more refined approximations to the lists that the nodes must eventually produce. The method of approximation is chosen so that each approximation to the final list for a node can be obtained from the preceding approximation in constant time.

Associated with any time step  $s$  and internal node  $v$  is a list  $LIST_v(s)$ ; this list is an increasing sequence of elements drawn from  $T_v$ . We say  $v$  is *finished* at time  $s$  if  $LIST_v(s)$  contains all the elements of  $T_v$ . Node  $v$  is a *frontier node* when  $v$  is finished but its parent is not. Initially, the leaves of  $T$  are its frontier nodes. At any time  $s$ , all the frontier nodes are at the same distance from the root of  $T$ .

At every step, each frontier node or unfinished node passes a subsequence of its list up

to its parent. For node  $v$  at step  $s$  we call this subsequence  $UP_v(s)$ . Node  $v$  forms  $LIST_v(s)$  by merging  $UP_x(s)$  with  $UP_y(s)$ , where  $x$  and  $y$  are the children of  $v$ . If  $x$  is unfinished at step  $s-1$  then  $UP_x(s)$  consists of every fourth element of  $LIST_x(s-1)$ ; i.e., elements 1, 5, 9, 13, ... If  $x$  becomes finished at step  $s$  then  $UP_x(s+1)$  consists of every fourth element of  $LIST_x(s)$ ,  $UP_x(s+2)$  consists of every second element of  $LIST_x(s)$  and  $UP_x(s+3)$  is equal to  $LIST_x(s)$ . It follows that a node becomes finished three steps after its children do. The sorting process is completed after  $3k$  steps, when the root becomes finished.

It remains to show that each step can be completed in constant time on a CREW PRAM using  $O(n)$  processors. At each step the sum of the lengths of all the lists associated with unfinished or frontier nodes is  $O(n)$ . Thus it suffices to give a method of merging the lists  $UP_x(s)$  and  $UP_y(s)$  in constant time, using one processor per list element. The key idea is to use information from previous steps. Given two ordered lists  $A$  and  $B$ , define a *cross-link array* from  $A$  into  $B$  to be an array of pointers from  $A$  into  $B$  such that each element  $a$  in  $A$  points to the least element in  $B$  that is greater than  $a$  (or, if no such element exists, to a sentinel placed at the end of the list  $B$ ). If the ordered lists  $A$  and  $B$  are disjoint then, given cross-links from  $A$  into  $B$  and from  $B$  into  $A$ , each element can quickly calculate its rank order in the list that results from merging  $A$  and  $B$ , and thus  $A$  and  $B$  can be merged in constant time. Cole's algorithm maintains certain cross-link arrays in order to speed up the merging process. If nodes  $x$  and  $y$  are siblings in  $T$  then, upon the completion of step  $s-1$ , the algorithm maintains cross-links from  $UP_x(s-1)$  into  $UP_y(s-1)$  and  $LIST_x(s-1)$ , and, symmetrically, from  $UP_y(s-1)$  into  $UP_x(s-1)$  and  $LIST_y(s-1)$ . Given the cross-links from  $UP_x(s-1)$  into  $LIST_x(s-1)$  it is easy, in constant time, to create cross-links from  $UP_x(s-1)$  into  $UP_x(s)$ . Similarly, cross-links can be constructed in constant time from  $UP_y(s-1)$  into  $UP_y(s)$ . Moreover, it can be shown that at most four elements of  $UP_x(s-1)$  point to any element of  $UP_x(s)$ . Given all this cross-link information, it is possible in constant time on a CREW comparison PRAM to create cross-links between  $UP_x(s)$  and  $UP_y(s)$ , to merge those two sequences, and to create the cross-links required for the next step. It follows that each step can be executed in constant time using  $O(n)$  processors on a CREW comparison PRAM, and thus Cole's algorithm sorts in time  $O(\log n)$  using  $O(n)$  processors on a CREW comparison PRAM.

## 2.5. Further topics

Efficient parallel algorithms have been developed for a number of other combinatorial problems, including string matching [88, 137, 151, 237, 33], set manipulation [17], computational geometry [4, 14, 15, 16, 51, 54, 108, 198] and graph algorithms [52, 112, 142]. In [78, 99] extensive surveys of efficient parallel algorithms are given including the topics of Sections 2.1–2.3.

Some of the challenges that have thus far eluded researchers in the area of efficient and optimal combinatorial parallel algorithms are the following: