# Formal Verification by Symbolic Evaluation of Partially-Ordered Trajectories\*

Carl-Johan H. Seger

Department of Computer Science

University of British Columbia

Vancouver, B.C. V6T 1Z4 Canada

Randal E. Bryant

School of Computer Science

Carnegie Mellon University

Pittsburgh, PA 15213 USA

July 1, 1999

## Abstract

Symbolic trajectory evaluation provides a means to formally verify properties of a sequential system by a modified form of symbolic simulation. The desired system properties are expressed in a notation combining Boolean expressions and the temporal logic “next-time” operator. In its simplest form, each property is expressed as an assertion  $[A \implies C]$ , where the antecedent  $A$  expresses some assumed conditions on the system state over a bounded time period, and the consequent  $C$  expresses conditions that should result. A generalization allows simple invariants to be established and proven automatically.

The verifier operates on system models in which the state space is ordered by “information content”. By suitable restrictions to the specification notation, we guarantee that for every trajectory formula, there is a unique weakest state trajectory that satisfies it. Therefore, we can verify an assertion  $[A \implies C]$  by simulating the system over the weakest trajectory for  $A$  and testing adherence to  $C$ . Also, establishing invariants correspond to simple fixed point calculations.

This paper presents the general theory underlying symbolic trajectory evaluation. It also illustrates the application of the theory to the task of verifying switch-level circuits as well as more abstract implementations.

## 1 Introduction

Verifying a digital system by conventional simulation is feasible only for very small systems, since the large number of possible initial states and input sequences would require massive amounts of case analysis. By exploiting a combination of *abstraction* and *symbolic manipulation*, on the other hand, symbolic trajectory evaluation can verify the behavior of complex systems by a modified form of simulation. This method exploits abstraction by extending the system state space to include elements representing sets of actual states, yielding a partially-ordered system model. A single simulation sequence can then verify that the system would produce a unique result for a set of

---

\*This research was supported by the Defense Advanced Research Projects Agency, ARPA Order Number 4976, by the National Science Foundation, under grant number MIP-8913667, by operating grant OGPO 109688 from the Natural Sciences and Engineering Research Council of Canada, and by a fellowship from the B. C. Advanced Systems Institute.

initial states or input sequences. It exploits symbolic manipulation by a modified form of symbolic simulation. The Boolean expressions appearing in the system specification are converted into symbolic patterns for the simulator. Like a conventional simulation, a single run of the trajectory evaluator models the system behavior over a single state sequence, although this sequence is both symbolic and partially-ordered.

## 1.1 Partially-Ordered System Modeling

In earlier work, we demonstrated the utility of ternary modeling for verifying a variety of circuits [11, 12]. Our methodology was based on ternary simulation of VLSI circuits, where a third value  $X$  is added to the set  $\{0, 1\}$  of possible signal values, indicating an unknown or indeterminate logic value. Assuming a monotonicity property of the simulation algorithm, one can ensure that any binary (i.e., 0 or 1) values resulting when simulating patterns containing  $X$ 's would also result when the  $X$ 's are replaced by any combination of 0's and 1's. Thus, the number of patterns that must be simulated to verify a circuit can often be reduced dramatically by representing many different operating conditions by patterns containing  $X$ 's. For example, we can verify that a particular sequence of actions will yield a 1 (or 0) on some node regardless of the initial state by verifying that this value results when starting from an initial state where all nodes are set to  $X$ . This requires far less effort than analyzing the effect of the action on all possible initial binary states.

Ternary modeling is a special case of a more general abstraction technique based on partially-ordered system models. That is, the actual state space of the circuit (in this case all possible combinations of binary values) is extended with values representing sets of circuit states, such that the resulting state set is partially ordered. With ternary simulation, a state with some nodes set to  $X$  covers those circuit states obtained by replacing the  $X$  values with all combinations of 0 and 1. The state with all nodes set to  $X$  thus covers all possible actual circuit states. By extending the next-state function of the circuit to one over the expanded state set, we can verify circuit behavior for a set of different operating conditions with a single simulation run. By suitable restrictions of the specification syntax and the extended next-state function, we can guarantee that any property verified on this more abstract form of simulation must also hold for the original circuit.

In this paper we generalize our previous results on ternary simulation to a wider class of partially-ordered system models. This generalization simplifies the presentation by allowing us to focus on the essential properties of the abstraction technique while eliminating artifacts specific to ternary modeling. It also allows us to apply our methods to higher level data domains than simple binary-valued signals.

## 1.2 Symbolic Simulation

Although ternary modeling, or its generalization, allows us to cover many conditions with a single simulation sequence, it lacks the analytic power required for complete verification, except for restricted classes of circuits such as memories [11]. We have shown that by combining ternary modeling with symbolic simulation [1], we can model even more complex sets of behaviors with a single simulation run. With ternary symbolic simulation, the simulation algorithm designed to operate on scalar values 0, 1, and  $X$ , is extended to operate on a set of symbolic values. Each symbolic value indicates the value of a signal for many different operating conditions, parameterized in terms of a set of symbolic Boolean variables. In essence, ternary symbolic simulation allows us to combine multiple ternary simulation sequences into a single symbolic sequence.

Simulators that support ternary modeling intentionally err on the side of pessimism for the sake of efficiency. That is, they will sometimes produce a value  $X$  even where exhaustive case analysis would indicate that the value should be binary (i.e., 0 or 1). For example, most ternary simulators

evaluate logic functions in a ternary algebra created by extending the standard Boolean operators. This algebra does not obey the law of excluded middle, because  $X + \overline{X} = X$ , where  $+$  and  $\overline{\phantom{X}}$  are ternary extensions of Boolean sum and complement, respectively. On the other hand, symbolic simulation avoids this pessimism, because it can resolve the interdependencies among signal values, and compute  $a + \overline{a} = 1$  (the Boolean function that always yields 1). By combining the expressive power of symbolic values with the computational efficiency of ternary values, we can trade off precision for ease of computation.

### 1.3 Symbolic Trajectory Evaluation

Symbolic trajectory evaluation takes the notion of ternary symbolic simulation one step further by providing a concrete means of specifying and verifying the desired behavior of the system operating over time. In earlier papers [9, 13], we introduced the notion of symbolic trajectory evaluation for ternary system models and demonstrated its utility on several actual circuits. In this paper we generalize the technique to a wider class of system models and specifications. We also make our previous, informal claims more precise and rigorous.

Our specifications take the form of *symbolic trajectory formulas* mixing Boolean expressions and the temporal *next-time* operator. The Boolean expressions provide a convenient means of describing many different operating conditions in a compact form. By allowing only the most elementary of temporal operators, the class of properties we can express is relatively restricted, as compared to other temporal logics [16, 32]. Nonetheless, we have found that we can readily express many aspects of synchronous digital systems at various levels of abstraction. It is quite adequate for expressing many of the subtleties of system operation, including clocking conventions and pipelining.

Our decision algorithm is based on a generalized symbolic simulation. In its simplest form it tests the validity of an *assertion* of the form  $[A \implies C]$ , where both  $A$  and  $C$  are trajectory formulas. That is, it determines whether or not every state sequence satisfying  $A$  (the “antecedent”) must also satisfy  $C$  (the “consequent”). It does this by generating a symbolic simulation sequence corresponding to the antecedent, and testing whether the resulting symbolic state sequence satisfies the consequent.

A more complex condition of the form  $[A \implies C]^* ; G$  can also be verified, where  $A$  and  $C$  are trajectory formulas and  $G$  is an assertion. Intuitively, the formula is deemed to hold if and only if for every sequence of states the system may go through, if the state sequence satisfies some number of iterations of  $A$ , then it must also satisfy the same number of iterations of  $C$  and furthermore the remaining sequence must satisfy  $G$ . Assertions of this form are useful for verifying circuits that may remain in an idle state for an unbounded amount of time, e.g., for a processor held in a “wait-state” by the memory subsystem. Our verification method proves invariants of this form by using symbolic simulation to compute a fixed-point which intuitively serves as a “summary” of what states the system can be in after it has gone through any number of iterations of  $A$ .

An important property of our algorithm is that it requires a comparatively small amount of simulation and symbolic manipulation to verify an assertion. The restrictions we impose on the formula syntax guarantee that there is a unique weakest symbolic sequence satisfying the antecedent. Furthermore, the symbolic manipulations involve only variables explicitly mentioned in the assertion. Unlike other symbolic circuit verifiers [5], we do not need to introduce extra variables denoting the initial circuit state or possible primary inputs. Finally, the length of the simulation sequence depends only on the depth of nesting of temporal next-time operators in the assertion and the speed of convergence of the fixed-point calculations.

| Symbolic? | Model   | Patterns | Variables                   |

|-----------|---------|----------|-----------------------------|

| No        | Binary  | $2^n$    | 0                           |

| Yes       | Binary  | 1        | $n$                         |

| No        | Ternary | $n + 1$  | 0                           |

| Yes       | Ternary | 1        | $\lceil \log(n + 1) \rceil$ |

Table 1: Requirements for Verifying  $n$ -input AND gate.

| Signal | Scalar Cases |     |     |     |     |     |     |   | Symbolic      |                                 |

|--------|--------------|-----|-----|-----|-----|-----|-----|---|---------------|---------------------------------|

|        | 0            | 1   | 2   | 3   | 4   | 5   | 6   | 7 | High          | Low                             |

| in0    | 0            | $X$ | $X$ | $X$ | $X$ | $X$ | $X$ | 1 | $i_2 i_1 i_0$ | $\bar{i}_2 \bar{i}_1 \bar{i}_0$ |

| in1    | $X$          | 0   | $X$ | $X$ | $X$ | $X$ | $X$ | 1 | $i_2 i_1 i_0$ | $\bar{i}_2 \bar{i}_1 i_0$       |

| in2    | $X$          | $X$ | 0   | $X$ | $X$ | $X$ | $X$ | 1 | $i_2 i_1 i_0$ | $\bar{i}_2 i_1 \bar{i}_0$       |

| in3    | $X$          | $X$ | $X$ | 0   | $X$ | $X$ | $X$ | 1 | $i_2 i_1 i_0$ | $\bar{i}_2 i_1 i_0$             |

| in4    | $X$          | $X$ | $X$ | $X$ | 0   | $X$ | $X$ | 1 | $i_2 i_1 i_0$ | $i_2 \bar{i}_1 \bar{i}_0$       |

| in5    | $X$          | $X$ | $X$ | $X$ | $X$ | 0   | $X$ | 1 | $i_2 i_1 i_0$ | $i_2 \bar{i}_1 i_0$             |

| in6    | $X$          | $X$ | $X$ | $X$ | $X$ | $X$ | 0   | 1 | $i_2 i_1 i_0$ | $i_2 i_1 \bar{i}_0$             |

| out    | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 1 | $i_2 i_1 i_0$ | $\bar{i}_2 + \bar{i}_1 + i_0$   |

Table 2: Verification of 7-input AND Gate by Ternary Modeling

#### 1.4 Illustrative Example

To illustrate the combined use of partially-ordered system modeling and symbolic simulation, consider the task of using a simulator to verify that a given circuit has the functionality of an  $n$ -input AND gate. Four approaches are tabulated in Table 1, according to whether the simulation is conventional or symbolic, and whether it uses a binary or a ternary system model. With binary modeling, we would need to simulate either  $2^n$  conventional patterns, or a single symbolic pattern of  $n$  variables—one per input. In either case, we must, in effect, exhaustively evaluate the circuit functionality.

With ternary modeling, we can exploit the property that if at least one of the inputs to the gate is 0, the output should be 0 regardless of the other inputs. Even with a conventional simulator, we can verify the circuit with just  $n + 1$  patterns. These are illustrated for the case of  $n = 7$  in Table 2. First, there are  $n$  patterns that set one input to 0, the remaining to  $X$ , and checks that the output is 0. The remaining pattern sets all inputs to 1 and checks that the output is 1.

By the method of *symbolic indexing*, our ternary symbolic simulator can encode all of these cases with a single symbolic pattern [1]. That is, we think of the patterns as being indexed from 0 to  $n$ . These index values are then encoded in binary and represented symbolically by a set of  $\lceil \log(n + 1) \rceil$  index variables. In our example with  $n = 7$ , we require three index variables:  $i_2$ ,  $i_1$ , and  $i_0$ . The signal values are then functions over these index variables mapping to the set  $\{0, 1, X\}$ . We can in turn represent each of these functions as a pair of Boolean functions, indicating the cases where the signal is 1 (“High”) or 0 (“Low”), with the signal otherwise being  $X$ . Table 2 shows the encoding of the eight ternary patterns by symbolic indexing. The High function is satisfied only when all index variables are assigned value 1, corresponding to the binary representation of 7. The Low function for each signal is satisfied when the index value matches the input number. Thus, each decoding of the index variables corresponds to one of the scalar ternary patterns.

This simple example illustrates how multi-valued modeling can be combined with symbolic simulation. By this method, we can efficiently cover a wide range of circuit operating conditions with a single symbolic simulation pattern involving far fewer variables than would be required for a complete binary symbolic simulation. In the case of an AND gate, we have reduced the number of variables to be logarithmic in the circuit size. For large systems involving many state variables, such reductions can lead to a dramatic improvement in symbolic manipulation efficiency.

Note also that even though we model circuit operation over multiple-valued signals, we utilize binary encodings of these signals so that they can be represented symbolically with OBDDs. This avoids the need to implement special data structures and manipulation algorithms for multi-valued functions. In general, we think of the Boolean variables of the symbolic simulator as providing a set of index variables. Each decoding of the variables covers one of the cases required for verification.

## 1.5 Related Work

Our approach to verification relates most closely to the symbolic model checking algorithms devised by a number of researchers [5, 15, 19]. Like our program, these algorithms verify that a finite state system, modeled symbolically, obeys a property expressed in temporal logic. Despite these general similarities, however, there are significant differences in the capabilities and complexities of the algorithms. In particular, our method is the most restricted in terms of the class of systems that can be modeled and in the properties that can be verified. For example, other symbolic model checkers [15] can model an arbitrary, nondeterministic system, since the system is described by a transition relation. The symbolic verifier for LUSTRE programs [25] is based on a next-state function representation of system behavior, but allows the inputs on each time step to be chosen nondeterministically. In computing circuit behavior by a form of simulation, our method effectively models system behavior in terms of the next-state functions for the circuit state elements. Furthermore, we do not choose inputs nondeterministically, but rather constrain the inputs according to the antecedents of the assertion formulas. We can model some forms of nondeterministic behavior by encoding a set of possible states with the value corresponding to the greatest lower bound in the partial ordering. This form of modeling would yield overly pessimistic results for highly divergent system behaviors.

Although our method does not compare favorably to symbolic model checking for verifying highly nondeterministic systems, we can efficiently model circuit behavior with more detailed circuit and timing models. In particular, we can handle most of the techniques found in (discrete) circuit simulators, including switch-level models, arbitrary clocking schemes, and various delay models for the circuit elements. Our verifier is thus one of the few that can model system behavior at a level of timing granularity finer than complete clock cycles.

In its most general form, verification by symbolic model checking can decide a class of formulas consisting of a complete branching time, propositional temporal logic. Our method can only be used to verify properties of bounded state sequences, intermixed with periods of invariant behavior. Our restrictions on the formulas to be checked allow us to verify system behavior by simulating circuit behavior over a single, symbolic state sequence. There are other precedents for restricting the class of formulas that can be checked in order to improve the efficiency of the verifier. For example, Clarke, Grumberg, and Long [17] have shown that by restricting the use of negation and existential operators, they can reliably replace a detailed system model by a more simplified abstraction. Any property proved of the abstract model is guaranteed to hold for the more detailed one. Similarly, we prohibit negation and even disjunction in our logic to make it possible to conservatively approximate the circuit behavior by a single, symbolic state sequence.

One can view the combined effect of these research projects as providing a spectrum of checking-

based verifiers that trade off between expressiveness and performance.

Most other automated approaches to sequential circuit verification are based on testing state machine equivalence [18, 21]. Such methods are useful for comparing two different (but hopefully equivalent) representations of the system, such as one at a register-transfer level and one at a gate level. However, they do not work well for verifying the correctness of incompletely specified systems, nor for reasoning about systems that employ methods, such as pipelining, that shift the sequencing of activities in time. Furthermore, most of these methods assume that the system starts in some known initial state. In actual circuits, the initial state usually cannot be predicted.

Symbolic simulation has been proposed by others as a hardware verification technique. Bose and Fisher have shown that these methods can be applied to complex circuits, including ones with pipelining [4]. Their method, however, requires a complete characterization of the system by binary symbolic simulation. That is, the user identifies each place state is stored in the circuit, either as charge on a node, or as a pair of complementary values within a static memory element. They then symbolically simulate a single clock cycle, where each state variable and each input signal is represented by a distinct Boolean variable, yielding a complete characterization of the next-state functions for every state variable. This process of extracting the explicit next-state function can be quite costly. In contrast, our method represents the next-state function implicitly as a combination of circuit structure and simulation algorithm. We only compute the next-state behavior for the particular patterns required to verify a given assertion. These patterns involve far fewer variables than is required by Bose and Fisher's functional extraction.

Other researchers have suggested symbolic simulation as a means of circuit verification [20, 33]. None of this work has presented a clear methodology for sequential circuit verification, however.

## 1.6 Outline of Paper

This paper presents the theoretical basis for symbolic trajectory evaluation. Following a summary of the mathematical foundations, we describe the concept of partially-ordered system models and how a system can be represented by the language consisting of all possible compatible state sequences, referred to as trajectories. Next we introduce a “scalar” version of the specification notation, where only constant expressions are permitted. We show that any assertion in this notation can be verified by simulating the (unique) weakest state sequence satisfying the antecedent and testing adherence to the consequent. We then show that the concepts generalize to the symbolic case, where the specifications may contain expressions over a set of Boolean variables. One can view a symbolic assertion as simply encoding a number of scalar assertions that can then be evaluated simultaneously through symbolic simulation. Finally, we discuss some of the practical issues of implementing and applying our theory to real-life digital circuits.

## 2 Mathematical Background

In this section we give concise definitions of many concepts used throughout the paper. Readers unfamiliar with the notation of lattice theory may wish to refer an introductory text for additional information.

In general, we use calligraphic letters  $\mathcal{A}, \mathcal{B}, \dots$ , to denote sets and lower case letters,  $a, b, \dots$ , to denote individual elements of sets. Unless otherwise stated, all sets are assumed to be finite.

The *cartesian product*  $\mathcal{A} \times \mathcal{B}$  of two sets  $\mathcal{A}$  and  $\mathcal{B}$  is the set of all ordered pairs  $(a, b)$ , where  $a \in \mathcal{A}$  and  $b \in \mathcal{B}$ . A *binary relation* on a set  $\mathcal{B}$  is any subset of  $\mathcal{B} \times \mathcal{B}$ . Let  $R$  be a binary relation on  $\mathcal{B}$ , i.e.,  $R \subseteq \mathcal{B} \times \mathcal{B}$ . We say that  $R$  is *reflexive* iff  $aRa$  for all  $a \in \mathcal{B}$ . Similarly,  $R$  is *antisymmetric* iff  $aRb$  and  $bRa$  implies  $a = b$  for all  $a, b \in \mathcal{B}$ . Finally,  $R$  is *transitive* iff  $aRb$  and  $bRc$  implies  $aRc$ .

for all  $a, b, c \in \mathcal{B}$ . A binary relation on  $\mathcal{B}$  which is reflexive, antisymmetric, and transitive is called a *partial order* on  $\mathcal{B}$ .

A *poset* (partially ordered set) is an ordered pair  $\langle \mathcal{S}, \sqsubseteq \rangle$ , where  $\mathcal{S}$  is a set and  $\sqsubseteq$  is a partial order on  $\mathcal{S}$ . Intuitively, we will view a partial order as ordering the values by their “information content.” That is, elements less than others “contain less information”.

If  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a poset,  $\mathcal{A} \subseteq \mathcal{S}$ , and  $b \in \mathcal{S}$ , then  $b$  is a *lower bound* of  $\mathcal{A}$  iff  $b \sqsubseteq a$  for all  $a \in \mathcal{A}$ . A lower bound  $a$  of  $\mathcal{A}$  is called *greatest lower bound* of  $\mathcal{A}$ , written  $glb(\mathcal{A})$ , if and only if  $b \sqsubseteq a$  for every lower bound  $b$  of  $\mathcal{A}$ . The concept of *upper bound* and *least upper bound* of  $\mathcal{A}$ , written  $lub(\mathcal{A})$ , are defined dually. If  $\mathcal{A} = \{a, b\}$ , we will write  $glb(a, b)$  ( $lub(a, b)$ ) rather than  $glb(\{a, b\})$  ( $lub(\{a, b\})$ ). Clearly, if  $glb(\mathcal{A})$  exists, it is unique, and the same holds for  $lub(\mathcal{A})$ .

A poset  $\langle \mathcal{S}, \sqsubseteq \rangle$  is said to have a *universal lower bound*  $\perp \in \mathcal{S}$  iff  $\perp \sqsubseteq a$  for every element  $a \in \mathcal{S}$ . A poset is said to have a *universal upper bound*  $\top \in \mathcal{S}$  iff  $a \sqsubseteq \top$  for every element  $a \in \mathcal{S}$ .

A poset  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a *complete lattice* if  $lub(\mathcal{A})$  and  $glb(\mathcal{A})$  exist for every subset  $\mathcal{A} \subseteq \mathcal{S}$ . Given that  $\mathcal{S}$  is a finite set, one can show [37] that if  $lub(a, b)$  and  $glb(a, b)$  exist for every  $a, b \in \mathcal{S}$ , then  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a complete lattice. Note that, by definition, every complete lattice has a universal upper bound  $\top \in \mathcal{S}$  and a universal lower bound  $\perp \in \mathcal{S}$ .

If  $\langle \mathcal{S}_1, \sqsubseteq_1 \rangle, \dots, \langle \mathcal{S}_n, \sqsubseteq_n \rangle$  are  $n$  complete lattices let  $\mathcal{S} = \mathcal{S}_1 \times \dots \times \mathcal{S}_n$  and for any  $a, b \in \mathcal{S}$  let  $a \sqsubseteq b$  iff  $a_i \sqsubseteq_i b_i$  for  $1 \leq i \leq n$ . It is easy to verify that  $\langle \mathcal{S}, \sqsubseteq \rangle$  forms a complete lattice.

A *mapping*  $f: \mathcal{A} \rightarrow \mathcal{B}$  consists of a function  $f$  assigning an element  $b$  from the *codomain*  $\mathcal{B}$  to each element  $a$  of its *domain*  $\mathcal{A}$ , written as  $b = f(a)$ .

Given a poset  $\langle \mathcal{S}, \sqsubseteq \rangle$  and a mapping  $f: \mathcal{S} \rightarrow \mathcal{S}$ , we say that  $f$  is *monotone* iff

$$a \sqsubseteq b \implies f(a) \sqsubseteq f(b)$$

This monotonicity definition is consistent with our use of information content. If a mapping is monotone, we cannot “gain” any information by reducing the information content of the arguments to the function.

A *predicate* over  $\mathcal{S}$  is a special type of mapping  $\mathcal{S}$  to the complete lattice with elements *false* and *true*, with *false* as the universal lower bound and *true* as the universal upper bound. A predicate  $p$  is said to be *simple* iff  $p$  is monotone and there is a unique element  $\bar{p} \in \mathcal{S}$ , called the *defining value*, such that  $p(t) = \text{true}$  iff  $\bar{p} \sqsubseteq t$  for all  $t \in \mathcal{S}$ . Another way of stating this property is that  $p$  is a simple predicate iff  $p$  is monotone and  $p(glb(\{s \in \mathcal{S} | p(s) = \text{true}\})) = \text{true}$ .

A fixed-point of a mapping  $f: \mathcal{S} \rightarrow \mathcal{S}$  is a value  $a$  such that  $a = f(a)$ . Furthermore, if  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a complete lattice and  $f$  is monotone, then the mapping has a unique *greatest fixed-point*, i.e., a fixed-point  $a$  such that  $a' \sqsubseteq a$  for any other fixed-point  $a'$ . This fixed-point is denoted  $Gfp\ a.\ f(a)$ . Furthermore, for the case where  $\mathcal{S}$  is finite, this fixed-point can be derived by iteratively computing  $a^0 = \top$ , and  $a^i = f(a^{i-1})$  for  $i > 0$ . Eventually some iteration step will yield  $a^i = a^{i-1}$ ; this value is the greatest fixed-point [37].

To express the behavior of a system working over time, we will reason about *sequences* of elements from some set  $\mathcal{S}$ . Conceptually, we will consider the sequences to be infinite, although the properties we will express can always be determined from some bounded length prefix of the sequence. Given a poset  $\langle \mathcal{S}, \sqsubseteq \rangle$ , we extend the relation  $\sqsubseteq$  to sequences pointwise. That is, if  $\sigma = \sigma^0 \sigma^1 \dots$  and  $\tau = \tau^0 \tau^1 \dots$  are two infinite sequences of elements from  $\mathcal{S}$ , then  $\sigma \sqsubseteq \tau$  iff  $\sigma^i \sqsubseteq \tau^i$  for  $i \geq 0$ . Similarly, the definitions of *lub* and *glb* are extended pointwise. Finally, for notational convenience, if  $\sigma = \sigma^0 \sigma^1 \sigma^2 \dots$  we will often write  $\sigma$  as  $\sigma^0 \tilde{\sigma}$ , where  $\tilde{\sigma} = \sigma^1 \sigma^2 \dots$ .

### 3 Model Structure

The model we use of a system is simple and general. A *model structure* is a tuple  $\mathcal{M} = [\langle \mathcal{S}, \sqsubseteq \rangle, Y]$ , where  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a complete lattice and  $Y$  is a monotone successor function  $Y: \mathcal{S} \rightarrow \mathcal{S}$ . Intuitively, the successor function is used to express constraints on the permissible sequences. In other words, given that the system is in state  $s \in \mathcal{S}$ , we view  $Y(s)$  as denoting the least specified state the system can be in one time unit later. Here, “least specified” is defined in terms of the partial order  $\sqsubseteq$ .

#### 3.1 Structure Example

In order to make the theory easier to follow but also to provide a concrete application for the general theory, we will use switch-level circuit verification as a running example throughout the paper. There are several reasons for this. First, there is a historical reason since this work grew out of switch-level simulation and verification. Secondly, there is a very close connection between our notion of a model structure and the type of models that are used in switch-level simulation. Nonetheless, the underlying concepts apply to more general classes of systems, examples of which will be given later.

In switch-level models it is useful to allow each circuit node to take on one of three distinct values. Let  $\mathcal{T} = \{0, 1, X\}$  denote such a set of values. There are several advantages in extending the domain from  $\{0, 1\}$  to  $\mathcal{T}$ . As a first advantage, this extension makes it possible to model an increased range of circuit phenomena. For example, we can deal with circuits in which nondigital voltages are generated in the course of normal circuit operation. This occurs frequently when modeling circuits at the switch-level [8], due to (generally transient) short circuits or charge sharing. We can also deal with circuits in which indeterminate behavior occurs due either to timing hazards or to circuit oscillation. In all of these cases, the modeling algorithm expresses this uncertainty by assigning a value  $X$  to the offending circuit nodes, indicating that the actual digital value cannot be determined [14, 28]. Thus the value  $X$  is introduced to denote an “unknown” and possibly indeterminate value.

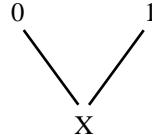

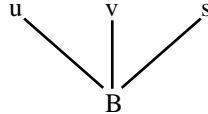

Figure 1: The  $\leq$  partial order.

In order to formalize this concept of an “unknown” value, define the partial order  $\leq$  on  $\mathcal{T}$  as follows:  $a \leq a$  for all  $a \in \mathcal{T}$ ,  $X \leq 0$ , and  $X \leq 1$ . In Fig. 1 we show the Hasse diagram for the partial order. We can view this partial ordering as ordering values by their “information content.” That is,  $X$  indicates an absence of information while 0 and 1 represent specific, fully-defined values.

Let  $\mathcal{T}^m$ ,  $m \geq 1$ , denote the set of all possible vectors of ternary values of length  $m$ , i.e.,  $\{\langle a_1, \dots, a_m \rangle | a_i \in \mathcal{T}, 1 \leq i \leq m\}$ . The partial order  $\leq$  is extended to  $\mathcal{T}^m$  pointwise:  $\vec{a} \leq \vec{b}$  iff  $a_i \leq b_i$  for  $1 \leq i \leq m$ . Unfortunately,  $\langle \mathcal{T}^m, \leq \rangle$  is not a complete lattice, since the least upper bound does not exist for every pair of elements in  $\mathcal{T}^m$ . We solve this by introducing a new top element. In other words, let  $\mathcal{C} = \mathcal{T}^m \cup \{\top\}$ . Intuitively, one can view  $\top$  as representing an “overconstrained” state, i.e., a state vector in which some node is both 0 and 1 at the same time. Let  $\sqsubseteq$  be the partial order on  $\mathcal{C}$  defined as follows:  $s \sqsubseteq \top$  for every  $s \in \mathcal{C}$  and if  $\vec{s}, \vec{t} \in \mathcal{T}^m$  then

$\vec{s} \sqsubseteq \vec{t}$  iff  $\vec{s} \leq \vec{t}$ . Clearly,  $(\mathcal{C}, \sqsubseteq)$  forms a complete lattice in which  $\perp = X, \dots, X$ . Thus we now have the first half of a model structure.

The underlying model of a switch-level circuit we use is quite simple, as well as general. A circuit is a tuple  $(\mathcal{N}, \vec{y})$ , where  $\mathcal{N}$  is a set of nodes and  $\vec{y}$  is a vector of excitation, or next-state, functions. In the mathematical presentation we will refer to the nodes as  $n_1, n_2, \dots, n_m$ , whereas in our examples we often will use more descriptive names.

Since  $X$  is meant to denote an unknown value, a gate with an  $X$  on its input must treat this value in a conservative way. Consequently, the excitation functions are required to be monotone with respect to the partial order  $\leq$ . This monotonicity requirement is consistent with our use of information content. If a function is monotone, we cannot “gain” any information by reducing the information content of the arguments to the function. In other words, changing some signals from binary values to  $X$  will either have no effect on the next-state values, or it will change some binary values to  $X$ .

The excitation functions are defined in a non-traditional way. We view them as expressing “constraints” on the values the nodes can take on one time unit later given the current values on the nodes. By constraint we mean specific binary values, whereas the value  $X$  indicates that no constraint is imposed. Since the value of an input is controlled by the external environment, the circuit itself does not impose any constraint on the value; hence the excitation of an “input node” is  $X$ . More formally, if node  $n_i$  corresponds to an input to the circuit then  $y_{n_i}(\vec{a}) = X$  for every  $\vec{a} \in \mathcal{T}^m$ . Nodes that do not correspond to inputs are called *function nodes*. For a function node  $n_i$  the excitation function is a monotone ternary function  $y_{n_i}: \mathcal{T}^m \rightarrow \mathcal{T}$  determined by the circuit topology and functionality.

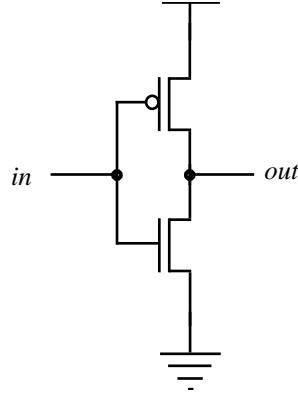

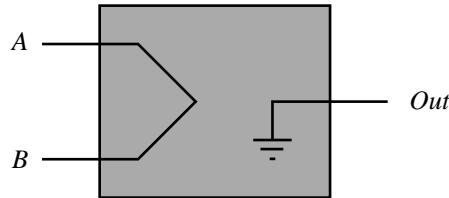

Figure 2: CMOS inverter.

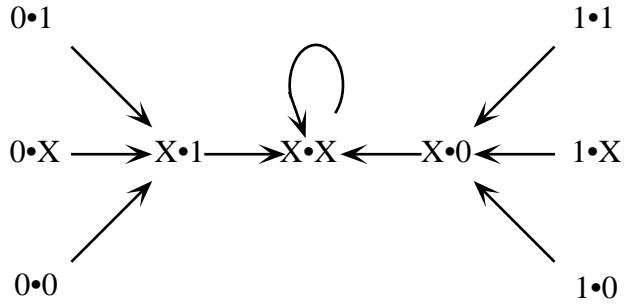

To illustrate our notion of excitation function, consider the CMOS circuit shown in Fig. 2. In Fig. 3 we give a graphical representation of the next-state function assuming the circuit behavior is analyzed using a unit-delay model. Note that no matter what the current state is, the next-state function for the input is  $X$ . Also, if the current input is binary, it is easy to see that the output one time unit later will be the complement of this value.

It should be pointed out that the “time unit” referred to above is the smallest period of time that is distinguishable in the circuit model. The minimum delay in any individual component of the circuit can be significantly larger. Thus we are not limited to unit delay circuit models. For example, by using the transformation technique described in [34], both nominal delay and bounded delay circuit models can be used. However, to make our example as simple as possible, we will use

Figure 3: Excitation function of unit delay inverter ( $in \cdot out$ ).

a unit delay model unless otherwise stated.

In order to obtain a model structure, we only need to define a monotone next time function mapping  $\mathcal{C}$  to  $\mathcal{C}$ . We do this by extending  $\vec{y}$  from  $\mathcal{T}^m \rightarrow \mathcal{T}^m$  to  $\mathcal{C} \rightarrow \mathcal{C}$  in the obvious way. Thus define:

$$Y(a) = \begin{cases} \vec{y}(a) & \text{if } a \in \mathcal{T}^m \\ \top & \text{otherwise} \end{cases}$$

Clearly,  $Y$  is monotone and thus  $\mathcal{M}^C = [\langle \mathcal{C}, \sqsubseteq \rangle, Y]$  forms a model structure.

### 3.2 Trajectories

Let us now return to the more general theory in which  $[\langle \mathcal{S}, \sqsubseteq \rangle, Y]$  is any model structure. Let  $\mathcal{S}^\omega$  denote the set of all infinite sequences of elements from  $\mathcal{S}$ . In general, sequences are useful when reasoning about model behaviors. However, not all sequences represent possible behaviors of a model. The successor function generally restricts the possible sequences significantly. We formalize this property by introducing the concept of a trajectory. Given a model  $\mathcal{M}$  and an arbitrary sequence  $\sigma = \sigma^0 \sigma^1 \dots \in \mathcal{S}^\omega$  we say that the sequence is a *trajectory* if and only if

$$Y(\sigma^i) \subseteq \sigma^{i+1} \text{ for } i \geq 0.$$

This rule for trajectories is consistent with our view of the successor function, i.e., a function computing a constraint on the possible value of the successor state. Another way of describing the next-state function is to view it as computing the most general state the system can evolve into during the next time step given its current state.

The set of all trajectories of model  $\mathcal{M}$  is denoted  $L(\mathcal{M})$ . Occasionally it is convenient to restrict the set of trajectories by requiring the first state in the trajectory to be greater than or equal to some element in  $\mathcal{S}$ . Consequently, define

$$L(\mathcal{M}, z) = \{\sigma^0 \sigma \mid \sigma^0 \sigma \in L(\mathcal{M}) \text{ and } z \sqsubset \sigma^0\}.$$

Note that  $L(\mathcal{M}, \perp) \equiv L(\mathcal{M})$ .

The following proposition follows trivially from the definition of trajectories:

**Proposition 1** *If  $\sigma = \sigma^0\sigma^1\sigma^2\dots \in L(\mathcal{M})$  then  $\sigma^1\sigma^2\dots \in L(\mathcal{M})$ . In other words, the set  $L(\mathcal{M})$  is suffix-closed, i.e. every suffix of every trajectory in  $L(\mathcal{M})$  is also in  $L(\mathcal{M})$ .*

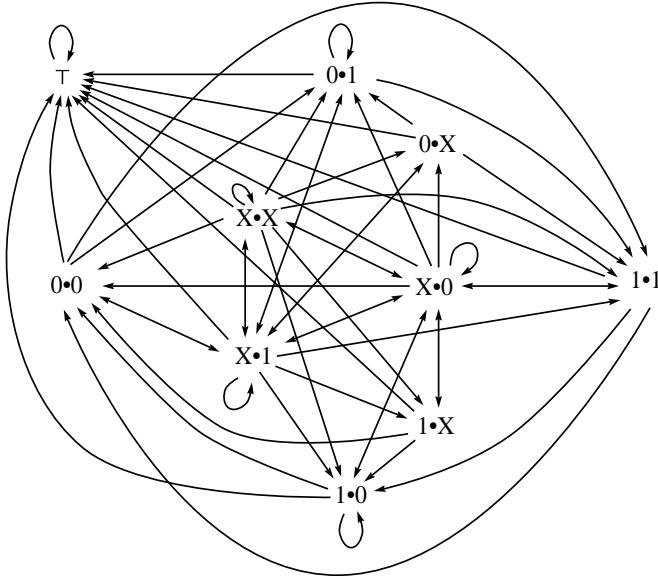

Figure 4:  $L(\mathcal{M}^C)$  for a unit delay inverter.

Another way of stating Proposition 1 is to say that we assume that every state in  $\mathcal{S}$  is a possible initial state of the system.

In Fig. 4 we illustrate the set of all trajectories ( $L(\mathcal{M}^C)$ ) for the unit delay inverter described earlier. In this figure, the set of labels encountered while traversing any infinite path in the graph denotes a trajectory. Before discussing this graph further, recall that the  $T$  state is used to represent overconstrained states. In a matter of speaking, we consider that `in` is both 0 and 1 at the same time in the state  $T$ . A similar remark holds for `out`. In view of this interpretation, we can draw several conclusions from the graph. For example, we can see that for every trajectory  $\sigma^0\sigma^1\dots$  such that `in` is 1 in  $\sigma^0$  we have that `out` is 0 in  $\sigma^1$ . The same statement holds with 0 replaced by 1 and 1 replaced by 0. At its core, our verification methodology establishes properties such as these for a given model structure. More specifically, in the next section we define a small logic that allows us to state properties like the ones above in a concise and unambiguous way. We then define an efficient way of determining whether the formulas in the logic are valid for a particular model structure. One main contribution of the paper is the development of a checking algorithm that only needs to explore a tiny fraction of the complete state graph as opposed to how it is shown in Fig. 4.

## 4 Specification Language

The basic specification language we use is very simple. In fact, at a first glance it might appear as if it can only be used to specify rather trivial behaviors. However, this is a bit of an illusion. In particular, we will later in the paper extend the model structure to a symbolic domain and give several examples of how non-trivial behaviors can be specified in this language. By keeping the language simple, we gain some very important properties. The most important is that there is a unique weakest trajectory that satisfies a formula. By focusing initially on the scalar version, we avoid the added complexity of the symbolic case while building a foundation upon which this more general formulation can be based.

Assume  $\langle \mathcal{S}, \sqsubseteq \rangle$  is a lattice with universal lower bound  $\perp$ . Let  $\mathcal{P}$  denote a set of simple predicates over  $\mathcal{S}$ . A *trajectory formula* is defined recursively as:

1. **Simple predicates:**  $p$  is a trajectory formula if  $p \in \mathcal{P}$ .

2. **Conjunction:**  $(F_1 \wedge F_2)$  is a trajectory formula if  $F_1$  and  $F_2$  are trajectory formulas.

3. **Domain restriction:**  $(e \rightarrow F)$  is a trajectory formula if  $F$  is a trajectory formula and  $e$  is either 0 or 1.

4. **Next time:**  $(\mathbf{NF})$  is a trajectory formula if  $F$  is a trajectory formula.

A trajectory formula is said to be *instantaneous* if it contains no next-time operators. Such a formula expresses system properties at only a single point in time. For convenience, we often drop parentheses when the intended precedence is clear. The domain restriction appears at first somewhat strange. Its usefulness will not become apparent until later when we extend the trajectory formulas to a symbolic domain. Observe also that our language does not include either disjunction or negation operations. The motivation and implications of this restriction will be discussed later.

The set of simple predicates is arbitrary. However, for convenience, we will always assume that the predicate  $p_0(s) \equiv \text{true}$  is in  $\mathcal{P}$ . Observe that  $p_0$  is indeed a simple predicate with defining value  $\perp$ .

In switch-level verification the natural simple predicates are of the following form:

1.  $(n_i \mathbf{is} 0)$  where  $n_i \in \mathcal{N}$ , and

2.  $(n_i \mathbf{is} 1)$  where  $n_i \in \mathcal{N}$ .

In other words, our simple predicates ask whether a node in the circuit is known to be 0 or 1. It is easy to see that  $(n_i \mathbf{is} 0)$  and  $(n_i \mathbf{is} 1)$  are indeed simple with defining values

$$\langle X, \dots, X, 0, X, \dots, X \rangle$$

and

$$\langle X, \dots, X, 1, X, \dots, X \rangle,$$

where the 0 (1) is in position  $i$ . The only somewhat strange property of these predicates is that they are both true in the (artificially introduced)  $\top$  state. We ask the reader to simply accept this for the time being. We will discuss the ramifications of this later. For our example circuit of Fig. 2 we will use the five simple predicates: *true*, *in is 0*, *in is 1*, *out is 0*, and *out is 1* with defining values  $\langle XX \rangle$ ,  $\langle 0X \rangle$ ,  $\langle 1X \rangle$ ,  $\langle X0 \rangle$ , and  $\langle X1 \rangle$  respectively.

A trajectory formula describes constraints on some prefix of a trajectory. In order to refer to the length of this prefix, we introduce the concept of “depth” for trajectory formulas. The *depth* of a formula  $F$ , written  $d(F)$ , is defined recursively.

1.  $d(p) = 1$  if  $p \in \mathcal{P}$  is a simple predicate.

2.  $d(F_1 \wedge F_2) = \max(d(F_1), d(F_2))$ .

3.  $d(e \rightarrow F) = d(F)$ .

4.  $d(\mathbf{NF}) = 1 + d(F)$ .

The depth of a formula is simply the maximum number of nested next time operators plus one.

As a notational convenience, we define for any trajectory formula  $F$

$$F^{[i]} = \begin{cases} F & \text{if } i = 1 \\ F \wedge \mathbf{N}^{d(F)}(F^{[i-1]}) & \text{otherwise,} \end{cases}$$

where  $\mathbf{N}^k F$  denotes  $(\mathbf{N}(\mathbf{N}(\dots(F)\dots)))$  with  $k$  next-time operators. This notation allows us to express a condition that repeats over time. For example, the formula  $(\text{in is } 0)^{[3]}$  states that node `in` stays at 0 for 3 consecutive time units. This is more concise than writing out the formula as  $(\text{in is } 0) \wedge \mathbf{N}(\text{in is } 0) \wedge \mathbf{N}(\mathbf{N}(\text{in is } 0))$ .

For our example circuit of Fig. 2 we can thus write trajectory formulas like:

$$(\text{in is } 0) \wedge \mathbf{N}(\text{out is } 1)$$

and

$$(0 \rightarrow ((\text{in is } 0) \wedge \mathbf{N}(\text{out is } 1))) \wedge (1 \rightarrow ((\text{in is } 1) \wedge \mathbf{N}(\text{out is } 0))).$$

The truth semantics of a trajectory formula is defined relative to a model structure and a trajectory. In particular, given a model structure  $\mathcal{M}$  and a trajectory  $\sigma$ , the truth of a trajectory formula  $F$ , written  $\sigma \models_{\mathcal{M}} F$ , is defined recursively. In the following, assume that both  $\sigma$  and  $\sigma^0 \tilde{\sigma}$  are members of  $L(\mathcal{M})$ .

1.  $\sigma^0 \tilde{\sigma} \models_{\mathcal{M}} p$  iff  $p(\sigma^0) = \text{true}$ .

2.  $\sigma \models_{\mathcal{M}} (F_1 \wedge F_2)$  iff  $\sigma \models_{\mathcal{M}} F_1$  and  $\sigma \models_{\mathcal{M}} F_2$

3. (a)  $\sigma \models_{\mathcal{M}} (1 \rightarrow F)$  iff  $\sigma \models_{\mathcal{M}} F$

(b)  $\sigma \models_{\mathcal{M}} (0 \rightarrow F)$  holds for every  $\sigma$ .

4.  $\sigma^0 \tilde{\sigma} \models_{\mathcal{M}} \mathbf{N}F$  iff  $\tilde{\sigma} \models_{\mathcal{M}} F$ .

For example, given the trajectory  $\sigma = \langle 00 \rangle \langle 01 \rangle \langle XX \rangle \langle XX \rangle \dots$  for the circuit shown in Fig. 2, it is easy to verify that  $\sigma \models_{\mathcal{M}} (\text{in is } 0) \wedge \mathbf{N}(\text{in is } 0)$ , but that

$$\sigma \not\models_{\mathcal{M}} (0 \rightarrow ((\text{in is } 0) \wedge \mathbf{N}(\text{out is } 1))) \wedge (1 \rightarrow ((\text{in is } 1) \wedge \mathbf{N}(\text{out is } 0))).$$

## 5 Properties of Trajectory Formulas

We can extend the definition of simplicity from predicates to formulas in the obvious way, i.e., given a model structure  $\mathcal{M}$ , a formula  $F$  is said to be *simple* iff there is a *defining trajectory*  $\bar{\sigma} \in L(\mathcal{M})$  such that  $\sigma \models_{\mathcal{M}} F$  iff  $\bar{\sigma} \sqsubseteq \sigma$ . In this section we first show that trajectory formulas are simple. We then show how the defining sequence can be constructed. The construction is direct and very efficient. As a result, if the main verification task can be phrased in terms of “for every trajectory  $\sigma$  that satisfies the trajectory formula  $A$ , verify that the trajectory also satisfies the formula  $C$ ”, it becomes obvious how the verification can be carried out: compute the defining trajectory for the formula  $A$  and check that the formula  $C$  holds for this trajectory.

Before we can continue, we need a monotonicity result for trajectory formulas. The following lemma states that if a trajectory formula holds for some trajectory  $\sigma$ , then it also holds for every trajectory  $\tau$  such that  $\sigma \sqsubseteq \tau$ .

**Lemma 1** *If  $\sigma, \tau \in L(\mathcal{M})$  and  $\sigma \sqsubseteq \tau$  then*

$$\sigma \models_{\mathcal{M}} F \implies \tau \models_{\mathcal{M}} F$$

**Proof:** We prove the claim by induction on the formula structure. For the basis case, if  $F = p$ , for some simple predicate  $p \in \mathcal{P}$  with defining value  $\bar{p}$ , then if  $\sigma = \sigma^0 \tilde{\sigma}$  and  $\sigma \models_{\mathcal{M}} F$  it follows from the truth semantics of  $F$  that  $p(\sigma^0) = \text{true}$ . By the definition of a simple predicate it thus follows that  $\bar{p} \sqsubseteq \sigma^0$ . If  $\tau = \tau^0 \tilde{\tau}$  it follows from the fact that  $\sigma \sqsubseteq \tau$  that  $\bar{p} \sqsubseteq \sigma^0 \sqsubseteq \tau^0$ . Hence, we can conclude that  $\tau^0 \tilde{\tau} \models_{\mathcal{M}} F$ .

If  $F = (F_1 \wedge F_2)$  then  $\sigma \models_{\mathcal{M}} F$  implies that  $\sigma \models_{\mathcal{M}} F_1$  and  $\sigma \models_{\mathcal{M}} F_2$ . Assuming inductively that the claim holds for the formulas  $F_1$  and  $F_2$ , it follows that  $\tau \models_{\mathcal{M}} F_1$  and that  $\tau \models_{\mathcal{M}} F_2$ . This, together with the truth semantics for  $F$ , imply that  $\tau \models_{\mathcal{M}} F$ .

If  $F = (1 \rightarrow F_1)$  and  $\sigma \models_{\mathcal{M}} F$  then, by the truth semantics, it follows that  $\sigma \models_{\mathcal{M}} F_1$ . Assuming inductively that the claim holds for  $F_1$ , i.e., that  $\tau \models_{\mathcal{M}} F_1$ , it follows directly that  $\tau \models_{\mathcal{M}} F$ . On the other hand, if  $F = (0 \rightarrow F_1)$  then the claim follows trivially since  $(0 \rightarrow F_1)$  holds for every trajectory in  $L(\mathcal{M})$ .

Finally, if  $F = \mathbf{N}F_1$  then, by the truth semantics,  $\sigma^0 \tilde{\sigma} \models_{\mathcal{M}} F$  implies that  $\tilde{\sigma} \models_{\mathcal{M}} F_1$ . Assuming inductively that the claim holds for  $F_1$ , i.e., that  $\tilde{\tau} \models_{\mathcal{M}} F_1$ , it follows immediately that  $\tau^0 \tilde{\tau} \models_{\mathcal{M}} F$ .  $\square$

Before stating our next result, it is convenient to introduce an infix ‘‘choice’’ function mapping  $\{0, 1\} \times \mathcal{S}^\omega$  to  $\mathcal{S}^\omega$  and which is defined as:

$$e? \delta = \begin{cases} \delta & \text{if } e = 1 \\ \perp \perp \dots & \text{otherwise} \end{cases}$$

We now show that given a trajectory formula  $F$  we can construct its *defining sequence*  $\delta_F$ . This sequence is the weakest possible in the sense that  $\sigma \models_{\mathcal{M}} F$  iff  $\delta \sqsubseteq \sigma$ . Note that  $\delta_F$  is not necessarily a trajectory. We define  $\delta_F$  recursively as follows:

1.  $\delta_p = \bar{p} \perp \perp \dots$  if  $p \in \mathcal{P}$  is a simple predicate with defining value  $\bar{p}$ .

2.  $\delta_{F_1 \wedge F_2} = \text{lub}(\delta_{F_1}, \delta_{F_2})$ .

3.  $\delta_{e \rightarrow F} = e? \delta_F$ .

4.  $\delta_{\mathbf{N}F} = \perp \delta_F$ .

For the particular case of switch-level verification and the model structure  $\mathcal{M}^C$ , consider the trajectory formula:  $F = (\text{in is } 0) \wedge \mathbf{N}(\text{in is } 0)$ . It is straightforward to see that

$$\begin{aligned} \delta_{\text{in is } 0} &= \langle 0X \rangle \langle XX \rangle \langle XX \rangle \dots \\ \delta_{\mathbf{N}(\text{in is } 0)} &= \langle XX \rangle \langle 0X \rangle \langle XX \rangle \langle XX \rangle \dots \\ \delta_{(\text{in is } 0) \wedge \mathbf{N}(\text{in is } 0)} &= \langle 0X \rangle \langle 0X \rangle \langle XX \rangle \langle XX \rangle \dots \end{aligned}$$

Note that  $\delta_F$  is not a trajectory as can be seen from Fig. 4. However, it is clearly smaller than several trajectories. For example,  $\delta_F \sqsubseteq \langle 0X \rangle \langle 01 \rangle \langle X1 \rangle \langle XX \rangle \dots$  and  $\delta_F \sqsubseteq \langle 0X \rangle \langle 01 \rangle \langle 01 \rangle \langle X1 \rangle \langle XX \rangle \dots$

Our prohibition of disjunction and negation is partially justified by our desire to have a unique weakest sequence for each formula. For example, we can find a sequence weaker than any other sequence satisfying the formula  $F = (\text{in is } 0) \vee \mathbf{N}(\text{in is } 0)$  by taking the greatest lower bound of the sequences for  $(\text{in is } 0)$  and  $\mathbf{N}(\text{in is } 0)$ . This would yield the sequence  $\langle XX \rangle \langle XX \rangle \langle XX \rangle \dots$ . Unfortunately, this sequence does not itself satisfy  $F$ , and hence the verifier would yield overly

pessimistic results. One can also see that there is no unique weakest sequence satisfying the formula  $\neg(\text{in is } 0)$ . More typically, the user really wants to use the formula  $(\text{in is } 1)$ , in any case, and hence this restriction is not as serious as it may initially seem.

In general, we have the following result.

**Lemma 2** *For any trajectory formula  $F$  let  $\delta_F$  be constructed as above. Then for every  $\sigma \in L(\mathcal{M})$*

$$\sigma \models_{\mathcal{M}} F \iff \delta_F \sqsubseteq \sigma$$

**Proof:** Assume that  $\sigma \in L(\mathcal{M})$ ,  $\sigma \models_{\mathcal{M}} F$ , and that  $\sigma = \sigma^0 \tilde{\sigma}$ . We first prove that  $\delta_F \sqsubseteq \sigma$  by induction on the formula structure.

For the basis, if  $F = p$ , for some simple predicate  $p \in \mathcal{P}$  with defining value  $\bar{p}$ , then, by definition,  $\sigma^0 \tilde{\sigma} \models_{\mathcal{M}} F$  implies that  $\bar{p} \sqsubseteq \sigma^0$ . Since  $\delta_F = \bar{p} \perp \perp \dots \sqsubseteq \sigma^0 \tilde{\sigma} = \sigma$ , the basis holds. Thus assume inductively that the claim holds for formulas  $F_1$  and  $F_2$ .

If  $F = (F_1 \wedge F_2)$  then  $\sigma \models_{\mathcal{M}} F$  implies that  $\sigma \models_{\mathcal{M}} F_1$  and  $\sigma \models_{\mathcal{M}} F_2$ . By the induction hypothesis it thus follows that  $\delta_{F_1} \sqsubseteq \sigma$  and that  $\delta_{F_2} \sqsubseteq \sigma$ . Hence,  $\sigma$  is an upper bound on both  $\delta_{F_1}$  and  $\delta_{F_2}$ . Consequently,  $\sigma$  is also an upper bound on  $\text{lub}(\delta_{F_1}, \delta_{F_2})$ , i.e.,  $\delta_F = \text{lub}(\delta_{F_1}, \delta_{F_2}) \sqsubseteq \sigma$ , and the claim follows.

If  $F = (1 \rightarrow F)$  then  $\sigma \models_{\mathcal{M}} F$  implies that  $\sigma \models_{\mathcal{M}} F_1$ , and thus, by the inductive assumption, that  $\delta_{F_1} \sqsubseteq \sigma$ . However, by definition,  $\delta_F = \delta_{F_1}$  and the result follows. On the other hand, if  $F = (0 \rightarrow F)$  then  $\delta_F = \perp \perp \dots$  and the result follows trivially.

Finally, if  $F = \mathbf{N}F_1$  then  $\sigma^0 \tilde{\sigma} \models_{\mathcal{M}} F$  implies that  $\tilde{\sigma} \models_{\mathcal{M}} F_1$ . By Proposition 1 it follows that  $\tilde{\sigma} \in L(\mathcal{M})$ . Therefore, by the induction hypothesis, it follows that  $\delta_{F_1} \sqsubseteq \tilde{\sigma}$ . Since  $\delta_F = \perp \delta_{F_1} \sqsubseteq \sigma^0 \tilde{\sigma}$  the result follows, and the induction step goes through.

Conversely, we now show that if  $\sigma = \sigma^0 \tilde{\sigma}$  is a trajectory in  $L(\mathcal{M})$  and  $\delta_F \sqsubseteq \sigma$ , then  $\sigma \models_{\mathcal{M}} F$ . Again, we show this by induction on the structure of  $F$ .

For the basis, if  $F = p$ , for some simple predicate  $p \in \mathcal{P}$  with defining value  $\bar{p}$ , then, by definition,  $\delta_F = \bar{p} \perp \perp \dots$ . Since, by assumption,  $\delta_F \sqsubseteq \sigma^0 \tilde{\sigma}$  it follows that  $\bar{p} \sqsubseteq \sigma^0$  and thus that  $\sigma \models_{\mathcal{M}} F$  and the basis holds. Hence, assume inductively that  $\delta_{F_1} \sqsubseteq \sigma$  and  $\delta_{F_2} \sqsubseteq \sigma$  implies  $\sigma \models_{\mathcal{M}} F_1$  and  $\sigma \models_{\mathcal{M}} F_2$ .

If  $F = (F_1 \wedge F_2)$  then  $\delta_F = \text{lub}(\delta_{F_1}, \delta_{F_2})$ . This together with the assumption  $\delta_F \sqsubseteq \sigma$  and the definition of  $\text{lub}$  imply that  $\delta_{F_1} \sqsubseteq \sigma$  and that  $\delta_{F_2} \sqsubseteq \sigma$ . Hence, by the induction hypothesis,  $\sigma \models_{\mathcal{M}} F_1$  and  $\sigma \models_{\mathcal{M}} F_2$ . By the truth semantics it thus follows that  $\sigma \models_{\mathcal{M}} F$ .

If  $F = (1 \rightarrow F)$  then  $\delta_F = \delta_{F_1}$ . Since, by assumption,  $\delta_F \sqsubseteq \sigma$  it follows that  $\delta_{F_1} \sqsubseteq \sigma$ . Hence, by the induction hypothesis, it follows that  $\sigma \models_{\mathcal{M}} F_1$ . Together with the truth semantics we can conclude that  $\sigma \models_{\mathcal{M}} F$ . On the other hand, if  $F = (0 \rightarrow F)$  then the result holds trivially since  $\sigma \models_{\mathcal{M}} F$  holds for every  $\sigma \in L(\mathcal{M})$ .

Finally, if  $F = \mathbf{N}F_1$  then  $\delta_F = \perp \delta_{F_1}$ . Since, by assumption,  $\delta_F \sqsubseteq \sigma = \sigma^0 \tilde{\sigma}$  it thus follows that  $\delta_{F_1} \sqsubseteq \tilde{\sigma}$  and thus, by the induction hypothesis, that  $\tilde{\sigma} \models_{\mathcal{M}} F_1$ . Consequently, by the truth semantics, we can conclude that  $\sigma \models_{\mathcal{M}} F$  and the induction goes through and the claim follows.  $\square$

From the above lemma we know that any trajectory satisfying  $F$  must be greater than or equal to its defining sequence  $\delta_F$ . Thus computing  $\delta_F$  and then determining if a trajectory is greater than or equal to  $\delta_F$  allows us to quickly test whether the trajectory satisfies the formula  $F$ . However,  $\delta_F$  is not necessarily itself a trajectory. In the following we will show how to combine the constraints on a state sequence implied by  $\delta_F$  with those imposed by the system's excitation function to give a trajectory. In fact, we will show that the obtained trajectory is the weakest possible trajectory satisfying  $F$ .

It turns out that a slightly more general concept than a defining trajectory is often useful. Thus, assume  $\delta_F = \delta_F^0 \delta_F^1 \dots$  is the defining sequence for a formula  $F$ . Define  $\tau_F(z) = \tau_F^0(z) \tau_F^1(z) \dots$  inductively as follows:

$$\tau_F^i(z) = \begin{cases} \text{lub}(\delta_F^0, z) & \text{if } i = 0 \\ \text{lub}(\delta_F^i, Y(\tau_F^{i-1}(z))) & \text{otherwise} \end{cases}$$

To illustrate the above construction, let us return to the trajectory formula

$$F = (\text{in is } 0) \wedge \mathbf{N}(\text{in is } 0)$$

with defining sequence  $\delta_F = \langle 0X \rangle \langle 0X \rangle \langle XX \rangle \langle XX \rangle \dots$ . Assume we would like to compute  $\tau_F(\perp) = \tau_F(XX)$ . From the construction above, it follows immediately that

$$\begin{aligned} \tau_F^0(\perp) &= 0X \\ \tau_F^1(\perp) &= \text{lub}(\delta_F^1, Y(0X)) = \text{lub}(0X, X1) = 01 \\ \tau_F^2(\perp) &= \text{lub}(\delta_F^2, Y(01)) = \text{lub}(XX, X1) = X1 \\ \tau_F^3(\perp) &= \text{lub}(\delta_F^3, Y(X1)) = \text{lub}(XX, XX) = XX \\ \tau_F^i(\perp) &= XX \text{ for } i \geq 4 \end{aligned}$$

and thus that  $\tau_F(\perp) = \langle 0X \rangle \langle 01 \rangle \langle X1 \rangle \langle XX \rangle \langle XX \rangle \dots$ . Note that from Fig. 4 we can immediately see that  $\tau_F(\perp)$  is a trajectory. It is more difficult to verify, but from Fig. 4 and the truth semantics of  $F$ , it can be seen that  $\tau_F(\perp)$  is the weakest trajectory that satisfies  $F$  and that every other trajectory that satisfies  $F$  is greater than  $\tau_F(\perp)$ . This is in fact no coincidence as we now show.

Before we establish the main properties of  $\tau_F(z)$ , the following monotonicity property will be needed.

**Lemma 3** *If  $s \sqsubseteq t$  then  $\tau_F(s) \sqsubseteq \tau_F(t)$ , for any trajectory formula  $F$ .*

**Proof:** We prove that  $\tau_F^i(s) \sqsubseteq \tau_F^i(t)$  by induction on  $i$ . For the base case we have that

$$\tau_F^0(s) = \text{lub}(s, \delta_F^0) \sqsubseteq \text{lub}(t, \delta_F^0) = \tau_F^0(t)$$

by the monotonicity of  $\text{lub}$ . Assume now inductively that  $\tau_F^i(s) \sqsubseteq \tau_F^i(t)$  for some  $i \geq 0$ . It follows from the definition of  $\tau_F^{i+1}(z)$ , the induction hypothesis, and the monotonicity of  $\text{lub}$  and  $Y$  that  $\tau_F^{i+1}(s) = \text{lub}(\delta_F^{i+1}, Y(\tau_F^i(s))) \sqsubseteq \text{lub}(\delta_F^{i+1}, Y(\tau_F^i(t))) = \tau_F^{i+1}(t)$  and the claim follows.  $\square$

The second key lemma of this section states that there is a defining trajectory for every trajectory formula  $F$  and start condition  $z$ . More formally:

**Lemma 4** *Assume  $\tau_F(z)$  is defined as above, then:*

1.  $\tau_F(z) \in L(\mathcal{M}, z)$ ,

2.  $\tau_F(z) \models_{\mathcal{M}} F$ , and

3. for every  $\sigma \in L(\mathcal{M}, z)$

$$\sigma \models_{\mathcal{M}} F \iff \tau_F(z) \sqsubseteq \sigma$$

**Proof:** In order to prove that  $\tau_F(z) \in L(\mathcal{M}, z)$  it is sufficient to show that  $z \sqsubseteq \tau_F^0(z)$  and that  $Y(\tau_F^{i-1}(z)) \sqsubseteq \tau_F^i(z)$  for  $i \geq 1$ . Since  $\tau_F^0(z) = \text{lub}(z, \delta_F^0)$ , we can immediately conclude that  $z \sqsubseteq \tau_F^0(z)$ . On the other hand, by the definition of  $\text{lub}$  it follows that for  $i \geq 1$ ,

$$Y(\tau_F^{i-1}(z)) \sqsubseteq \text{lub}(\delta_F^i, Y(\tau_F^{i-1}(z))).$$

However  $\tau_F^i(z) = lub(\delta_F^i, Y(\tau_F^{i-1}(z)))$ , and thus  $Y(\tau_F^{i-1}(z)) \sqsubseteq \tau_F^i(z)$  for  $i \geq 1$ . Altogether,  $\tau_F(z) \in L(\mathcal{M}, z)$ .

By the definition of *lub* it also follows that

$$\delta_F^i \sqsubseteq lub(\delta_F^i, Y(\tau_F^{i-1}(z))) = \tau_F^i(z) \quad \text{for } i \geq 1.$$

Hence,  $\delta_F \sqsubseteq \tau_F(z)$ . This, together with the fact that  $\tau_F(z) \in L(\mathcal{M}, z) \subseteq L(\mathcal{M})$ , means that Lemma 2 apply. Thus,  $\tau_F(z) \models_{\mathcal{M}} F$ .

Now assume  $\sigma \in L(\mathcal{M}, z)$ . Since  $\tau_F(z)$  is a trajectory and  $\tau_F(z) \models_{\mathcal{M}} F$  we can apply Lemma 1. Hence, if  $\tau_F(z) \sqsubseteq \sigma$  then  $\sigma \models_{\mathcal{M}} F$ .

Finally, we establish the converse by showing that for any  $\sigma \in L(\mathcal{M}, z)$ ,  $\tau_F(z) \sqsubseteq \sigma$ . Thus, assume  $\sigma = \sigma^0\sigma^1\dots$  is a trajectory,  $z \sqsubseteq \sigma^0$ , and that  $\sigma \models_{\mathcal{M}} F$ . We prove by induction on  $i$  that  $\tau_F^i(z) \sqsubseteq \sigma^i$ .

Since  $\sigma = \sigma^0\tilde{\sigma}$  is a trajectory, Lemma 2 applies. Consequently,  $\sigma^0\tilde{\sigma} \models_{\mathcal{M}} F$  implies that  $\delta_F = \delta_F^0\delta_F^1\dots \sqsubseteq \sigma^0\tilde{\sigma} = \sigma$ . Furthermore, since  $\sigma = \sigma^0\tilde{\sigma} \in L(\mathcal{M}, z)$  it follows that  $z \sqsubseteq \sigma^0$ . In other words,  $\sigma^0$  is an upper bound for both  $z$  and  $\delta_F^0$  and thus  $lub(z, \delta_F^0) \sqsubseteq \sigma^0$ . However, since  $\tau_F^0(z) = lub(z, \delta_F^0)$  it follows directly that  $\tau_F^0(z) \sqsubseteq \sigma^0$  and the basis case holds.

Now assume inductively that  $\tau_F^i(z) \sqsubseteq \sigma^i$  for some  $i > 0$ . Since  $\sigma$  is a trajectory, it follows that  $Y(\sigma^i) \sqsubseteq \sigma^{i+1}$ . Also, by Lemma 2 we know that  $\delta_F \sqsubseteq \sigma$  and thus that  $\delta_F^{i+1} \sqsubseteq \sigma^{i+1}$ . Together, these facts imply that  $\sigma^{i+1}$  is an upper bound to both  $Y(\sigma^i)$  and  $\delta_F^{i+1}$ . Consequently,  $lub(\delta_F^{i+1}, Y(\sigma^i)) \sqsubseteq \sigma^{i+1}$ . However, by the induction hypothesis,  $\tau_F^i(z) \sqsubseteq \sigma^i$ . Hence, by the monotonicity of  $Y$  and *lub*, it follows that

$$\tau_F^{i+1}(z) = lub(\delta_F^{i+1}, Y(\tau_F^i(z))) \sqsubseteq lub(\delta_F^{i+1}, Y(\sigma^i)) \sqsubseteq \sigma^{i+1}$$

and the induction step goes through and the lemma follows.  $\square$

Another way of stating this lemma is that every trajectory formula  $F$  is simple with defining trajectory  $\tau_F(\perp)$ .

The above lemmas give a simple method for computing the defining trajectory and the defining sequence for a trajectory formula. Unfortunately, there is a practical difficulty, since both the defining trajectory and the defining sequence are theoretically infinite sequences. The following technical lemma will be useful later to show that only a finite prefix of the defining trajectories and sequences are needed.

**Lemma 5** *Let  $F$  be a trajectory formula and let  $\delta_F = \delta_F^0\delta_F^1\dots$  be the defining sequence for formula  $F$ . Then  $\delta_F^i = \perp$  for  $i \geq d(F)$ .*

**Proof:** We prove the claim by induction on the formula structure. For the basis, if  $F = p$ , for some simple predicate  $p$  with defining value  $\bar{p}$ , then  $\delta_F = \bar{p} \perp \perp \dots$ . Since,  $d(p) = 1$ , it follows directly that  $\delta_F^i = \perp$  for  $i \geq d(F)$  and the basis holds.

Assume inductively that  $\delta_{F_1}^i = \perp$  for  $i \geq d(F_1)$  and that  $\delta_{F_2}^i = \perp$  for  $i \geq d(F_2)$  for some trajectory formulas  $F_1$  and  $F_2$ . If  $F = F_1 \wedge F_2$  then  $d(F) = \max(d(F_1), d(F_2))$ . Consider any  $i \geq d(F)$ . Since  $d(F) \geq d(F_1)$  and  $d(F) \geq d(F_2)$  it follows from the induction hypothesis that  $\delta_{F_1}^i = \perp$  and that  $\delta_{F_2}^i = \perp$ . Furthermore, since  $\delta_F = lub(\delta_{F_1}, \delta_{F_2})$  we can conclude that  $\delta_F^i = \perp$ .

If  $F = e \rightarrow F_1$  then there are two cases to consider. If  $e = 0$  then  $\delta_F = \perp \perp \dots$  and the claim follows trivially. On the other hand, if  $e = 1$  then  $\delta_F = \delta_{F_1}$ . By the induction hypothesis,  $\delta_{F_1}^i = \perp$  for every  $i \geq d(F_1)$ . Since,  $d(F) = d(F_1)$ , we can conclude that  $\delta_F^i = \perp$  for every  $i \geq d(F)$ .

Finally, if  $F = \mathbf{N}F_1$  then  $\delta_F = \perp \delta_{F_1}$ . By the induction hypothesis,  $\delta_{F_1}^i = \perp$  for every  $i \geq d(F_1)$ . Consequently,  $\delta_F^i = \perp$  for every  $i \geq d(F_1) + 1$ . However,  $d(F) = 1 + d(F_1)$  and thus  $\delta_F^i = \perp$  for every

$i \geq d(F)$ .

□

From this result we immediately get the following corollary.

**Corollary 1** *Assume  $A$  and  $C$  are two trajectory formulas. Let  $\tau_A = \tau_A^0 \tau_A^1 \dots$  be the defining trajectory for formula  $A$  and let  $\delta_C = \delta_C^0 \delta_C^1 \dots$  be the defining sequence for formula  $C$ . Then*

$$\delta_C \sqsubseteq \tau_A \quad \text{iff} \quad \delta_C^i \sqsubseteq \tau_A^i \text{ for } 0 \leq i < d(C)$$

## 6 Verification Methodology

Our specification language describes a property of the system  $\mathcal{M}$  as a “trajectory assertion”. Again, we have chosen a quite limited language in order to gain efficiency. We have three types of constructs: simple assertions, sequences, and iterations. Simple assertions are of the form “if the system ever goes through a sequence of states satisfying trajectory formula  $A$ , then the sequence of states better also satisfy the trajectory formula  $C$ ”. Sequences of assertions allow representing system behaviors that shift from one “mode” to another. For example, it is convenient to use in describing the desired behavior during each clock cycle for a microprocessor during the execution of a multi-cycle instruction. Finally, a simple assertion can also be iterated an arbitrary number of times. This construct is primarily useful for, automatically, establishing and proving invariants of the system. For example, a typical use of the iteration construct is when specifying the possibility of an arbitrary number of wait-states in a microprocessor. More specifically, we may want to verify that the processor works correctly no matter how many wait-states the external memory interface imposes. This could be accomplished by describing the constraints on the inputs during “wait cycles” and iterate this simple assertion an arbitrary number of times.

More formally, a *trajectory assertion* is defined recursively as:

1. **Simple assertions:**  $[A \Rightarrow C]$ , where  $A$  and  $C$  are trajectory formulas and  $d(A) = d(C)$ .

2. **Sequences:**  $[A \Rightarrow C]; G_1$ , where  $A$  and  $C$  are trajectory formulas,  $d(A) = d(C)$ , and  $G_1$  is a trajectory assertion.

3. **Iterations:**  $[A \Rightarrow C]^*; G_1$ , where  $A$  and  $C$  are trajectory formulas,  $d(A) = d(C)$ , and  $G_1$  is a trajectory assertion.

A trajectory assertion that does not contain any iteration, is said to be *iteration-free*.

The definition of a trajectory assertion is somewhat restrictive. For example, it does not allow a trajectory assertion to end with an iteration. The reason for this restriction is to simplify the definition of the truth semantics of trajectory assertions. In practice, it turns out not to be a serious restriction since one can always append  $[true \Rightarrow true]$  to an assertion that otherwise would end with an iteration.

To illustrate trajectory assertions, consider first our inverter circuit of Fig. 2. The following two assertions can constitute our specification of a unit-delay inverter:

$$[\text{in is } 0 \wedge \mathbf{N}true \Rightarrow \mathbf{N}out \text{ is } 1]$$

and

$$[\text{in is } 1 \wedge \mathbf{N}true \Rightarrow \mathbf{N}out \text{ is } 0].$$

Note that the  $\mathbf{N}true$  parts in the antecedents are simply there in order to make the depth of the antecedent equal the depth of the consequent. In a practical system, these “filler” functions

would be added automatically by the verification system and thus would not have to be expressed explicitly. However, in order to simplify the presentation of the general theory we have opted to require the depth of the antecedent to be equal to the depth of the consequent.

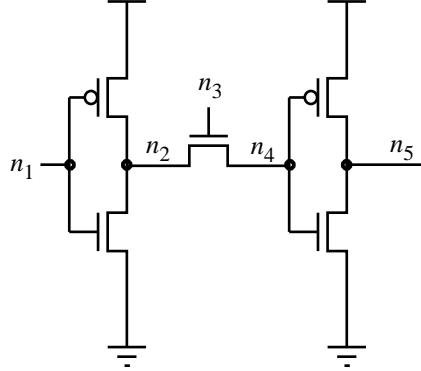

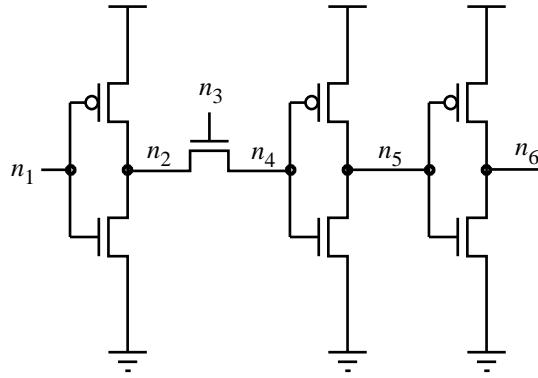

Figure 5: Switch-level latch.

Our next example shows the use of the sequence construct. Consider the switch-level circuit shown in Fig. 5. Intuitively,  $n_1$  is the input to a latch,  $n_3$  is the clock signal,  $n_4$  is the electrical node that stores the state when the clock is low, and  $n_5$  is the output of the output buffer. If the state of the circuit currently is  $t \in \mathcal{T}^5$ , a typical switch-level analysis of the circuit would derive the excitation functions:

$$y_1(t) = X \quad y_2(t) = \overline{t_1} \quad y_3(t) = X \quad y_4(t) = \overline{t_1}t_4 + t_3\overline{t_1} + \overline{t_3}t_4 \quad y_5(t) = \overline{t_4}$$

where all operators are assumed to be ternary. That is, nodes  $n_1$  and  $n_3$ , being input nodes, have excitation  $X$ . Nodes  $n_2$  and  $n_5$  are the outputs of simple inverters. Depending on the control signal on  $n_3$ , node  $n_4$  will either retain its stored charge ( $t_3 = 0$ ), or get the value from the first inverter ( $t_3 = 1$ ). If  $t_3 = X$ , node  $n_4$  will have a binary excitation only if the inverter output matches the value already on the node, and value  $X$  otherwise. Such excitation functions can be derived automatically from the transistor representation of the circuit by symbolic circuit analysis [8].

Since the latch is a sequential circuit and the clock signal changes the behavior quite drastically, it is natural to specify the desired behavior as a sequence of sub-behaviors—one for each clock phase. For example, the following assertion expresses the desired behavior of the circuit when each clock phase has a duration of two time units:

$$G_1 = \left[ ((n_1 \text{ is } 1) \wedge (n_3 \text{ is } 1))^{[2]} \Rightarrow \text{true}^{[2]} \right] ; \left[ (n_3 \text{ is } 0)^{[2]} \Rightarrow (n_5 \text{ is } 1)^{[2]} \right].$$

Recall that  $F^{[2]} = F \wedge \mathbf{N}F$  for an instantaneous trajectory formula  $F$ .

The above assertion only verifies the circuit behavior for one particular clock timing. In general, the desired behavior of a latch can be expressed informally as: “given that the clock cycle is longer than some minimum time, the circuit can load an input when the clock is high and retain it when the clock goes low”. The iteration construct can be used to formulate such a specification, yielding the assertion:

$$G_2 = \left[ ((n_1 \text{ is } 1) \wedge (n_3 \text{ is } 1))^{[2]} \Rightarrow \text{true}^{[2]} \right] ; \left[ (n_1 \text{ is } 1) \wedge (n_3 \text{ is } 1) \Rightarrow \text{true} \right]^* ; \\ \left[ (n_3 \text{ is } 0) \Rightarrow (n_5 \text{ is } 1) \right]^* ; \left[ \text{true} \Rightarrow \text{true} \right].$$

Intuitively, we are here stating that if the clock is high and the input is 1 for at least two time units and then the clock goes low, the output will remain 1. Note that any circuit passing  $G_2$  will pass  $G_1$ , but the opposite does not necessarily hold.

The example above illustrates our motivation for introducing the iteration construct. It allows the verification of systems that are characterized by periods of activity interspersed by periods in which the circuit is waiting for some external event before continuing. With a single trajectory evaluation we can verify correct circuit behavior for all possible durations of these idle periods. In the above example, the external events correspond to transitions of the clock, with the circuit remaining in a stable state until the clock changes. The antecedent of the iteration construct is an instantaneous formula specifying inputs that will be held fixed for the remainder of the clock phase, while the consequent specifies state values that should remain stable as long as the clock and inputs are held fixed. In other cases the iteration construct includes temporal operators indicating some periodic behavior of the system, such as the cycling of clocks while a processor is in a wait state. Note that this construct should not be confused with the operators of temporal logic denoting “eventual” behavior, such as the **F** or **U** operators of CTL [16]. We require the consequent of the iteration construct to hold for any number of repetitions (including 0) as long as the antecedent is satisfied.

Before we define the truth semantics of a trajectory assertion we need to introduce a function that removes some of the first elements in a sequence. Let the *suffix* of a sequence  $\sigma$  be defined recursively as follows:

$$\text{suffix}(n, \sigma^0 \tilde{\sigma}) = \begin{cases} \sigma^0 \tilde{\sigma} & \text{if } n = 0 \\ \text{suffix}(n - 1, \tilde{\sigma}) & \text{otherwise.} \end{cases}$$

Intuitively, the suffix function applied to some sequence removes the first  $n$  elements in the sequence.

The truth semantics of a trajectory assertion is defined relative to a model structure and a set of trajectories in this model structure. In particular, given a model structure  $\mathcal{M}$  and a set  $L$  of trajectories, the truth of a trajectory assertion  $G$ , written  $L \models_{\mathcal{M}} G$ , is defined recursively as follows:

1.  $L \models_{\mathcal{M}} [A \Rightarrow C]$  holds iff  $\sigma \models_{\mathcal{M}} A$  implies  $\sigma \models_{\mathcal{M}} C$  for all  $\sigma \in L$ .

2.  $L \models_{\mathcal{M}} [A \Rightarrow C]; G_1$  holds iff  $L \models_{\mathcal{M}} [A \Rightarrow C]$  and  $\tilde{L} \models_{\mathcal{M}} G_1$ , where

$$\tilde{L} = \{\tilde{\sigma} \mid \tilde{\sigma} = \text{suffix}(d(A), \sigma), \sigma \in L \text{ and } \sigma \models_{\mathcal{M}} A\}.$$

3.  $L \models_{\mathcal{M}} [A \Rightarrow C]^*; G_1$  holds iff  $L \models_{\mathcal{M}} G_1$  and  $\forall i \geq 1. L \models_{\mathcal{M}} [A^{[i]} \Rightarrow C^{[i]}]; G_1$ .

Since we often require a trajectory assertion to hold for all possible trajectories, we use the shorthand  $\models_{\mathcal{M}} G$  to denote  $L(\mathcal{M}) \models_{\mathcal{M}} G$ .

Returning to our examples of trajectory assertions above, we can easily see from Fig. 4 that

$$L(\mathcal{M}^C) \models_{\mathcal{M}} [\text{in is } 0 \wedge \text{Ntrue} \Rightarrow \text{Nout is } 1],$$

and that

$$L(\mathcal{M}^C) \models_{\mathcal{M}} [\text{in is } 1 \wedge \text{Ntrue} \Rightarrow \text{Nout is } 0].$$

What we will show in this section is how to determine the validity of a trajectory assertion without having to compute the complete state space as was done in Fig. 4.

The following, rather technical, lemma will be useful later.

**Lemma 6** *Given a model structure  $\mathcal{M}$ , an initial state  $z \in \mathcal{S}$ , and a trajectory formula  $F$  with defining trajectory  $\tau_F^0(z)\tau_F^1(z)\dots$ , let  $\tilde{L} = \{\tilde{\sigma} \mid \tilde{\sigma} = \text{suffix}(d(F), \sigma), \sigma \in L(\mathcal{M}, z) \text{ and } \sigma \models_{\mathcal{M}} F\}$ . Then  $\tilde{L} = L(\mathcal{M}, \tau_F^{d(F)}(z))$ .*

**Proof:** Assume first that  $\tilde{\sigma} \in \tilde{L}$ . This implies that there is a  $\sigma \in L(\mathcal{M}, z)$  such that  $\sigma \models_{\mathcal{M}} F$  and  $\tilde{\sigma} = \text{suffix}(d(F), \sigma)$ . Since  $\tilde{\sigma} = \text{suffix}(d(F), \sigma)$  and  $\sigma \in L(\mathcal{M}, z) \subseteq L(\mathcal{M})$  we can conclude from Proposition 1 that  $\tilde{\sigma} \in L(\mathcal{M})$ . Hence, in order to prove that  $\tilde{\sigma} \in L(\mathcal{M}, \tau_F^{d(F)}(z))$  it suffices to show that  $\tau_F^{d(F)}(z) \sqsubseteq \tilde{\sigma}^0$ . By Lemma 4 we know that  $\tau_F(z) \sqsubseteq \sigma$  iff  $\sigma \models_{\mathcal{M}} F$  for all  $\sigma \in L(\mathcal{M}, z)$ . In particular,  $\tau_F^{d(F)}(z) \sqsubseteq \sigma^{d(F)} = \tilde{\sigma}^0$  and the claim follows.

Conversely, assume  $\tilde{\sigma} \in L(\mathcal{M}, \tau_F^{d(F)}(z))$ . Define  $\sigma = \sigma^0\sigma^1\dots$  as follows:

$$\sigma^i = \begin{cases} \tau_F^i(z) & \text{if } i < d(F) \\ \tilde{\sigma}^{i-d(F)} & \text{otherwise} \end{cases}$$

Clearly  $\text{suffix}(d(F), \sigma) = \tilde{\sigma}$ . If we now can show that  $\sigma \in L(\mathcal{M}, z)$  and that  $\sigma \models_{\mathcal{M}} F$  it would follow that  $\tilde{\sigma} \in \tilde{L}$  and the claim of the lemma would be established.