# UNIT 8B Computer Organization: Levels of Abstraction

### **Announcements**

- Midsemester grades will be assigned this weekend

- Ps7 is due Friday March 22 in class

- Pa7 will be assigned shortly (due after break)

Pab - due tomorrow

### **Abstraction**

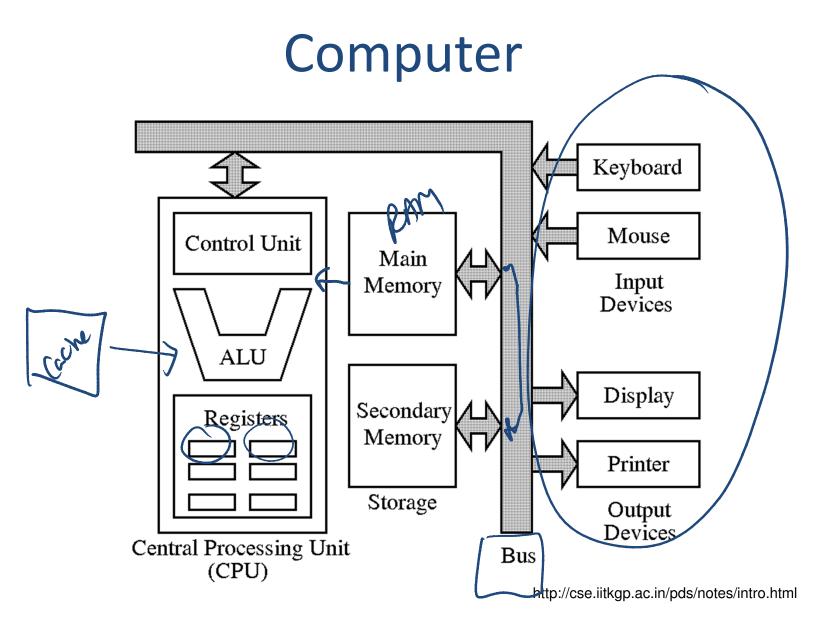

- We can use layers of abstraction to hide details of the computer design.

- We can work in any layer, not needing to know how the lower layers work or how the current layer fits into the larger system.

- -> transistors

- -> gates

- -x circuits (adders, multiplexors, flip-flops)

- -> central processing units((ALU), registers, control)

- -> computer

# Central Processing Unit (CPU)

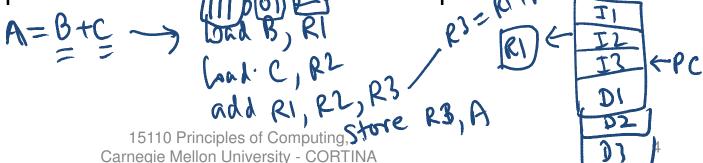

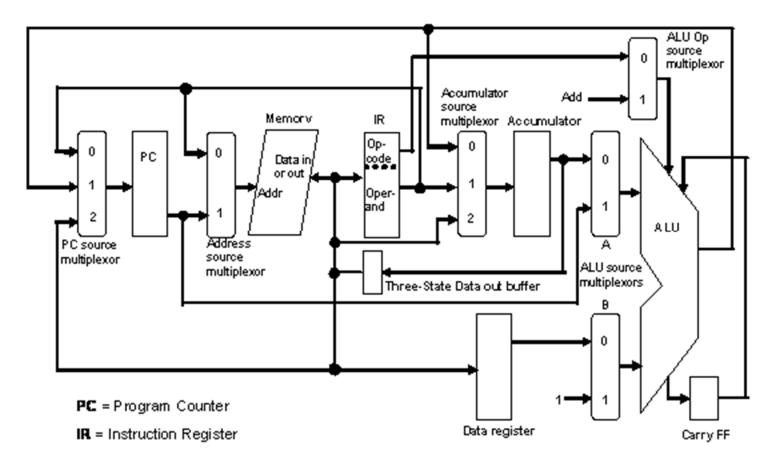

- A CPU contains:

- Arithmetic Logic Unit to perform computation

- Registers to hold information

- Instruction register (current instruction being executed)

- Program counter (to hold location of next instruction in memory)

- Accumulator (to hold computation result from ALU)

- Data register(s) (to hold other important data for future use)

- Control unit to regulate flow of information and operations that are performed at each instruction step

C Ph

RAM

HD

# A sample CPU

http://cpuville.com/main.htm

### To Gates

### Properties (Similar to × and +)

- Commutative:  $a \wedge b = b \wedge a$   $a \vee b = b \vee a$

- Associative:  $a \wedge b \wedge c = (a \wedge b) \wedge c = a \wedge (b \wedge c)$

- $a \lor b \lor c = (a \lor b) \lor c = a \lor (b \lor c)$

- Distributive:  $a \wedge (b \vee c) = (a \wedge b) \vee (a \wedge c)$

$$a \lor (b \land c) = (a \lor b) \land (a \lor c) \longleftrightarrow_{\substack{\text{Not true for } \\ + \text{and } \times}}$$

$a \lor 0 = a$

$a \vee 1 = 1$

- Identity: a ∧ 1 = a

- Dominance:  $a \wedge 0 = 0$

- Idempotence:  $a \wedge a = a$   $a \vee a = a$

- Complementation:  $a \land \neg a = 0$   $a \lor \neg a = 1$

- Double Negation:  $\neg \neg a = a$

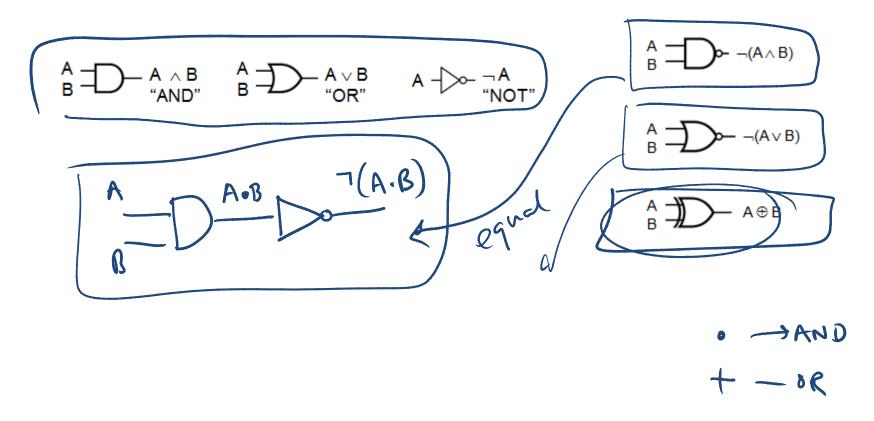

### equivalence

More gates

|   |   |             |         |         | 0       |

|---|---|-------------|---------|---------|---------|

| A | В | A nand<br>B | A nor B | A xor B | 4 arrs  |

| 0 | 0 | 1           | 1       | 0       | 0       |

| 0 | 1 | 1           | 0       | 1       |         |

| 1 | 0 | 1           | 0       | 1       |         |

| 1 | 1 | 0           | 0       | 0       | M       |

|   |   |             |         |         | 1 ' 1 ' |

MAND

C= 1

• nand ("not and"): A nand B = not (A and B)

- nor ("not or"): A nor B = not (A or B)

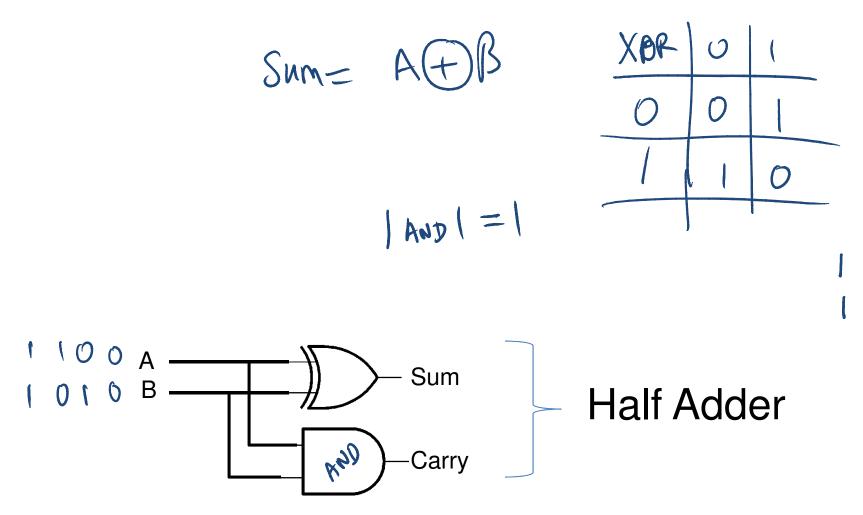

- xor ("exclusive or"):

A xor B =  $(A \text{ and not B}) \circ r (B \text{ and not A})$

$\begin{array}{c}

A \\

B

\end{array}$   $\begin{array}{c}

A \\

B

\end{array}$   $A \oplus B$

Carnegie Mellon University - CORTINA

## **All Gates**

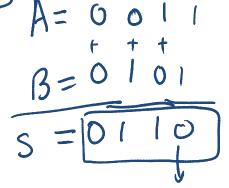

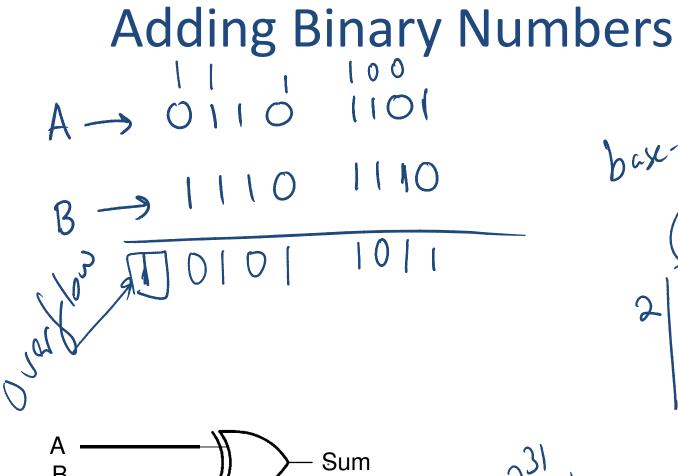

# **Adding Binary Numbers**

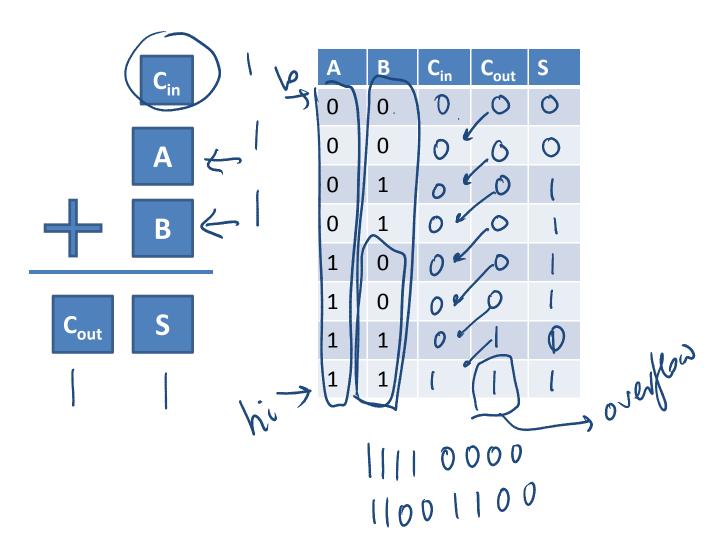

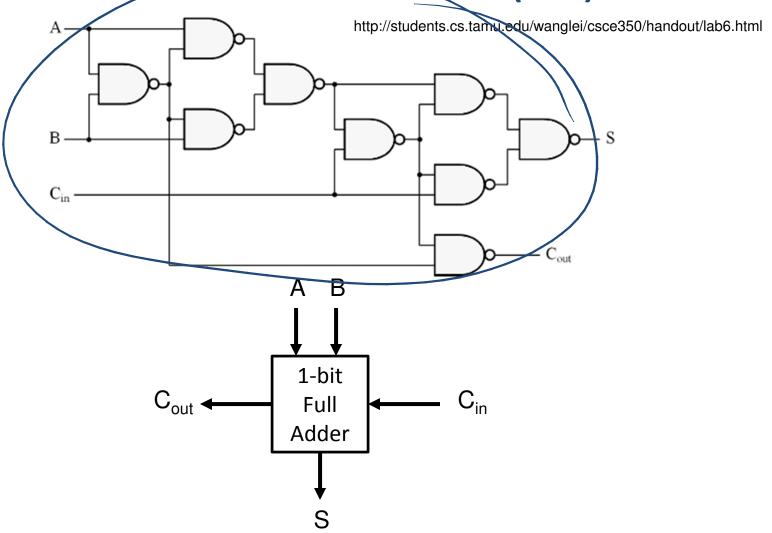

# A Full Adder

### A Full Adder

| Α | В | C <sub>in</sub> | C <sub>out</sub> | S |

|---|---|-----------------|------------------|---|

| 0 | 0 | 0               | 0                | 0 |

| 0 | 0 | 1               | 0                | 1 |

| 0 | 1 | 0               | 0                | 1 |

| 0 | 1 | 1               | 1                | 0 |

| 1 | 0 | 0               | 0                | 1 |

| 1 | 0 | 1               | 1                | 0 |

| 1 | 1 | 0               | 1                | 0 |

| 1 | 1 | 1               | 1                | 1 |

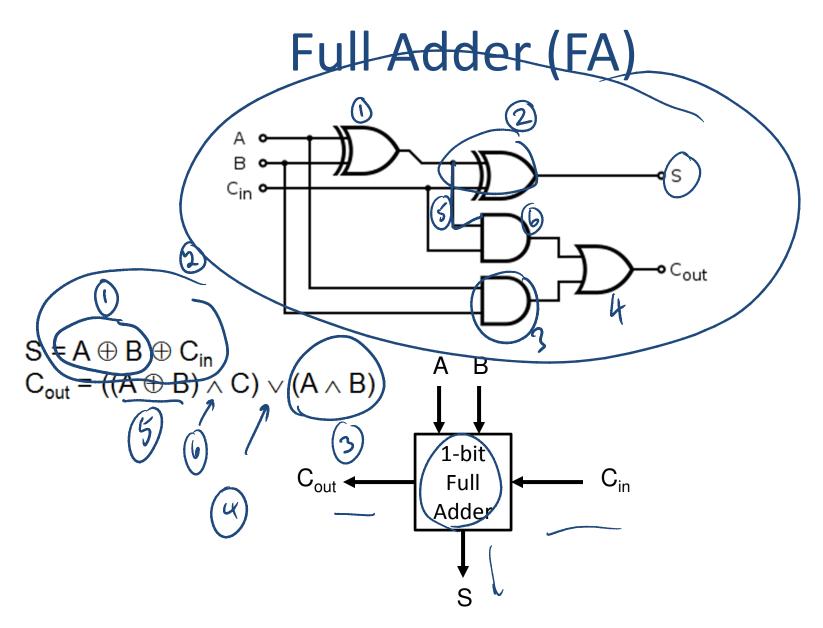

$$S = A \oplus B \oplus C_{in}$$

$C_{out} = ((A \oplus B) \land C) \lor (A \land B)$

15110 Principles of Computing, Carnegie Mellon University - CORTINA

# Another Full Adder (FA)

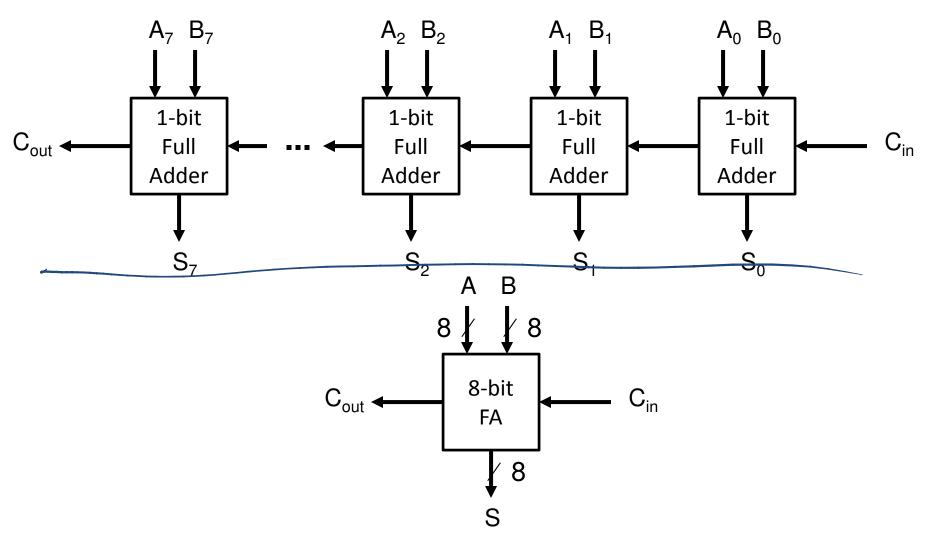

# 8-bit Full Adder

### Exercise

$$A \longrightarrow \neg(A \land B)$$

$$A \longrightarrow \neg (A \lor B)$$

### Exercise

$$^{A}_{B}$$

$\longrightarrow$   $^{A}_{AND}$

$$\begin{array}{c}

A \\

B

\end{array} \longrightarrow \neg (A \lor B)$$

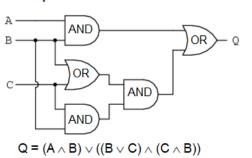

Convert circuit to expressions

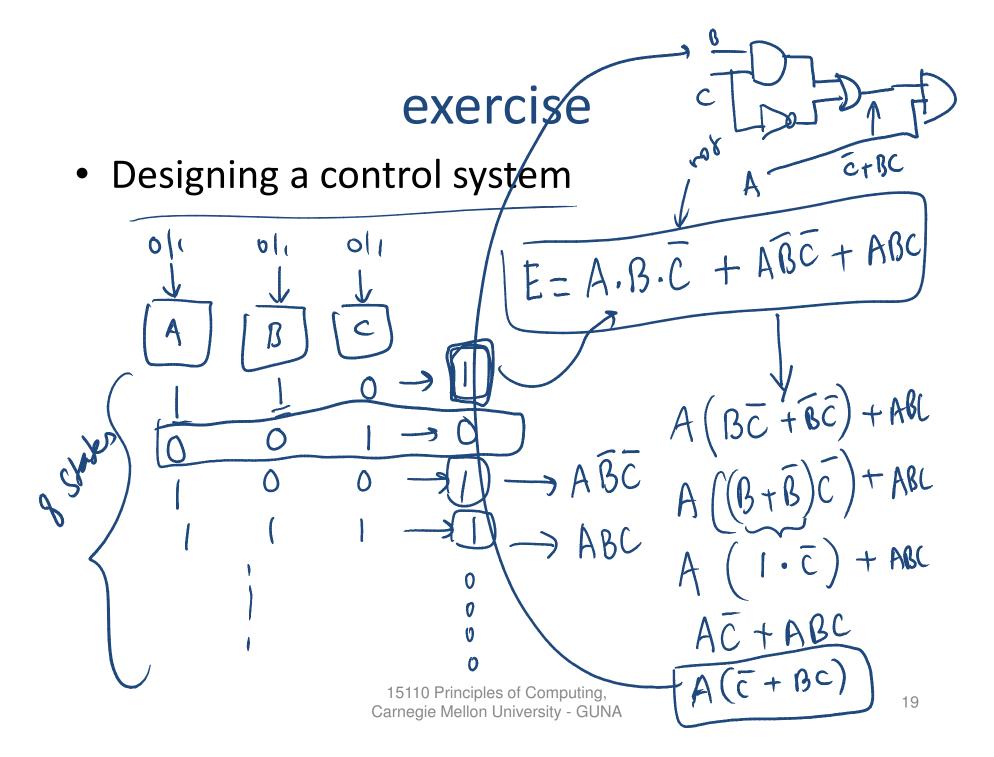

# From Design to circuits

| Α | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1      |