Carnegie Melle

## **Thread-Level Parallelism**

15-213 / 18-213: Introduction to Computer Systems  $26^{\rm th}$  Lecture, Apr. 26, 2012

#### Instructors:

Todd Mowry and Anthony Rowe

1

# Why Multi-Core?

- Traditionally, single core performance is improved by increasing the clock frequency...

- ...and making deeply pipelined circuits...

- Which leads to...

- Heat problems

- Speed of light problems

- Difficult design and verification

- Large design teams

- Big fans, heat sinks

- Expensive air-conditioning on server farms

- Increasing clock frequency no longer the way to go forward

**Today**

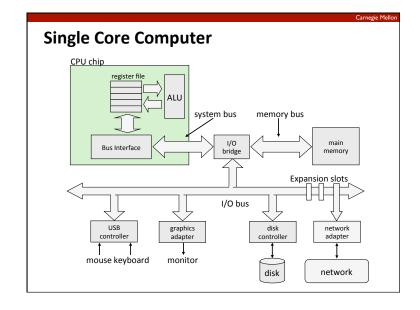

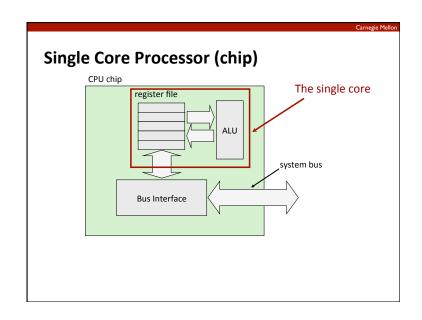

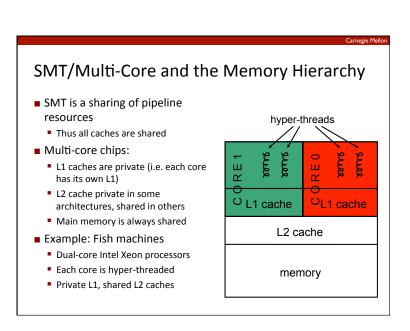

#### ■ Parallel Computing Hardware

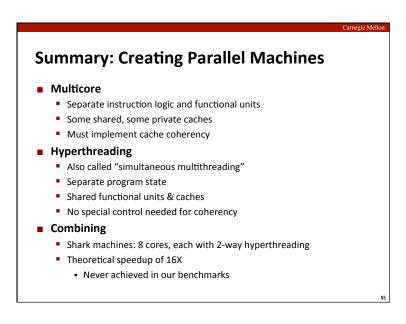

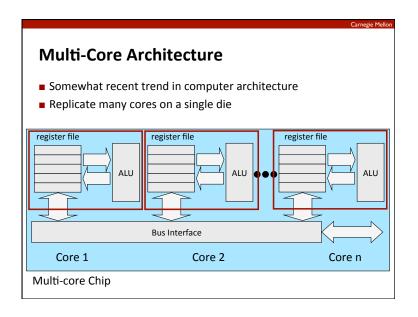

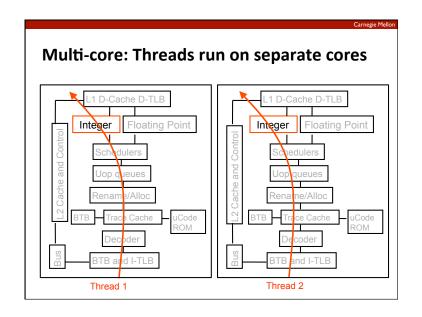

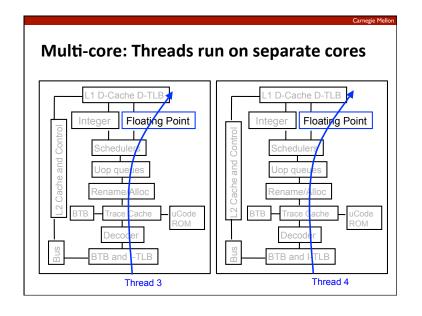

- Multicore

- Multiple separate processors on single chip

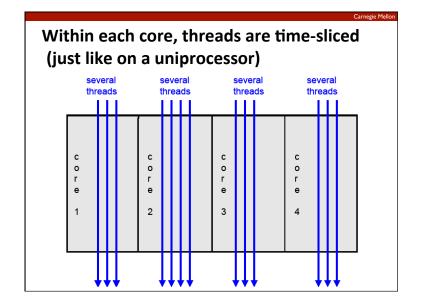

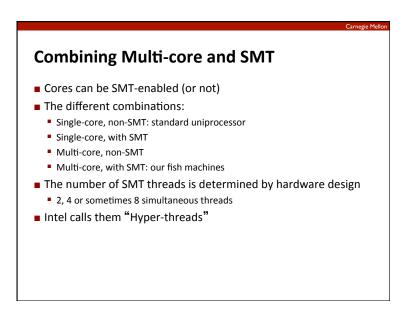

- Hyperthreading

- Multiple threads executed on a given processor at once

#### Thread-Level Parallelism

- Splitting program into independent tasks

- Example: Parallel summation

- Some performance artifacts

- Divide-and conquer parallelism

- Example: Parallel quicksort

2

Carnegie Melle

# **Interaction With the Operating System**

- OS perceives each core as a separate processor

- OS scheduler maps threads/processes to different cores

- Most major OS support multi-core today:

- Mac OS X, Linux, Windows, ...

# **Flavors of Parallelism**

- Instruction Level Parallelism (ILP)

- Thread Level Parallelism (TLP)

- Simultaneous Multi-Threading (SMT)

Carnegie Mellon

# **Instruction-Level Parallelism**

- Parallelism at the machine-instruction level

- Achieved in the processor with

- Pipeline

- Re-ordered instructions

- Split into micro-instructions

- Aggressive branch prediction

- Speculative execution

- ILP enabled rapid increases in processor performance

- Has since plateaued

Carnegie Melic

## Thread-level Parallelism

- Parallelism on a coarser scale

- Server can serve each client in a separate thread

- Web server, database server

- Computer game can do AI, graphics, physics, UI in four different threads

- Single-core superscalar processors cannot fully exploit TLP

- Thread instructions are interleaved on a coarse level with other threads

- Multi-core architectures are the next step in processor evolution: explicitly exploiting TLP

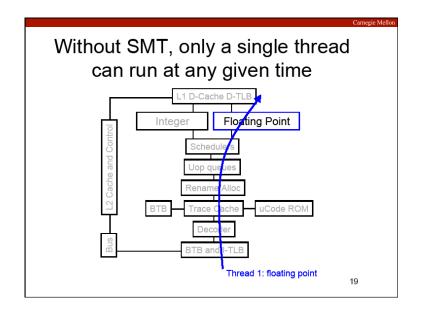

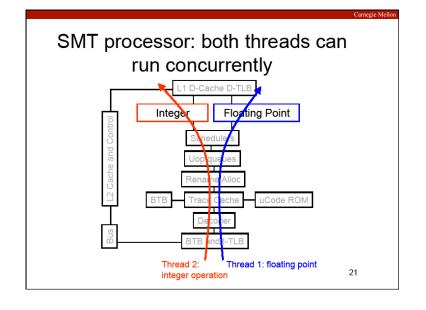

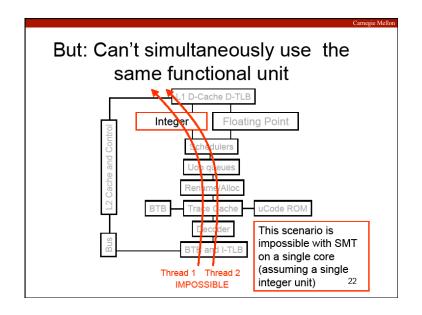

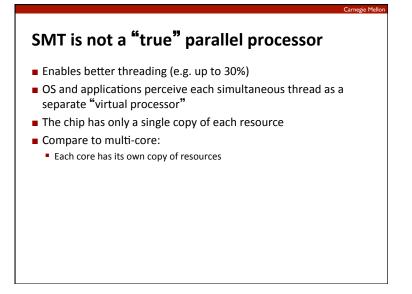

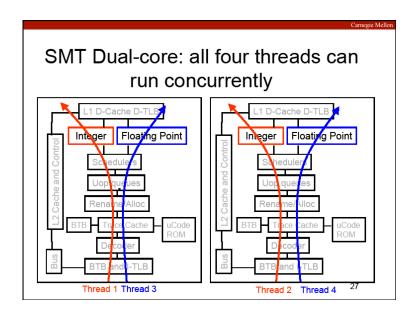

### **Simultaneous Multithreading (SMT)** ■ Complimentary technique to L1 D-Cache D-TLB multi-core Integer | Floating Point ■ Addresses the stalled pipeline L2 Cache and Control problem Schedulers Pipeline is stalled waiting for the Uop queues result of a long operation (float?) • ... or waiting for data to arrive from Rename/Alloc memory (long latency) BTB - Trace Cache uCode ■ Other execution units are idle Decoder BTB and I-TLB

Carnegie Mellon

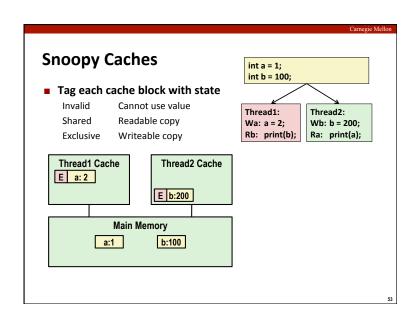

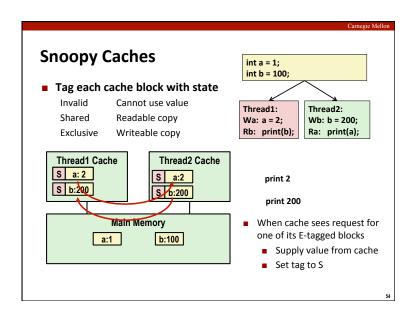

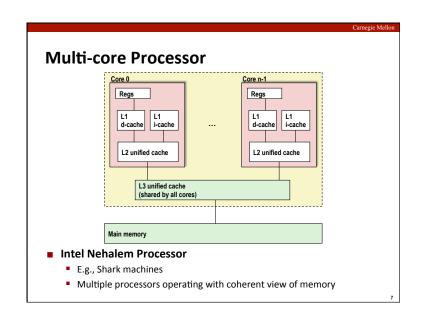

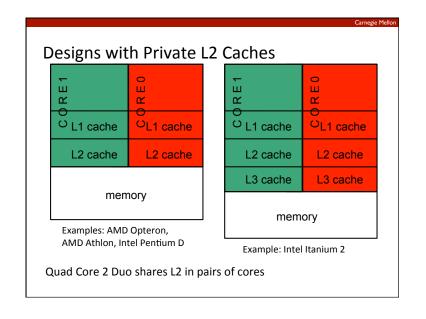

# **Private vs Shared Cache**

- Advantages of Private Cache

- Closer to the core, so faster access

- No contention for core access -- no waiting while another core accesses

- Advantages of Shared Cache

- Threads on different cores can share same cache data

- More cache space is available if a single (or a few) high-performance threads run

- Cache Coherence Problem

- The same memory value can be stored in multiple private caches

- Need to keep the data consistent across the caches

- Many solutions exist

- Invalidation protocol with bus snooping, ...

Carnegie Mellon

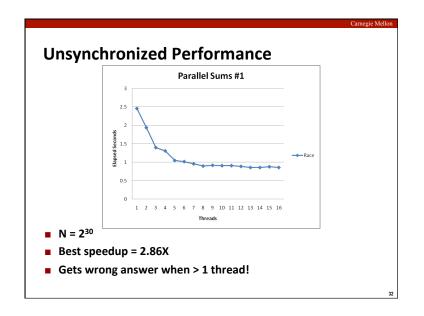

# **Summation Example**

- Sum numbers 0, ..., N-1

- Should add up to (N-1)\*N/2

- Partition into K ranges

- |N/K| values each

- Accumulate leftover values serially

- Method #1: All threads update single global variable

- 1A: No synchronization

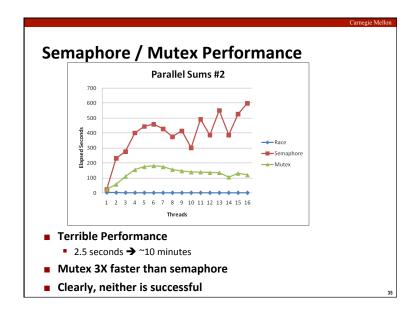

- 1B: Synchronize with pthread semaphore

- 1C: Synchronize with pthread mutex

- "Binary" semaphore. Only values 0 & 1

# **Exploiting parallel execution**

- So far, we've used threads to deal with I/O delays

- e.g., one thread per client to prevent one from delaying another

- Multi-core CPUs offer another opportunity

- Spread work over threads executing in parallel on N cores

- Happens automatically, if many independent tasks

- e.g., running many applications or serving many clients

- Can also write code to make one big task go faster

- by organizing it as multiple parallel sub-tasks

- Shark machines can execute 16 threads at once

- 8 cores, each with 2-way hyperthreading

- Theoretical speedup of 16X

- never achieved in our benchmarks

2

# Accumulating in Single Global Variable: Declarations

```

typedef unsigned long data_t;

/* Single accumulator */

volatile data_t global_sum;

/* Mutex & semaphore for global sum */

sem_t semaphore;

pthread_mutex_t mutex;

/* Number of elements summed by each thread */

size_t nelems_per_thread;

/* Keep track of thread IDs */

pthread_t tid[MAXTHREADS];

/* Identify each thread */

int myid[MAXTHREADS];

```

# Accumulating in Single Global Variable: Operation

```

nelems_per_thread = nelems / nthreads;

/* Set global value */

global_sum = 0;

/* Create threads and wait for them to finish */

for (i = 0; i < nthreads; i++) {

myid[i] = i;

Pthread_create(&tid[i], NULL, thread_fun, &myid[i]);

}

for (i = 0; i < nthreads; i++)

Pthread_join(tid[i], NULL);

result = global_sum;

/* Add leftover elements */

for (e = nthreads * nelems_per_thread; e < nelems; e++)

result += e;</pre>

```

```

Thread Function: No Synchronization

void *sum_race(void *vargp)

{

int myid = *((int *)vargp);

size_t start = myid * nelems_per_thread;

size_t end = start + nelems_per_thread;

size_t i;

for (i = start; i < end; i++) {

global_sum += i;

}

return NULL;

}</pre>

```

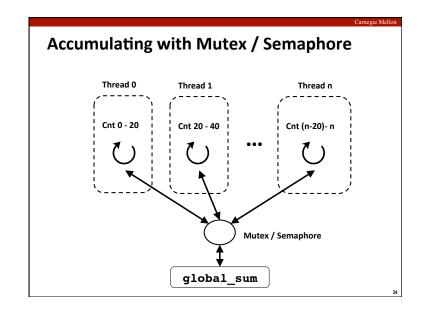

# Accumulating in Single Global Variable: Illustration Thread 0 Cnt 0-20 Cnt 20-40 Cnt (n-20)-n global\_sum

```

Thread Function: Semaphore / Mutex

Semaphore

void *sum_sem(void *vargp)

int myid = *((int *)vargp);

size_t start = myid * nelems_per_thread;

size_t end = start + nelems_per_thread;

size_t i;

for (i = start; i < end; i++) {</pre>

sem wait(&semaphore);

global sum += i;

sem_post(&semaphore);

return NULL;

Mutex

pthread mutex lock(&mutex);

global_sum += i;

pthread mutex unlock(&mutex);

```

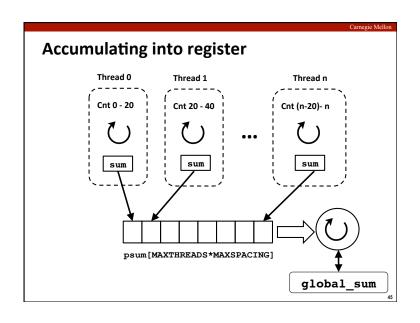

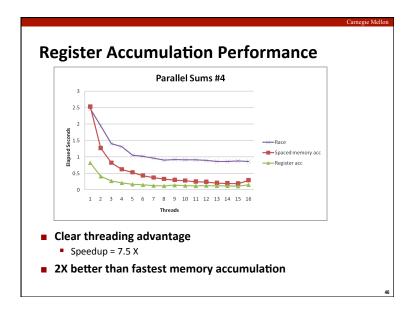

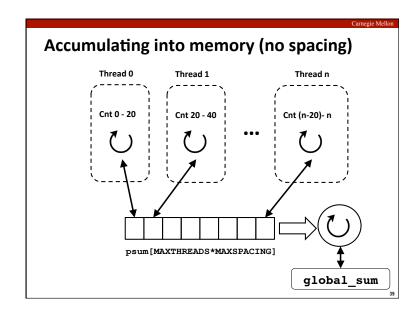

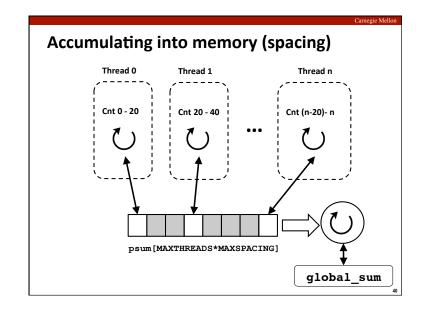

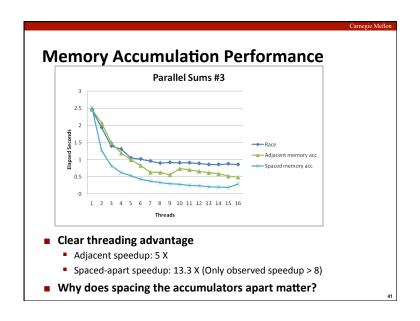

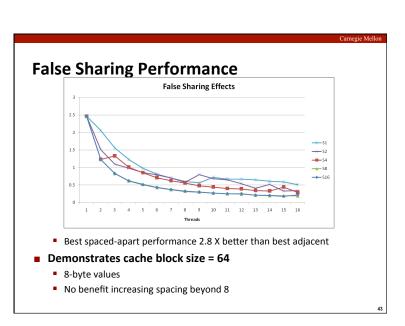

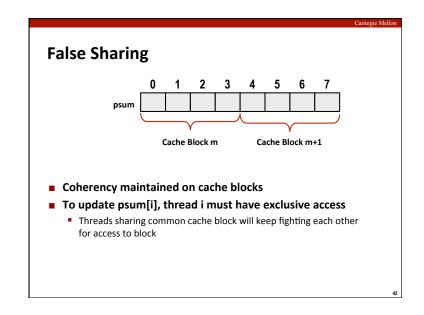

Separate Accumulation

• Method #2: Each thread accumulates into separate variable

• 2A: Accumulate in contiguous array elements

• 2B: Accumulate in spaced-apart array elements

• 2C: Accumulate in registers

/\* Partial sum computed by each thread \*/

data\_t psum[MAXTHREADS\*MAXSPACING];

/\* Spacing between accumulators \*/

size\_t spacing = 1;

# **Separate Accumulation: Operation** nelems\_per\_thread = nelems / nthreads; /\* Create threads and wait for them to finish \*/ for (i = 0; i < nthreads; i++) { myid[i] = i; psum[i\*spacing] = 0; Pthread\_create(&tid[i], NULL, thread\_fun, &myid[i]); for (i = 0; i < nthreads; i++)</pre> Pthread\_join(tid[i], NULL); result = 0; /\* Add up the partial sums computed by each thread \*/ for (i = 0; i < nthreads; i++)result += psum[i\*spacing]; /\* Add leftover elements \*/ for (e = nthreads \* nelems\_per\_thread; e < nelems; e++)</pre> result += e;

```

Thread Function: Memory Accumulation

void *sum_global(void *vargp)

{

int myid = *((int *)vargp);

size_t start = myid * nelems_per_thread;

size_t end = start + nelems_per_thread;

size_t i;

size_t index = myid*spacing;

psum[index] = 0;

for (i = start; i < end; i++) {

psum[index] += i;

}

return NULL;

}

```

```

Thread Function: Register Accumulation

void *sum_local(void *vargp)

{

int myid = *((int *)vargp);

size_t start = myid * nelems per_thread;

size_t end = start + nelems_per_thread;

size_t i;

size_t index = myid*spacing;

data_t sum = 0;

for (i = start; i < end; i++) {

sum += i;

}

psum[index] = sum;   return NULL;

}</pre>

```