# **Introduction to Computer Systems**

15-213/18-243, fall 2009 4<sup>th</sup> Lecture, Sep. 3<sup>rd</sup>

### Instructors:

Roger B. Dannenberg and Greg Ganger

**Last Time: Floating Point**

- Fractional binary numbers

- IEEE floating point standard: Definition

- Example and properties

- Rounding, addition, multiplication

- Floating point in C

- Summary

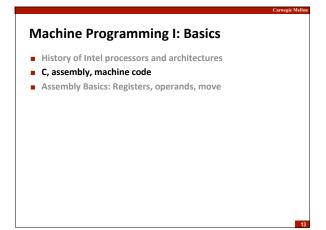

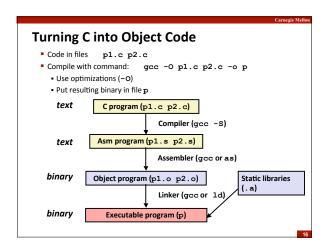

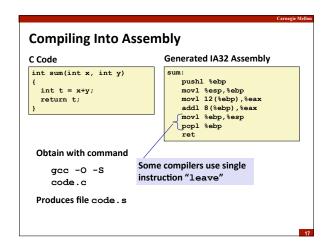

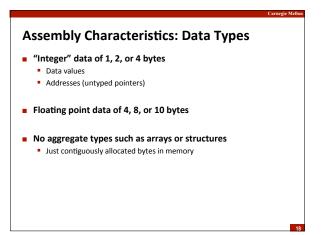

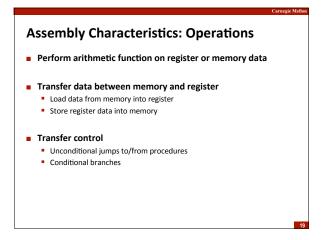

# **Machine Programming I: Basics**

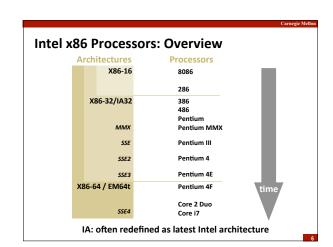

- History of Intel processors and architectures

- C, assembly, machine code

"Core" line

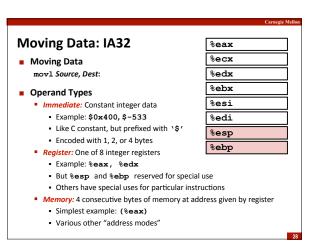

Assembly Basics: Registers, operands, move

# **Intel x86 Processors**

- Totally dominate computer market

- Evolutionary design

- Backwards compatible back to 8086, introduced in 1978

- Added more features as time goes on

- Complex instruction set computer (CISC)

- Many different instructions with many different formats

- But, only small subset encountered with Linux programs

- Hard to match performance of Reduced Instruction Set Computers

- But, Intel has done just that!

Intel x86 Evolution: Milestones Name Date **Transistors** MHz **8086** 1978 29K 5-10 First 16-bit processor. Basis for IBM PC & DOS ■ 1MB address space 1985 16-33 **386** 275K First 32 bit processor , referred to as IA32 Added "flat addressing" Capable of running Unix 32-bit Linux/gcc uses no instructions introduced in later models Pentium 4F 2005 2800-3800 First 64-bit processor Meanwhile, Pentium 4s (Netburst arch.) phased out in favor of

Intel x86 Processors, contd.

### ■ Machine Evolution

| <b>486</b>                     | 1989 | 1.9M |

|--------------------------------|------|------|

| <ul><li>Pentium</li></ul>      | 1993 | 3.1M |

| Pentium/MMX                    | 1997 | 4.5M |

| <ul><li>PentiumPro</li></ul>   | 1995 | 6.5M |

| <ul><li>Pentium III</li></ul>  | 1999 | 8.2M |

| Pentium 4                      | 2001 | 42M  |

| <ul> <li>Core 2 Duo</li> </ul> | 2006 | 291M |

#### Added Features

- Instructions to support multimedia operations

- Parallel operations on 1, 2, and 4-byte data, both integer & FP

- Instructions to enable more efficient conditional operations

- Linux/GCC Evolution

- Very limited

More Information

- Intel processors (Wikipedia)

- Intel microarchitectures

# New Species: ia64, then IPF, then Itanium,...

Name Date Transistors

■ Itanium 2001 10M ■ First shot at 64-bit architecture: first called IA64

- Radically new instruction set designed for high performance

- Can run existing IA32 programs

- On-board "x86 engine"

- Joint project with Hewlett-Packard

■ Itanium 2 2002 221M

Big performance boost

■ Itanium 2 Dual-Core 2006 1.7B

Itanium has not taken off in marketplace

Lack of backward compatibility, no good compiler support, Pentium 4 got too good •

# x86 Clones: Advanced Micro Devices (AMD)

#### Historically

- AMD has followed just behind Intel

- A little bit slower, a lot cheaper

#### ■ Then

- Recruited top circuit designers from Digital Equipment Corp. and other downward trending companies

- Built Opteron: tough competitor to Pentium 4

- Developed x86-64, their own extension to 64 bits

## ■ Recently

- Intel much quicker with dual core design

- Intel currently far ahead in performance

- em64t backwards compatible to x86-64

arnegie Mell

## Intel's 64-Bit

- Intel Attempted Radical Shift from IA32 to IA64

- Totally different architecture (Itanium)

- Executes IA32 code only as legacy

- Performance disappointing

- AMD Stepped in with Evolutionary Solution

- x86-64 (now called "AMD64")

- Intel Felt Obligated to Focus on IA64

- Hard to admit mistake or that AMD is better

- 2004: Intel Announces EM64T extension to IA32

- Extended Memory 64-bit Technology

- Almost identical to x86-64!

- Our Saltwater fish machines

- Meanwhile: EM64t well introduced, however, still often not used by OS, programs

**Our Coverage**

- IA32

- The traditional x86

- x86-64/EM64T

- The emerging standard

- Presentation

- Book has IA32

- Handout has x86-64

- Lecture will cover both

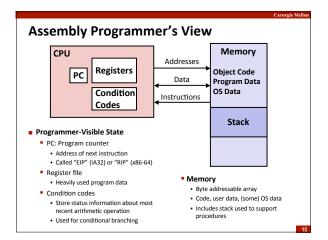

# Definitions Architecture: (also instruction set architecture: ISA) The parts of a processor design that one needs to understand to write assembly code. Microarchitecture: Implementation of the architecture. Architecture examples: instruction set specification, registers. Microarchitecture examples: cache sizes and core frequency. Example ISAs (Intel): x86, IA, IPF

```

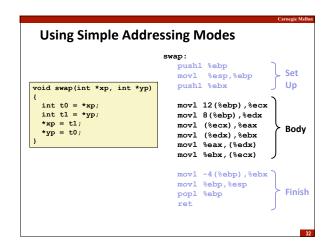

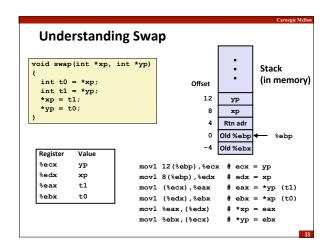

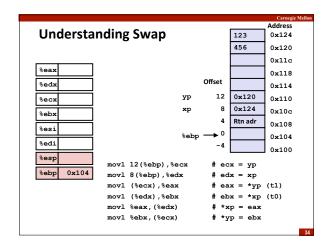

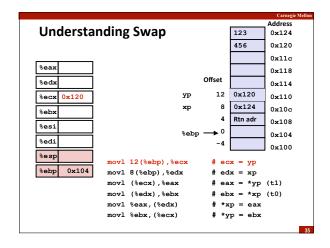

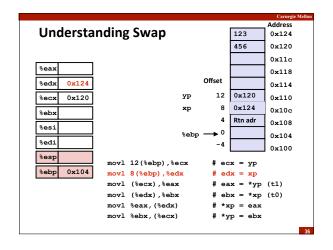

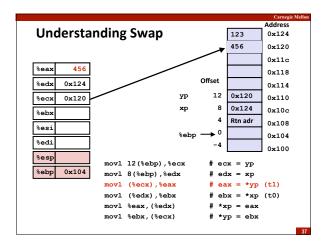

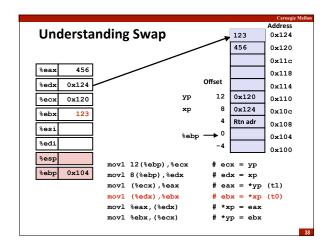

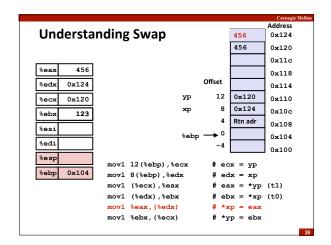

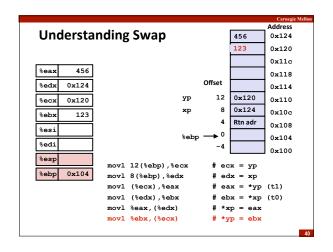

Using Simple Addressing Modes

swap:

pushl %ebp

Set

movl %esp,%ebp

Up

pushl %ebx

void swap(int *xp, int *yp)

int t0 = *xp;

movl 12(%ebp),%ecx

int t1 = *yp;

*xp = t1;

*yp = t0;

movl 8(%ebp),%edx

movl (%ecx),%eax

Body

movl (%edx),%ebx

movl %eax.(%edx)

movl %ebx, (%ecx)

movl -4(%ebp),%ebx

movl %ebp,%esp

Finish

popl %ebp

ret

```

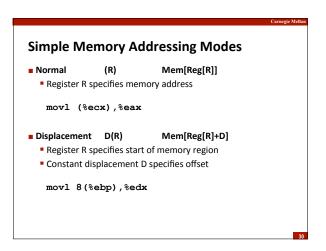

## **Complete Memory Addressing Modes** ■ Most General Form Mem[Reg[Rb]+S\*Reg[Ri]+D] D(Rb,Ri,S) ■ D· Constant "displacement" 1, 2, or 4 bytes Base register: Any of 8 integer registers Ri: Index register: Any, except for %esp • Unlikely you'd use %ebp, either Scale: 1, 2, 4, or 8 (why these numbers?) ■ Special Cases (Rb,Ri) Mem[Reg[Rb]+Reg[Ri]] D(Rb,Ri) Mem[Reg[Rb]+Reg[Ri]+D] (Rb,Ri,S) Mem[Reg[Rb]+S\*Reg[Ri]]