# Design of an efficient Software Environment for a RDMA Network Interface Controller

Diploma Thesis by Sven Stork

presented to

Computer Architecture Group

Department of Computer Engineering

University of Mannheim

11 January 2006

Referee : Prof. Dr.-Ing. Ulrich Brüning

Co - Referee : Prof. Dr. K.-H. Brenner Supervisor : Dipl.-Inf. Mondrian Nüssle

### **Abstract**

The goal of this thesis is to evaluate the requirements, the design and the implementation of an efficient software interface for the Extoll NIC. The resulting software is called Extoll Software Stack (ESS).

The design of the ESS should be efficient and exploit the maximum performance that will be offered by the Extoll NIC. The software interface should be clear and intuitive. An important point is the optimization of the software interface for an easy and efficient collaboration with already existing middle-wares, like MPI and DAPL.

The first part of the thesis gives an overview of the currently available communication interfaces. The next part evaluates the Extoll NIC hostport interface. Based on the determined hostport interface the ESS design will be presented. The last part of the thesis gives an overview of the current implementation and testing environment of the ESS.

## **Contents**

| Abstract                                 | III  |

|------------------------------------------|------|

| Contents                                 | V    |

| List of Figures                          | XI   |

| List of Tables                           | XIII |

| List of Listings.                        | XV   |

| Introduction                             | 1    |

|                                          |      |

| 1.1 Outline                              |      |

| 1.2.1 Definitions                        |      |

| 1.2.2 Decision Tree                      |      |

| 1.2.3 UML                                |      |

| 1.2.5 (1.11)                             |      |

| <b>Communication Interfaces</b>          |      |

| 2.1 BSD Socket API                       |      |

| 2.2 Atoll - PALMS.                       |      |

| 2.3 Myrinet - MX                         |      |

| 2.4 Quadrics - Elan Library              |      |

| 2.5 InfiniBand - Verbs                   |      |

| 2.6 DAPL                                 |      |

| 2.7 MPI                                  |      |

| 2.8 Conclusions                          | 17   |

| Extoll Hostport Interface                | 19   |

| 3.1 Atoll Basics                         |      |

| 3.1.1 Atoll Architecture.                |      |

| 3.1.2 Atoll Send                         |      |

| 3.1.3 Atoll Receive                      |      |

| 3.1.4 Summary                            |      |

| 3.2 Extoll Overview                      |      |

| 3.3 Global Information for VPs           | 25   |

| 3.3.1 Global Information for Event Queue | 26   |

| 3.4 Extoll Descriptors                   | 26   |

| 3.4.1 Virtual Port Descriptor            |      |

| 3.4.1.1 Virtual Port Status Word         | 29   |

| 3.4.1.2 Virtual Port Map                 |      |

| 3.4.2 Window Descriptor                  | 29   |

| 3.4.3 Notification Descriptor            |      |

| 3.4.4 Virtual Communication Instruction  |      |

| 3.4.5 Consistency                        |      |

| 3.5 Notification system                  |      |

| 3 5 1 Notification Error Codes           | 34   |

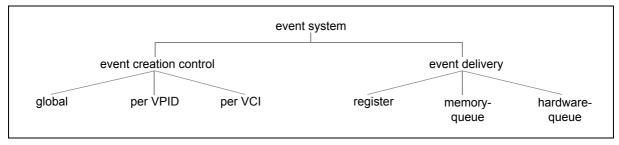

| 3.6 Event System                                                          | . 34              |

|---------------------------------------------------------------------------|-------------------|

| 3.6.1 Event creation control                                              |                   |

| 3.6.1.1 Global Event Creation Controlling                                 |                   |

| 3.6.1.2 Event Creation Control per Virtual Port                           |                   |

| 3.6.1.3 Event creation control per VCI                                    |                   |

| 3.6.1.4 Conclusion: Event creation control                                |                   |

| 3.6.2 Event delivery                                                      |                   |

| 3.6.2.1 Lazy Event Signalling                                             |                   |

| 3.6.2.2 Global Event Register                                             |                   |

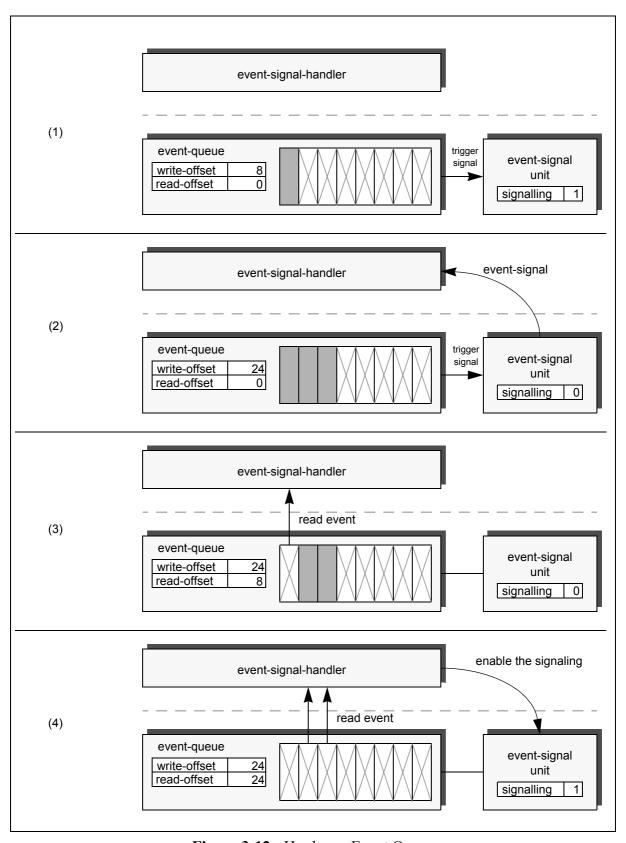

| 3.6.2.3 Hardware Event Queue                                              |                   |

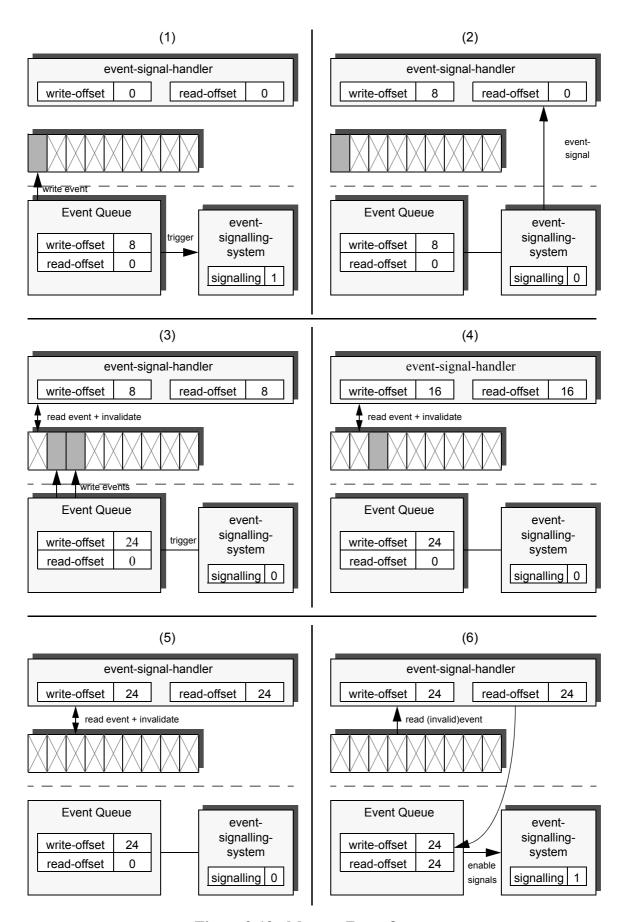

| 3.6.2.4 Memory Event Queue                                                |                   |

| 3.6.2.5 Conclusion: Event delivery                                        |                   |

| 3.6.3 Event Format.                                                       |                   |

| 3.7 Order of communication                                                |                   |

| 3.7.1 General observations                                                |                   |

| 3.7.2 Order of Communication in MPI                                       |                   |

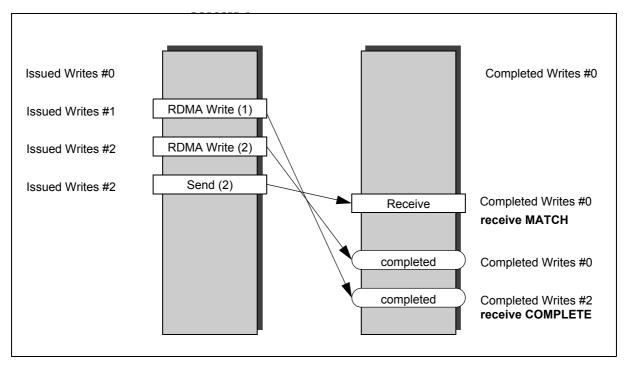

| 3.7.3 Order of Communication in DAPL                                      |                   |

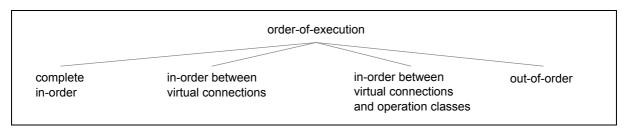

| 3.7.4 Order Classifications                                               |                   |

| 3.7.4.1 Complete in-order                                                 |                   |

| 3.7.4.2 Complete in-order on a Virtual Connection                         | -                 |

| 3.7.4.3 In-order on Virtual Connections and the same Communication Class. |                   |

| 3.7.4.4 Out-of-order                                                      |                   |

| 3.7.5 Conclusion: Order of Communication                                  |                   |

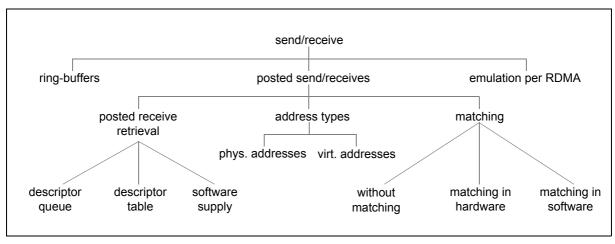

| 3.8 Send and Receive System                                               |                   |

| 3.8.1 Send/Receive with Ring Buffers                                      |                   |

| 3.8.2 Posted Send/Receive Operations                                      |                   |

| 3.8.2.1 Posted Receive Descriptors stored in Queue                        |                   |

| 3.8.2.2 Posted Receives Descriptors stored in a Table                     |                   |

| 3.8.2.3 Posted Receives provided by Software                              |                   |

| 3.8.2.4 Posted Send/Receive without Matching                              |                   |

| 3.8.2.5 Posted Send/Receive with Matching in Hardware                     |                   |

| 3.8.2.6 Posted Send/Receive with Matching in Software                     |                   |

| 3.8.2.7 Posted Send/Receive with Virtual Addresses                        |                   |

| 3.8.2.8 Posted Send/Receive with physical addresses                       |                   |

| 3.8.3 Send/Receive Emulation per RDMA.                                    |                   |

| 3.8.4 Conclusion: Send/Receive Systems.                                   |                   |

| 3.8.4.1 Posted Receive Descriptor Format                                  |                   |

| 3.9 Extoll Caches                                                         |                   |

| 3.9.1 Cache Management                                                    |                   |

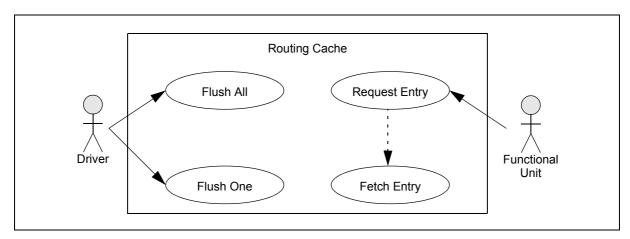

| 3.9.2 RC - Routing Cache                                                  |                   |

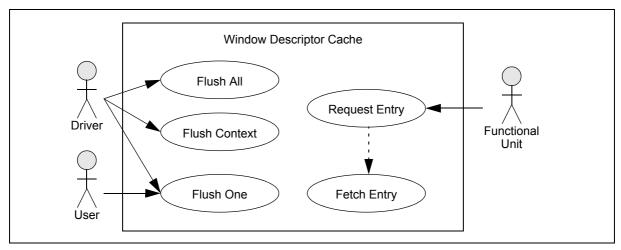

| 3.9.3 WDC - Window Descriptor Cache                                       | . <i>55</i><br>56 |

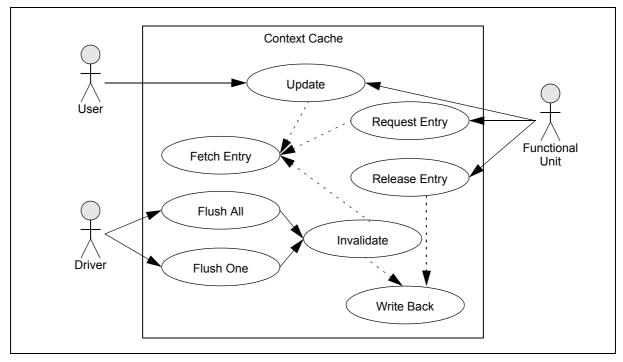

| 3.9.4 CC - Context Cache                                                  |                   |

| 3.9.5 TLB - Translation Lookaside Buffer                                  | . 50<br>. 57      |

| 3.10 The Barrier                                                          |                   |

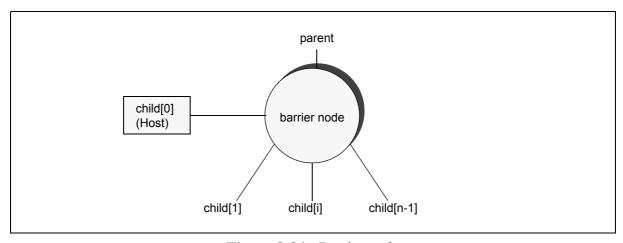

| 3.10.1 Design of the Barrier Software Interface                           |                   |

| 3.10.1 Design of the Barrier Software Interface                           |                   |

| 3.10.1.2 Collective Barrier Allocation                                    |                   |

| 3.10.1.3 Central Barrier Management                                       |                   |

|                                                                           |                   |

| 3.10.1.4 Distributed Barrier Management                                   |                   |

| 5.10.1.5 Duille Dille via Mellor / liadbea 1/O 1 aze                      | . ∪+              |

| 3.10.1.6 Barrier Enter via VCI               | 64 |

|----------------------------------------------|----|

| 3.10.1.7 Barrier Leave via I/O mapped Memory |    |

| 3.10.1.8 Barrier Leave via Notification      |    |

| 3.10.1.9 Conclusion : Extoll Barrier         |    |

| 3.10.2 Extoll Barrier Usage                  |    |

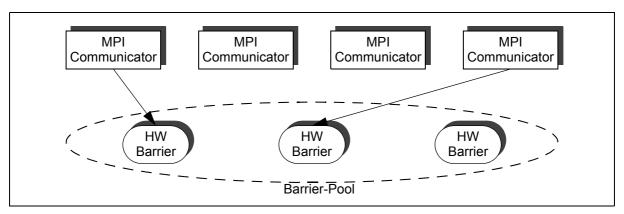

| 3.10.2.1 Barrier Mapping 1:1                 |    |

| 3.10.2.2 Barrier Mapping M:N                 |    |

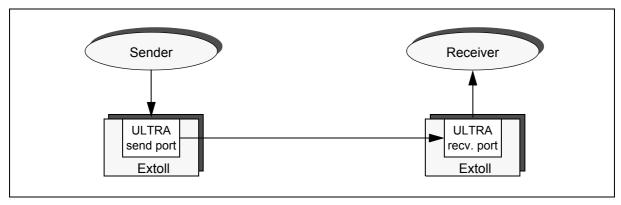

| 3.11 The ULTRA System.                       |    |

| 3.11.1 ULTRA Management                      |    |

| 3.11.2 ULTRA Send Port                       |    |

| 3.11.3 ULTRA Receive Port                    |    |

| 3.11.3.1 ULTRA Receive via PIO               |    |

| 3.11.3.2 ULTRA Receive via DMA Buffer        |    |

| 3.11.4 Conclusion: ULTRA Receive             |    |

| 3.12 Proposal for a new RDMA Operation       |    |

| 5.12 Hoposai for a flew KDWA Operation       | 09 |

| Design of the ESS                            | 71 |

|                                              |    |

| 4.1 Extoll Software Stack                    |    |

| 4.1.1 Requirements of the ESS.               | 71 |

| 4.1.2 Design of the ESS.                     |    |

| 4.1.2.1 Routing Management                   |    |

| 4.1.2.2 Memory Management                    |    |

| 4.1.2.3 Logging Support                      |    |

| 4.1.2.4 Application Programming Interface    |    |

| 4.1.2.5 Device Driver                        | 74 |

| 4.1.2.6 Conclusion: Design of the ESS        |    |

| 4.2 Extoll Logging System.                   |    |

| 4.2.1 Requirements                           |    |

| 4.2.2 Design                                 |    |

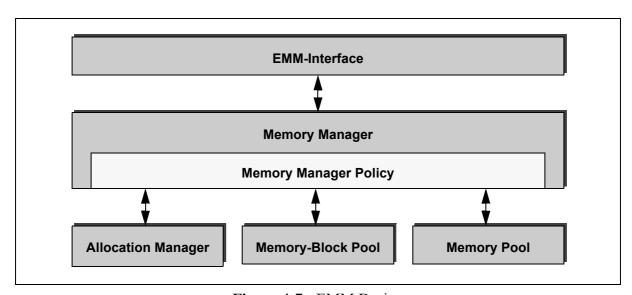

| 4.3 Extoll Memory Manager                    | 77 |

| 4.3.1 Requirements                           |    |

| 4.3.2 Design                                 | 78 |

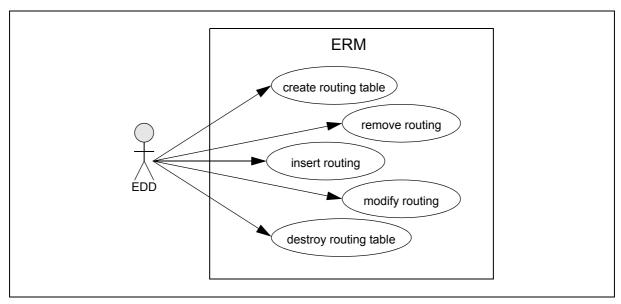

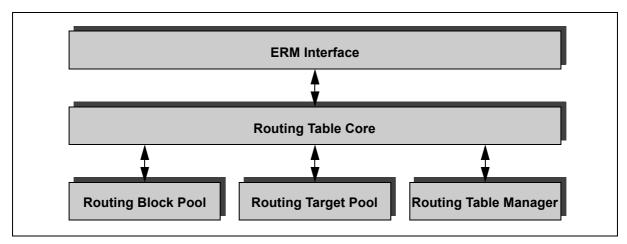

| 4.4 Extoll Routing Manager                   | 79 |

| 4.4.1 Requirements                           | 79 |

| 4.4.2 Design                                 | 80 |

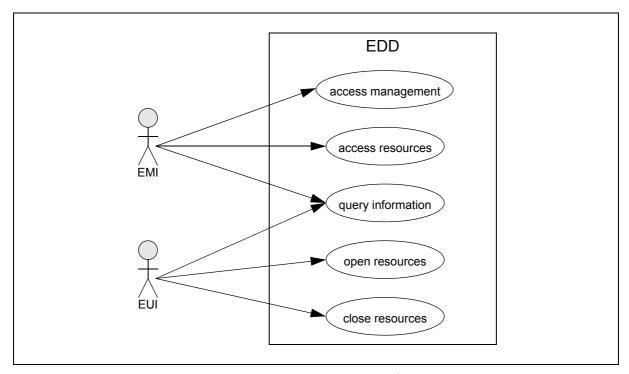

| 4.5 Extoll Device Driver                     | 80 |

| 4.5.1 Requirements                           | 80 |

| 4.5.2 Design                                 |    |

| 4.6 Extoll User Interface                    |    |

| 4.6.1 Requirements                           | 84 |

| 4.6.2 Design                                 |    |

| 4.7 Extoll Management Interface              |    |

| 4.7.1 Requirements                           |    |

| 4.7.2 Design                                 |    |

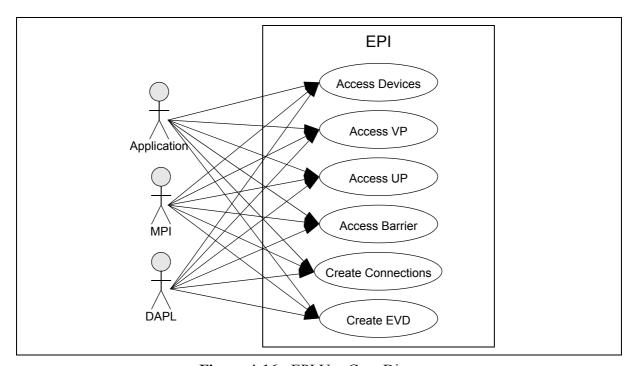

| 4.8 Extoll Programming Interface             |    |

| 4.8.1 Requirements                           |    |

| 4.8.2 Design                                 |    |

| 4 9 Extoll Daemon                            |    |

| Implementation of the ESS 91                    |

|-------------------------------------------------|

| 5.1 General 91                                  |

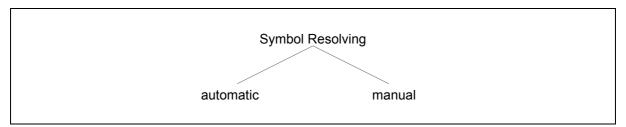

| 5.1.1 Symbol Resolving                          |

| 5.1.1.1 Automatic Symbol Resolving              |

| 5.1.1.2 Manual Symbol Resolving                 |

| 5.1.1.3 Conclusion: Symbol Resolving            |

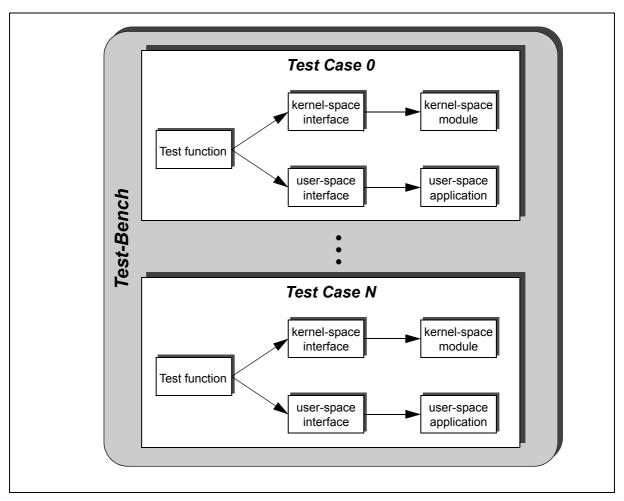

| 5.1.2 Extoll Testing Framework.                 |

| 5.1.2.1 Design Goals                            |

| 5.1.2.2 Structure                               |

| 5.1.3 Configuration                             |

| 5.1.3.1 Compiletime Configuration               |

| 5.1.3.2 Loadtime Configuration                  |

| 5.1.3.3 Runtime Configuration                   |

| 5.2 ELS                                         |

| 5.3 EMM                                         |

| 5.4 ERM                                         |

| 5.4.1 Routing Table Management                  |

| 5.4.2 Routing Failure                           |

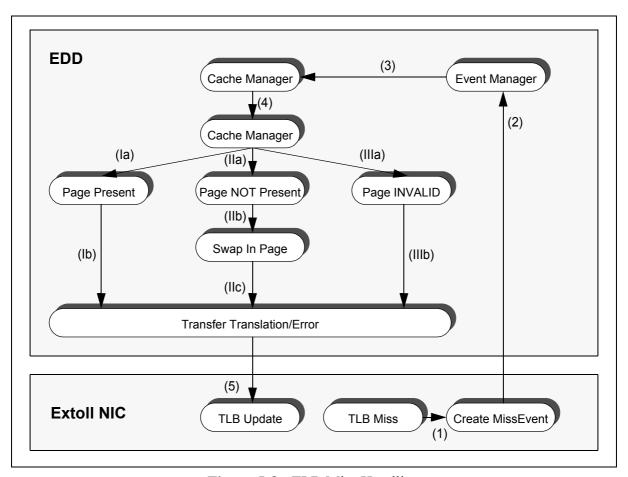

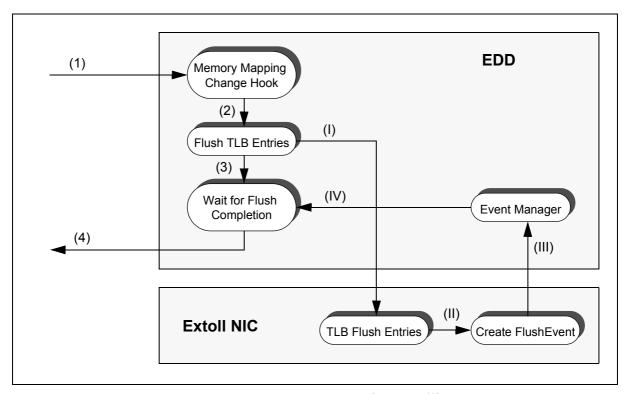

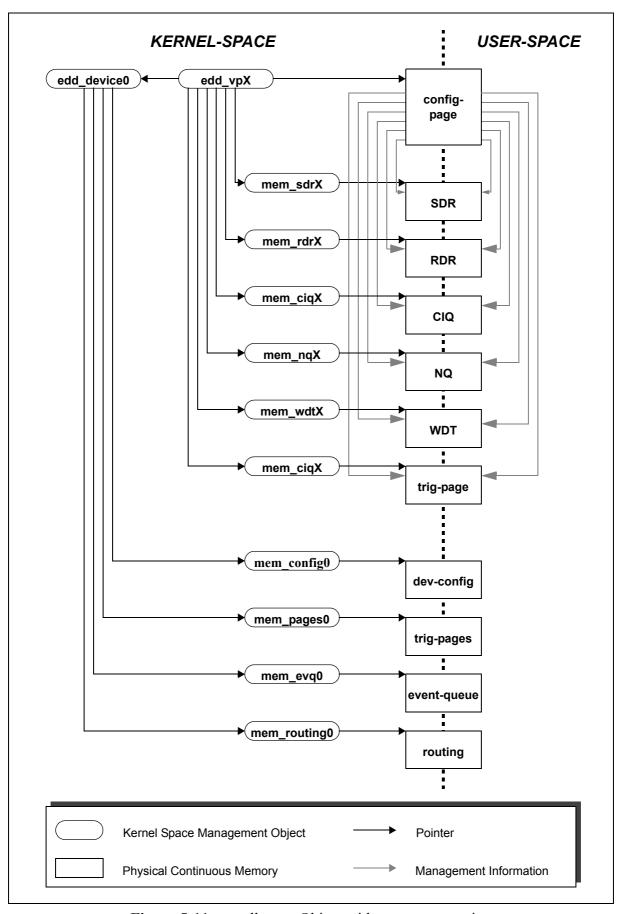

| 5.5 EDD                                         |

| 5.5.1 Process Management                        |

| 5.5.1.1 Threads                                 |

| 5.5.2 Device management.                        |

|                                                 |

| 5.5.3 VP Management975.5.4 Barrier Management99 |

| 5.5.5 UP Management 99                          |

| 5.5.6 Connections Management 99                 |

|                                                 |

| 5.5.7 VPG Management 99 5.5.8 FOPS-Mapper 99    |

| Tr ·                                            |

|                                                 |

| 5.5.10 Poll/ePoll Support                       |

| 5.6 EUI                                         |

| C., E., E.                                      |

| 5.8 EPI                                         |

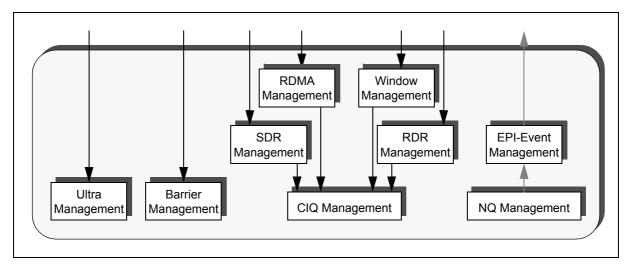

| 5.8.1 Structure                                 |

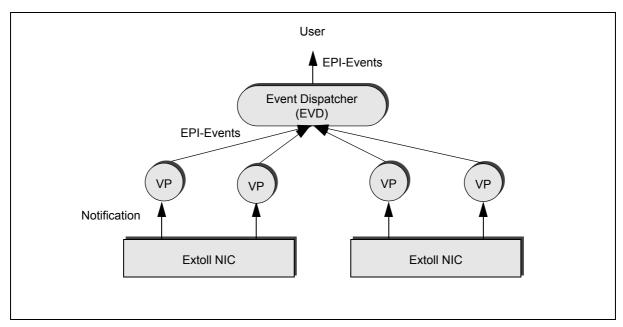

| 5.8.2 EPI Events and Event Dispatcher. 107      |

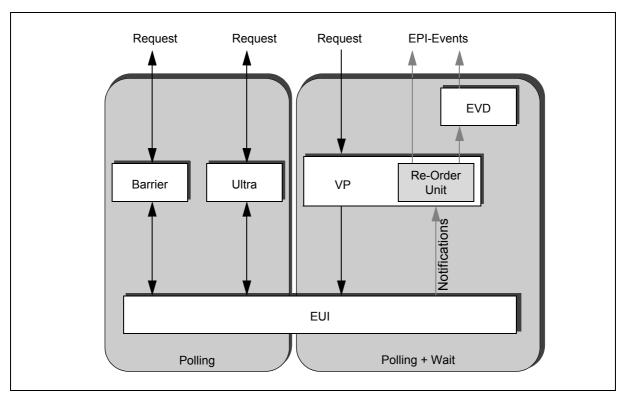

| 5.8.3 Polling and Waiting                       |

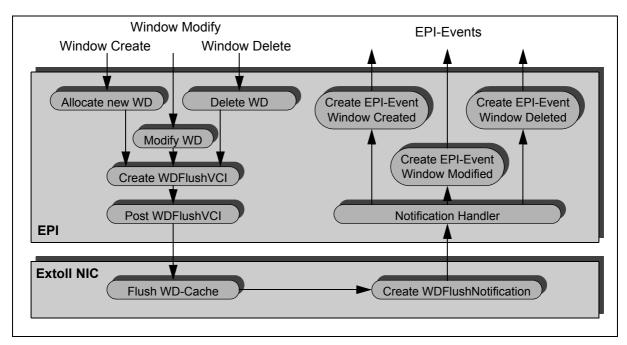

| 5.8.4 VP window management                      |

| 5.8.5 Thread Safety                             |

| 5.8.6 Context Value                             |

| Conclusion & Outlook                            |

|                                                 |

| 6.1 Conclusion                                  |

| References                | 113        |

|---------------------------|------------|

| Glossary                  | 117        |

| Coding Style              | 123        |

| C.1 Coding Styles         | 123        |

| C.2 Naming convention     | 123        |

| C.3 Source Code           | 124        |

| C.4 General               | 126        |

| Linux Select/Poll/Epoll   | 129        |

| D.1 Motivation            | 129        |

| D.2 Classical Approaches. | 130        |

| D.2.1 Select.             | 130        |

| D.2.2 Poll                | 131        |

| D.2.3 Drawbacks           | 131        |

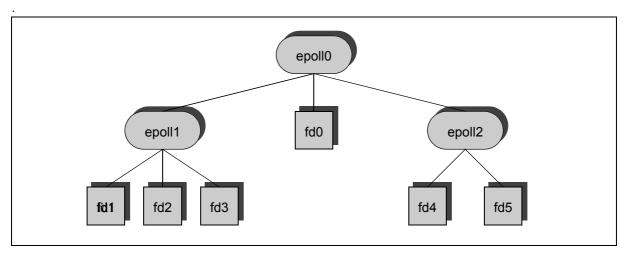

| D.3 New Approach          | 131        |

| D.3.1 EPoll               | 131        |

| D.4 Driver Support.       | 132        |

| Extoll Tools              | 133        |

|                           |            |

| E.1 extoll-config         | 133        |

| E.1.1 Description         | 133        |

| E.1.2 Parameters.         | 133<br>133 |

| E.1.3 Possible Error      | 133        |

| E.2 extoll_mknod          | 133        |

| E.2.1 Description         | 133        |

|                           | 134        |

| E.3 extoll_modules.       | 134        |

| E.3.1 Description         |            |

| <b>▲</b>                  | 134        |

| E.3.3 Possible Errors     | 134        |

| E.3.4 Example.            | 135        |

| E.4 extoll_info.          | 135        |

| E.4.1 Description         | 135        |

| E.4.2 Parameters.         | 135        |

| E.4.3 Possibly Errors     | 135        |

| E.4.4 Example.            | 136        |

| E.5 extollctl             | 136        |

| E.5.1 Description         | 136        |

| E.5.2 Paramters.          | 137        |

| E.5.3 Possibly Errors     | 137        |

|                           | 137        |

| Declaration of Honour     | 139        |

# **List of Figures**

| Decision Tree Syntax                               | . 3 |

|----------------------------------------------------|-----|

| Client/Server Sockets                              | . 5 |

| BSD connection setup                               | . 6 |

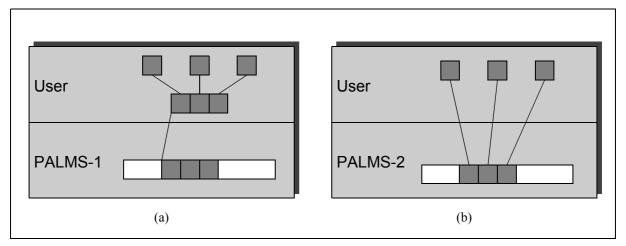

| PALMS layout                                       |     |

| PALMS-1 and PALMS-2 Send/Receive Mechanisms        | . 8 |

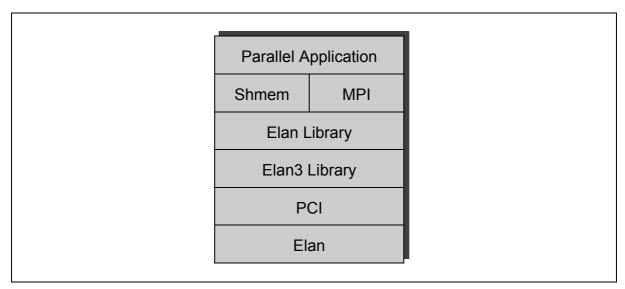

| Elan Software Stack                                |     |

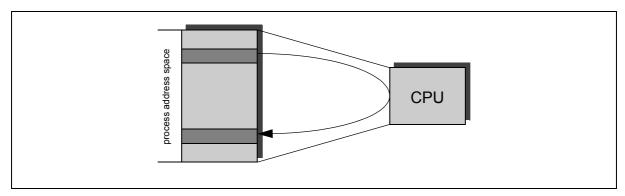

| Single Node Principle                              | 10  |

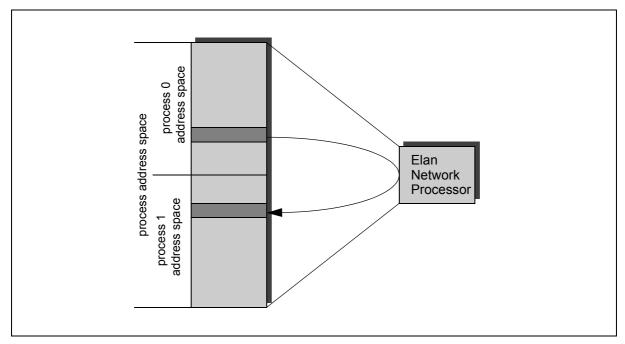

| Quadrics Network Processor                         | 11  |

|                                                    | 12  |

| QP connection and datagram service                 | 13  |

| Memory Window and Registered Buffers               | 13  |

| DAT System                                         | 14  |

| Event Dispatcher                                   | 14  |

| MPI Overview                                       | 15  |

| MPI Communicators                                  | 16  |

| Atoll architecture                                 | 19  |

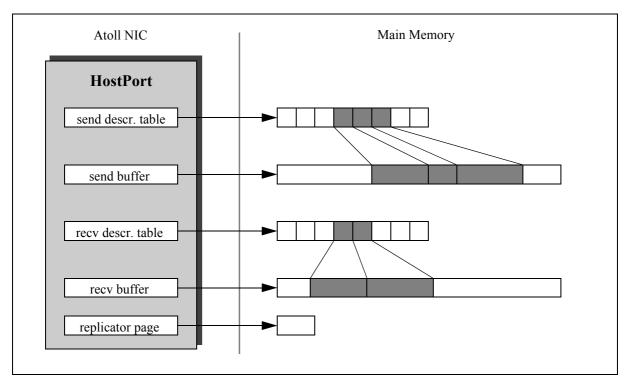

| Atoll Hostport                                     | 20  |

| Process Scheduling                                 | 22  |

| Trigger Page                                       | 23  |

| Conditional Store Buffer                           | 24  |

| CIQ Flow                                           | 25  |

| Virtual Port Descriptor                            | 26  |

| Window Descriptor                                  | 29  |

| VCI Descriptor                                     | 30  |

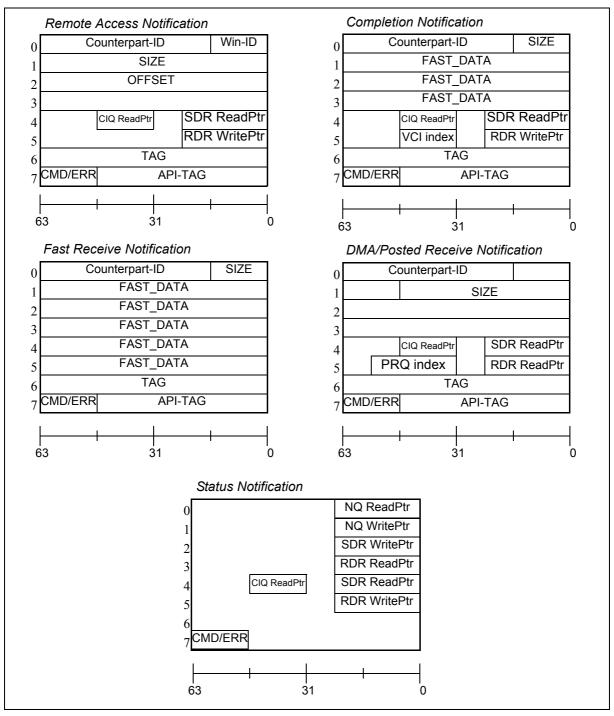

| Notification Formats                               | 33  |

| Decision tree for the Event System                 | 34  |

| Hardware Event Queue                               | 39  |

| Memory Event Queue                                 | 41  |

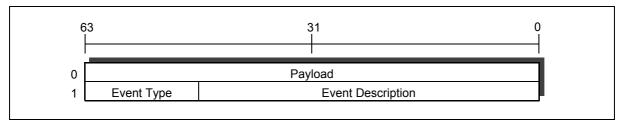

| Event layout                                       | 42  |

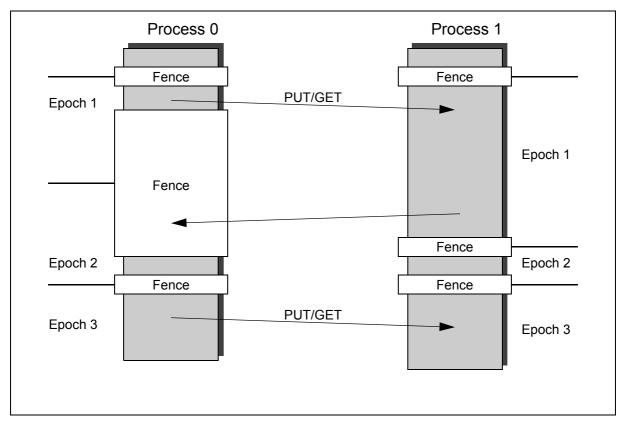

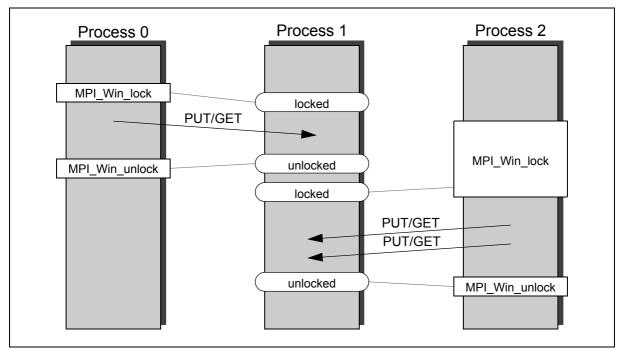

| MPI_Win_fence Operation                            | 44  |

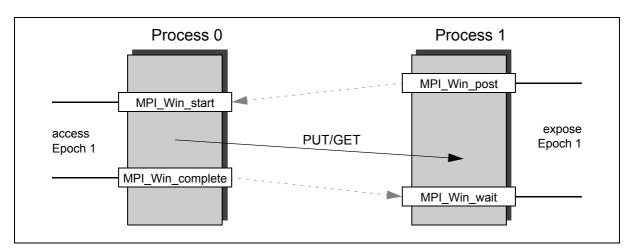

| Synchronisation between a small group of processes | 44  |

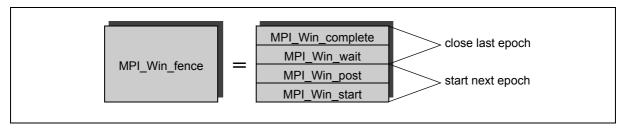

| MPI_Win_fence emulation                            | 45  |

| MPI Window Locking                                 | 45  |

| Orders of communications                           | 46  |

| Fix for RDMA writes in DAPL                        | 47  |

| Send/Receive Decision Tree                         | 49  |

| Send/Receive with Ring Buffers                     | 49  |

| Posted Send/Receive                                | 50  |

| Posted Receive Descriptor Format                   | 54  |

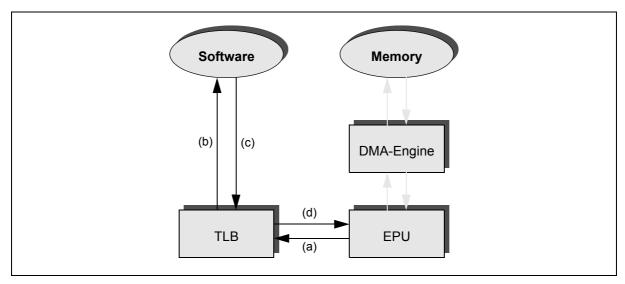

| Cache Management                                   | 55  |

| <u> </u>                                           | 55  |

| Window Descriptor Cache Use Case Diagram           | 56  |

| Context Cache Use Case Diagram                     | 57  |

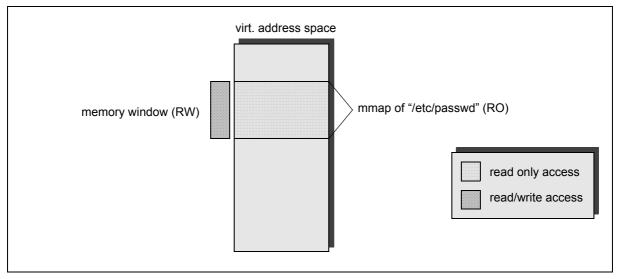

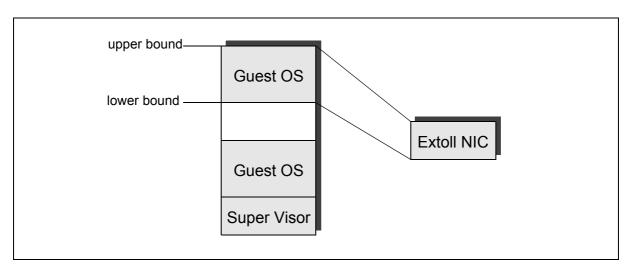

| Memory Window Exploit                 | 58  |

|---------------------------------------|-----|

| Cache miss with direct error delivery | 59  |

| Virtualisation Support                | 59  |

| TLB Use Case Diagram                  | 60  |

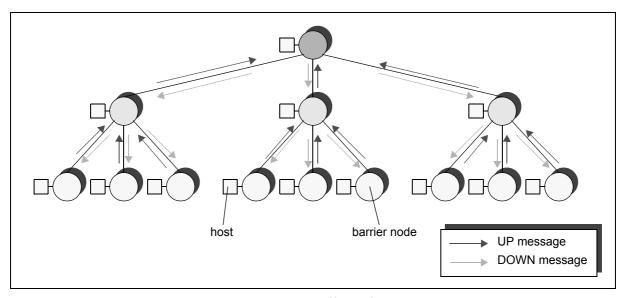

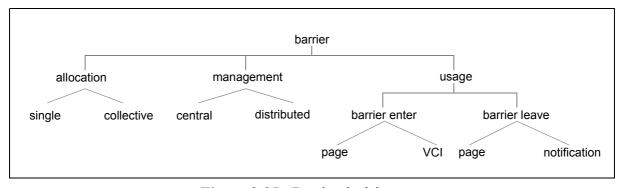

| Extoll Barrier Tree                   | 61  |

| Barrier node                          | 61  |

| Barrier decision tree                 | 62  |

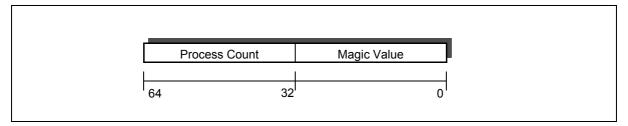

| Barrier Allocation Cookie             | 63  |

| Barrier M:N Mapping                   | 66  |

| ULTRA Communication System            | 67  |

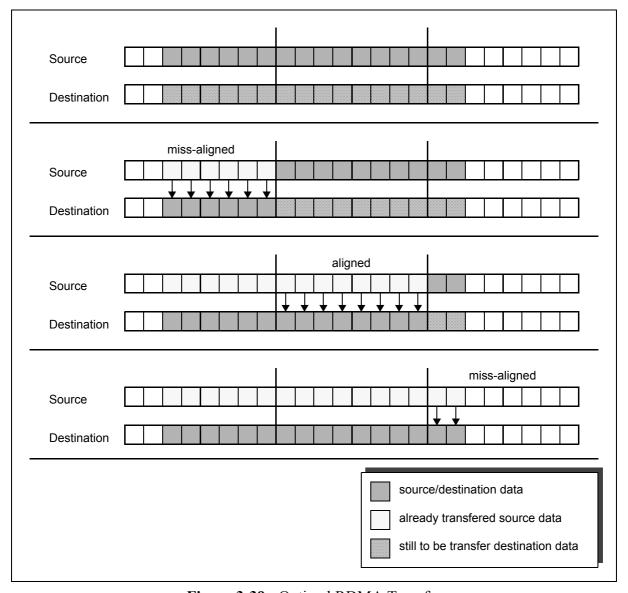

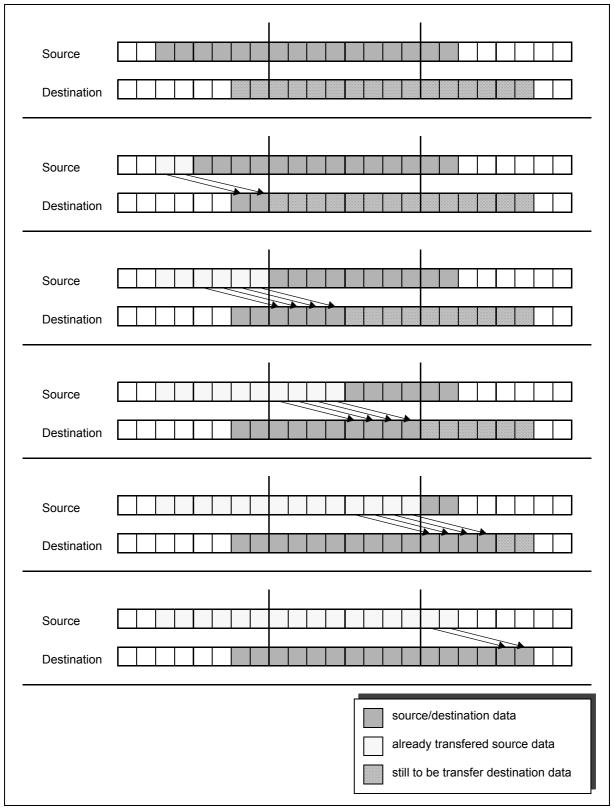

| Optimal RDMA Transfer                 | 69  |

| Worst Case RDMA Transfer              | 70  |

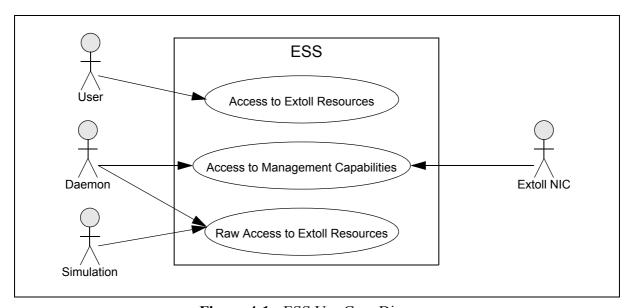

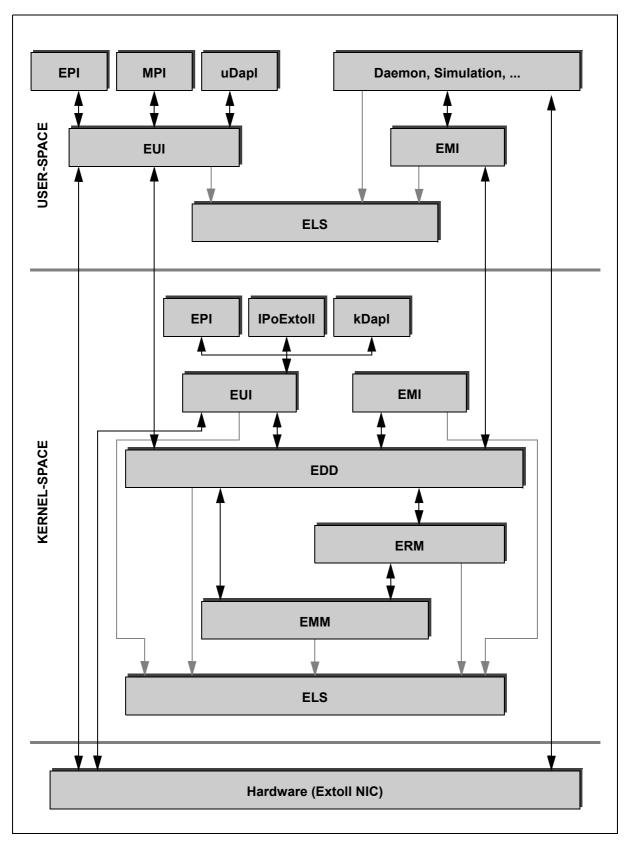

| ESS Use Case Diagram                  | 72  |

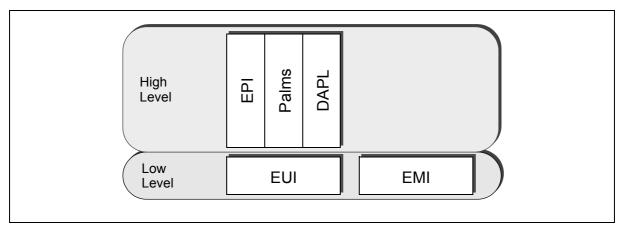

| Extoll API                            | 74  |

| ESS Design                            | 75  |

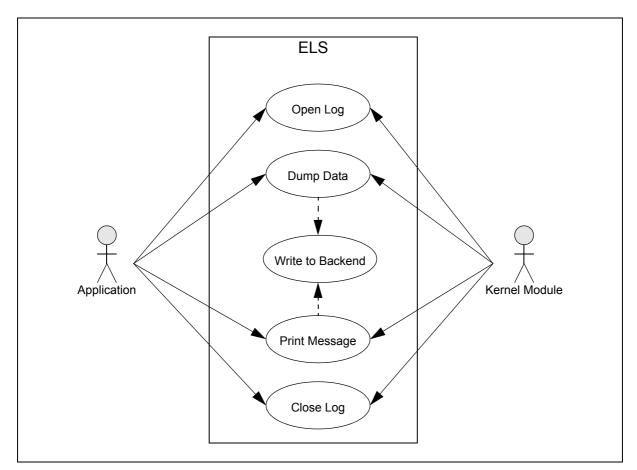

| ELS Use Case Diagram                  | 76  |

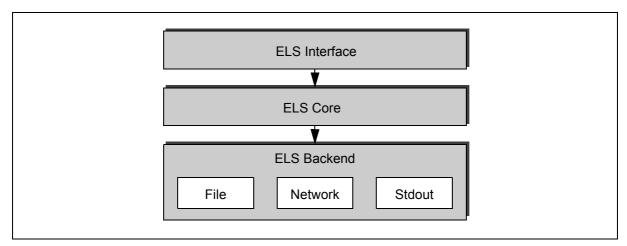

| ELS Design                            |     |

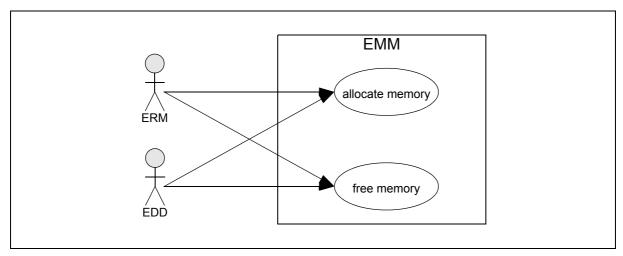

| EMM Use Case Diagram                  |     |

| EMM Design                            |     |

| ERM Use Case Diagram                  |     |

| ERM Design                            | 80  |

| EDD Use Case Diagram                  |     |

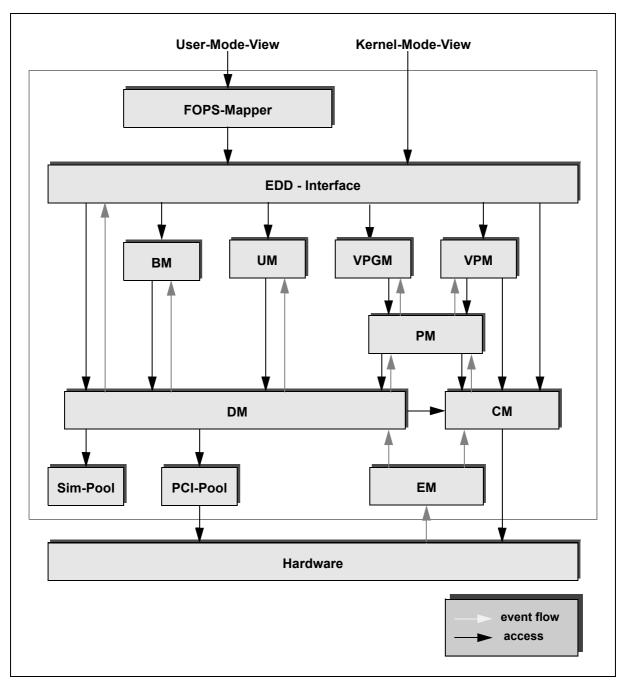

| EDD Design                            |     |

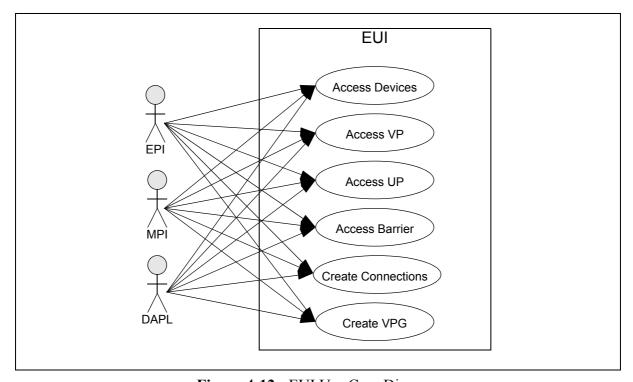

| EUI Use Case Diagram                  |     |

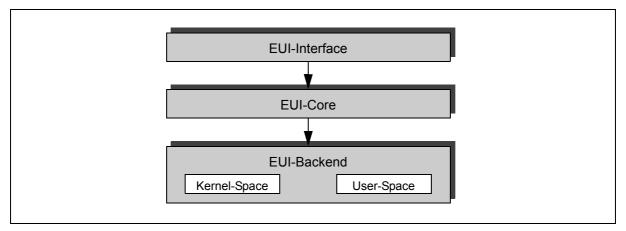

| Design EUI                            |     |

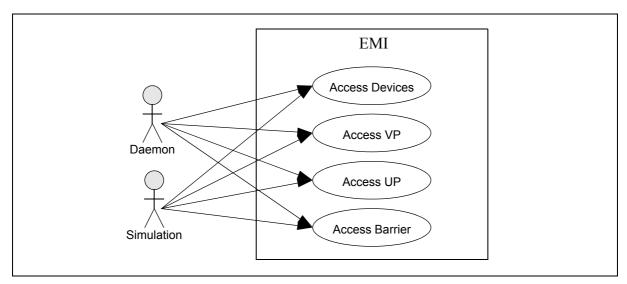

| EMI Use Case Diagram                  |     |

| Design EUI                            |     |

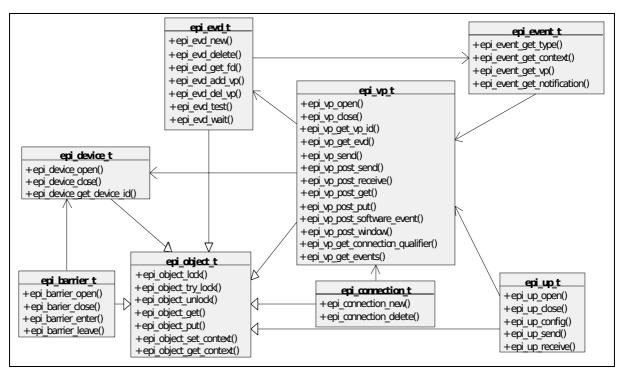

| EPI Use Case Diagram                  |     |

| EPI Design                            |     |

| Symbol Resolving Decision Tree        |     |

| Test-Bench Structure                  |     |

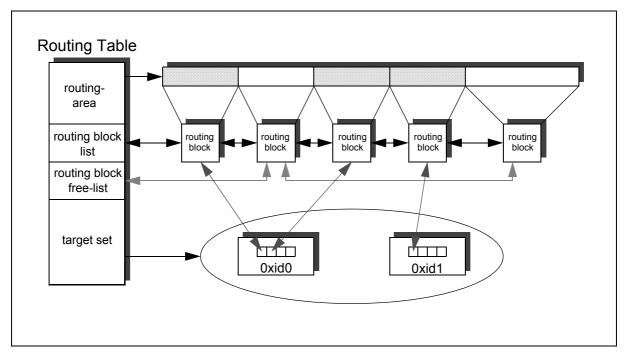

| ERM Routing Table Implementation      |     |

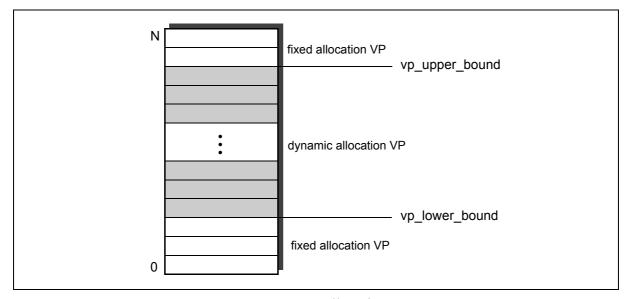

| VP Allocation Map                     |     |

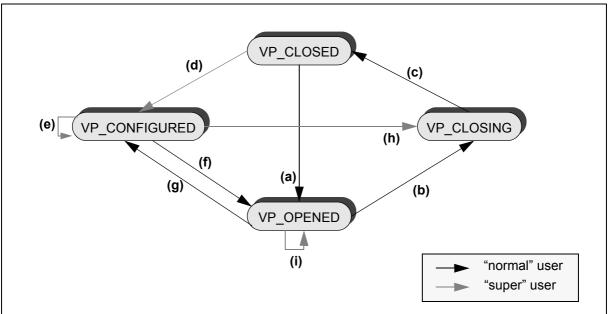

| VP States                             |     |

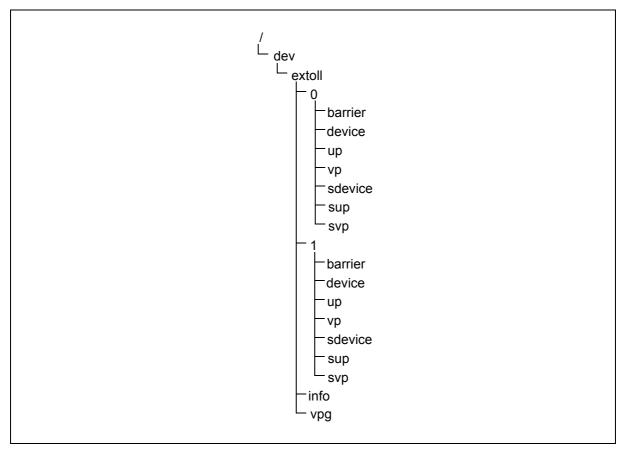

|                                       | 100 |

| * *                                   | 100 |

|                                       | 102 |

|                                       | 103 |

| ,                                     | 104 |

| - ·-                                  | 105 |

|                                       | 106 |

| •                                     | 107 |

|                                       | 108 |

| Window Management                     | 109 |

|                                       | 129 |

| Epoll System                          |     |

| Δρυπ υ γυι <b>υ</b> π                 | 124 |

## **List of Tables**

| Global information for VPs                      | 25  |

|-------------------------------------------------|-----|

| Global information for the Event Queue          | 26  |

| Virtual Port Descriptor Members                 | 27  |

| Pointer metrics.                                | 28  |

| PSW Members.                                    | 29  |

| Virtual Port map                                | 29  |

| WD Members                                      | 30  |

| Information for Notification Descriptors        | 31  |

| Notification Members                            | 31  |

| Notification Error Codes                        | 34  |

| Posted receive descriptor members               | 54  |

| Comparison of FAST_SEND and ULTRA               | 67  |

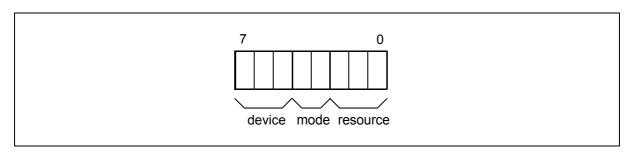

| Minor device number partitioning                | 100 |

| Minor number resources                          | 101 |

| Minor number privileges                         | 101 |

| Quantitative Analyse of the ESS (lines of code) | 111 |

| Parameters extoll-config                        | 133 |

| Parameter extoll_modules                        | 134 |

| Parameters of extollctl.                        | 137 |

## **List of Listings**

| Output Test Bench of ERM           | <br> | <br> | 94    |

|------------------------------------|------|------|-------|

| VP enable/disable Prototypes       | <br> | <br> | 99    |

| Examples of function names         | <br> | <br> | . 123 |

| Examples of object names           | <br> | <br> | . 124 |

| Comment header template            | <br> | <br> | . 125 |

| Examples of correct error checking | <br> | <br> | . 125 |

| Header template                    | <br> | <br> | . 126 |

| Examples of a packed objects       | <br> | <br> | . 127 |

| Prototype Select                   |      |      |       |

| Prototype Poll                     | <br> | <br> | . 131 |

| Prototypes of the epoll functions  | <br> | <br> | . 131 |

| Prototype FOPS Poll function       |      |      |       |

| Example of extoll_modules          |      |      |       |

| Output of extoll info              |      |      |       |

| Output of extollctl                | <br> | <br> | . 137 |

### Introduction

CHAPTER

1

In 1999, the Computer Architecture Group, University of Mannheim, started a research project called Atoll ([ATOLL]). The goal of the Atoll project was to develop a complete SAN for high performance computing (HPC). Besides the NIC a complete software stack, consisting of a management software and an application programming interface (API) called PALMS and a management Daemon, has been developed by Mondrian Nuessle ([NUS03]).

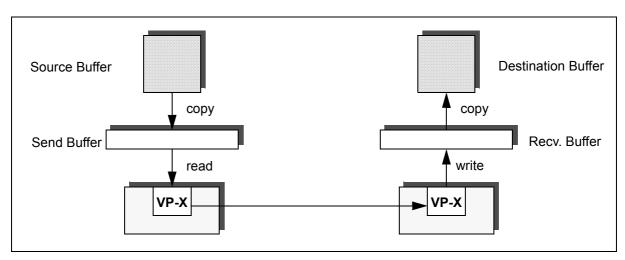

The Atoll SAN proved to be functional and efficient. Extended information about Atoll and Palms can be found in "Atoll Basics" on page 19 and "Atoll - PALMS" on page 7. For additional information about the Atoll design and the Atoll performance refer to [ATOLL99], [ATOLL02], [ATOLL03] and [RZY97]. During the development and usage phase of the Atoll SAN several drawbacks showed up caused by the design of the Atoll NIC (see "Atoll Basics" on page 19). The first issue was the limited number of hostports and therefore the limited number processes that were able to communicate via the Atoll simultaneously. The other problem of the Atoll design was the send/receive mechanism. In the case of the Atoll all data that is sent/received needs to be copied twice, one copy into/from a special send-/receive-buffer and another one between this buffer and the Atoll NIC. This approach has a fairly big impact on the communication performance especially in the case of big messages.

These drawbacks lead to the start of a new research project called Extoll. Extoll stands for "Extended Atoll". The goals of Extoll are to use the Atoll architectural ideas and build a new SAN controller without the drawbacks of Atoll and additional features and improvements. The first goal of the Extoll project is to get rid of the limited supported number of hostports. The Myrinet SAN ([MYRICOM]) has a similar architecture like the Atoll SAN and therefore the same problem. If more hostports are requested than available the software starts to virtualize the hostports. This software virtualisation works in such a way that instead of triggering the hostport directly from user space, the processes call the device driver. The device driver then coordinate access of the different processes to the hostport. With this software virtualisation it is possible to support more hostports than physically available, but with the drawback of a big performance penalty for the indirect communication via the device driver. Therefore the Extoll NIC employs a new approach, which supports hardware virtualisation. With this hardware virtualisation it is possible to support a huge amount of processes with a far less and fixed amount of hardware resources but without any additional software penalty.

The other goal of the Extoll project is to improve the problem of the extra copies for the send receive mechanism. This problem is solved by adding support for RDMA operation to the Extoll NIC. This RDMA operations allow the direct transfer of the data into the device without the overhead via a special send/receive buffer. All currently available SANs, with the exception of the Quadrics QsNet ([QUADRICS]), support RDMA operation only between preregistered buffers. This means, before a RDMA operations can be started the source and the destination processes need to register the source/destination buffers on the NIC. Because the registration of memory is an expensive operation this approach can have a big impact on the performance. Like the Quadrics SAN the Extoll SAN will support RDMA operations without pre-registering of buffers that works with the virtual addresses of the user space process.

Besides the improvements of the Atoll SAN the Extoll SAN also introduces some new features. One of the new features is the support of a hardware barrier. Similar to the crossbar the barrier functionality is inside every NIC and works in a distributed fashion. The next new feature that has been introduced is the Ultra port mechanism. The Ultra port is a special communication mechanism that has been optimised for low latency.

This thesis is part of the Extoll project and has the goal to evaluate the software interface of the Extoll NIC and the design and implementation of the complete software stack. The evaluation includes the comparison of the currently existing software interfaces and their drawbacks. Based on the gained information of the drawbacks of the Atoll and the competitors the whole design of the hostport software interface is made.

The whole project follows the hardware-software co-design paradigm. That means that parallel to the hardware design the software is designed and implemented. The hardware-software co-design approach has the advantage that the overall development time is shorter than by a sequential design. Another advantage is that the software design process can have influences on the hardware design and vice versa.

#### 1.1 Outline

- Chapter 2 "Communication Interfaces" gives an overview of the currently available communication interfaces and highlights the advantages and disadvantages of each presented communication interface.

- Chapter 3 "Extoll Hostport Interface" introduce the Extoll features that will be offered by the final NIC. The rest of this chapter will present the design space for possible software interfaces including all design decisions made.

- Chapter 4 "Design of the ESS" present the Extoll Software Stack design based on the design decisions of the hostport interface.

- Chapter 5 "Implementation of the ESS" will present detailed information about the current implementation.

#### **1.2 Conventions**

#### 1.2.1 Definitions

For this thesis the following conventions and definitions are made:

- **Definition 1-1:** A **process** is a running instance of a program including all variables and states.

- **Definition 1-2:** A **thread** consists of a instruction counter, a register set and stack. A thread always runs inside a process and therefore has access to the whole address space of the process.

- **Definition 1-3:** A **virtual connection** is a logical connection between 2 processes that is described by the communication between these 2 processes.

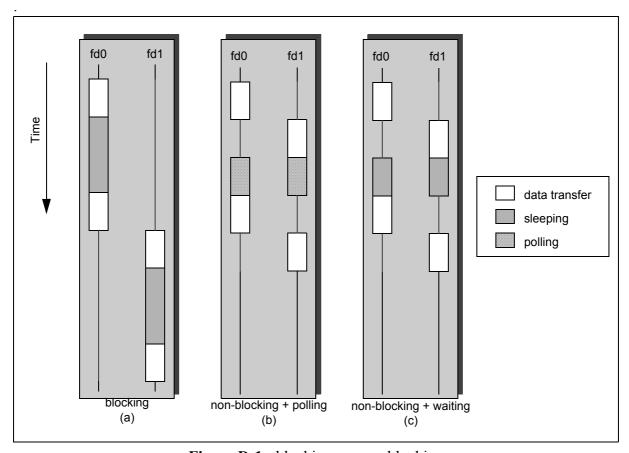

- **Definition 1-4: Polling** means busy polling. When the user busy polls the CPU is non-stop reading and comparing from a certain address to check if a special condition has been reached.

- **Definition 1-5:** Waiting means that the process will not do a busy polling. If the required condition is not reached the whole process will go to sleep. When the required condition has been reached the process will be waked up again.

#### 1.2.2 Decision Tree

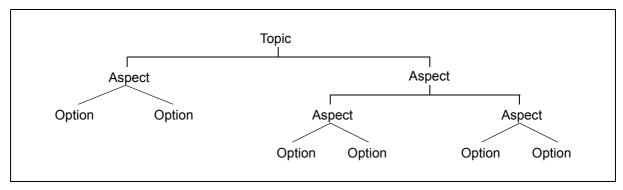

Decision trees are used to visualize different aspects and options of a topic. A decision tree consists of the following objects (see Figure 1-1):

- **Topic**. A topic is the root of every decision tree. A topic describe the topic/problem that is presented by the corresponding decision tree.

- Aspect. Aspects are connected with orthogonal lines. Aspects are either child of the topic or of other aspects. All Aspects of the same parent describe a different aspect of the common parent and are therefore independent from each other.

- Option. Option are always connected with the corresponding aspect by straight lines. All options of an aspect represent alternative approaches for the same aspect. Therefore the options of an aspect are mutual exclusive.

Figure 1-1: Decision Tree Syntax

#### 1.2.3 UML

This thesis uses UML diagrams for visualisation of different aspects. The UML diagrams that are used in this thesis are valid for the UML version 2.0 standard ([FOWLER], [UML]).

## **Communication Interfaces**

This chapter introduces the most commonly used communication interfaces nowadays. The basics of the corresponding interconnect network will be described as much as necessary to understand the corresponding API. The design of an API must fulfil different goals. The first is the efficiency. To reach the best performance on a high performance hardware the software must not introduce a high performance penalty by an inefficient usage of the available resources. On the other side the software layer should abstract the current hardware and offer an easy to use interface to the upper layer. These interfaces that are presented are the BSD Sockets, Atoll PALMS, Myrinet MX, Quadrics, DAPL and MPI.

#### 2.1 BSD Socket API

The BSD socket API ([STE98]) was introduced in 1983 with the release of the 4.2 BSD system. The goal of the BSD socket API was to create a generic interface for accessing computer networks. Today the BSD socket API is the de-facto standard for network programming. The BSD API was originally designed for IP networks. Today, the BSD socket API supports a broad range of different computer networks and protocols.

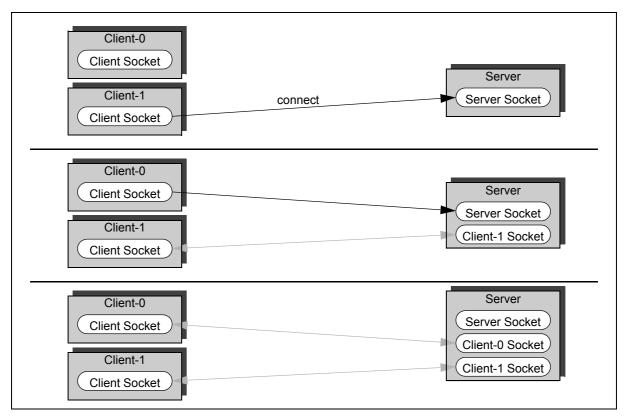

Figure 2-1: Client/Server Sockets

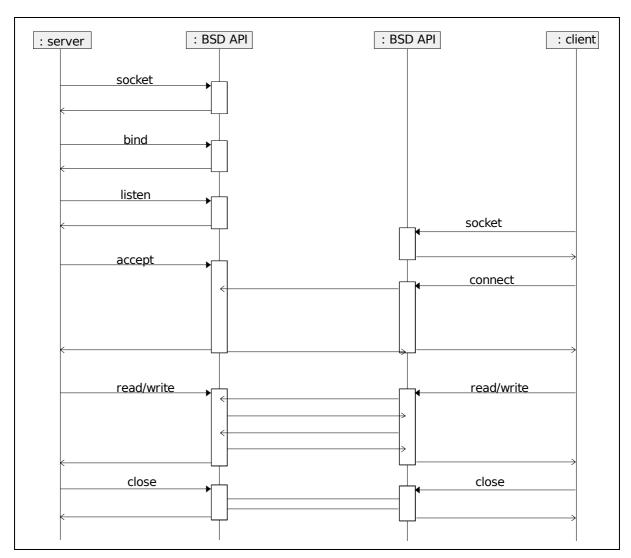

A socket is the central object of the BSD socket API. A socket is an abstract object that describes a connection between two processes. A socket is a tuple of endpoint information. One endpoint information describes the local endpoint of the communication and the other endpoint information the remote endpoint of the connection. A socket communication is build upon the server/client principle. The server side of the communication creates a new socket. The socket is transformed in to a server socket by binding the socket to a certain address. The server process is now able to wait on the server socket for incoming connections. The client side needs the address information of the server socket to establish a connection. The client side first creates a new socket and then connects to the server side. After the server side accepted the connection, a socket for the corresponding client will be created that represents the server endpoint of the connection. The server side is now able to accept more connections via the server-socket and/or communicate with the client via the returned socket (see Figure 2-1). Figure 2-2 visualize the the server/client principle in more details and shows the involved function calls.

Each socket connection is full duplex, this means that each side is able to read/write data at any time. From the user point of view a socket behaves like an ordinary file descriptor. Therefore the communication can be realised with the normal POSIX ([POSIX]) file operation functions. It is furthermore possible to use a socket with the select, poll and or epoll call to realise a non-busy wait. And as a kind of file descriptor a socket is shared amongst all threads of a process.

Figure 2-2: BSD connection setup

#### 2.2 Atoll - PALMS

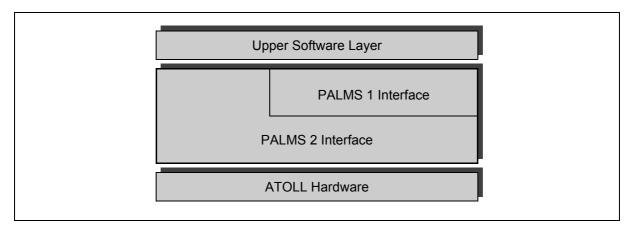

The Atoll-PALMS is the standard API for the Atoll NIC, which offers a user-level communication mechanism. A description of the basic structure of the Atoll NIC can be found in "Atoll Basics" on page 19. The first versions of the Atoll-PALMS were inspired by the BSD-Interface to allow the users a smooth transition to this new API. During the implementation of a MPICH2 port which was based on the first version of the Atoll-PALMS several drawbacks of this interface showed up. Therefore in the second version of the Atoll-PALMS a much lower-level interface has been offered to the upper layer. This new interface is more complex than the interface of the first version but offers more control to the upper layer which is necessary to realise the maximum performance. For backwards portability the Atoll-PALMS interface of the first version has been emulated on the functions of the second version (see Figure 2-3).

Figure 2-3: PALMS layout

The Atoll NIC uses a message based communication mechanism. The idea of this system is to exchange messages between Atoll hostports. To identify a hostport in the network each hostport must have an identifier that is unique across the whole network. After a hostport has been opened by a process on the local Atoll NIC, the process is able to send messages to all other opened hostports in the network. To send a message to a certain hostport, the origin hostport process needs the unique hostport identifier of the target hostport. If the target hostport ID is known, the process can create a connection between the local hostport and the target hostport. The Atoll connections are light-weight connections that do not need to exchange information for an establishment of a new connection. This is possible because the Atoll SAN use sourcepath routing, and creation of a connection mainly consists of a routing table look up. Because the Atoll connections are only unidirectional, both sides need to connect to the corresponding other hostport. The first version of the PALMS-API offered only simple send and receive functions which expect a pointer to a buffer that contains the whole data. These functions automatically performed all necessary tasks to send data including fragmenting of the data. This simple interface had the disadvantage that if several non continuous data buffers need to be send/received, the small data pieces need to be packed into one continuous buffer for the PALMS (see Figure 2-4 (a)). Because of this all data has to be copied twice, first into the temporary buffer for the PALMS and then a second time from the temporary buffer into the send data buffer of the hostport.

To avoid a second copy operation the second version of PALMS introduces direct access to the send/receive buffers. This principle is visualised in Figure 2-4 (b).

Figure 2-4: PALMS-1 and PALMS-2 Send/Receive Mechanisms

As described in "Atoll Basics" on page 19 an active notification mechanism is not supported by Atoll. Therefore polling is the only possibility to detect new data. PALMS offers a special function to poll until new data is available. Since this blocking behaviour is discouraged on many situations the PALMS also offers a non-blocking function which checks if a new message is available or not.

## 2.3 Myrinet - MX

Myrinet is a proprietary cluster interconnect build by Myricom ([MYRICOM]). After Ethernet Myrinet is the most used interconnect for clusters ([TOP500]). Myrinet Express ([MX]) is the most current API for the Myrinet SANs. MX consists of a new API and a firmware. MX allows the user to bypass the operating system and use user-level communication for lower latency.

The central object of the MX API is the endpoint. An endpoint is a virtualization of an NIC. An MX endpoint offers the user a way to use the hardware. An MX endpoint has a similar meaning to MX as a hostport to PALMS. Unlike the Atoll SAN MX supports more than 4 endpoints and an MX endpoint is tagged by an user defined integer value that is used for filtering tasks. The current amount of endpoints that is directly supported by the hardware depends on the current adapter version. If more endpoints are requested than available, then MX will transparently switch from a user-level communication to traditional communication via kernel traps into the device driver. In this traditional communication mode one endpoint in hardware will be shared amongst several processes by multiplexing.

To send data from the local endpoint to a target endpoint the corresponding target address of the remote endpoint must be created. The creation of the remote target address is based on the following information:

- The local endpoint that belongs to the process.

- The remote NIC ID.

- The remote endpoint ID.

- The remote endpoint filter value.

The resulting endpoint address is only valid for this special connection from this local endpoint to the remote endpoint and cannot be used with any other endpoint. The endpoint address represents a unidirectional connection and therefore it can be compared with the Atoll connection. Because the endpoint address is only unidirectional both sides need to create an endpoint address for the corresponding other side to exchange data in both directions.

The whole communication scheme of the MX API is designed to be fully asynchronous. Fully asynchronous means that the initiation of a communication operations is strictly separated by the completion of the operation. For each initiated communication operation an MX request is created and returned to the user. The MX request enables the user to track the status of the initiated operation. MX supports some non-blocking functions to query the request status which allows the user to poll on a request. Besides this non-blocking functions MX also supports functions to wait on a request until a certain state is reached. This wait function will suspend the process until this state is reached.

MX supports message passing communication. For each send operation the user must supply a special matching value that is used to mach the send and receive operation. To receive the message on the remote side a receive needs to be posted with the same matching value. MX guarantees that all send/receive operations will match in-order. It is required to post a receive before the send operation is started. If there is no matching receive MX supports ways to handle this unexpected messages by buffering them until the corresponding receive will be posted.

In the current version 1.0 of MX the support for one-sided communication and collective operations (barrier, broadcast, ...) is missing. The missing functionality will be added in a later version. In addition to the communication via the Myrinet NIC the MX API realizes the communication between processes on the same node via shared memory mechanism. The switch between the NIC and the shared-memory communication is completely transparent from the user point of view. The MX API is available in a thread-safe version and a not thread-safe version. If thread-safety is not required by the upper layer the non-thread-safe library can be used which offers a slightly better latency than the thread-safe version.

## **2.4 Quadrics - Elan Library**

QsNet is a proprietary interconnect solution developed by Quadrics ([QUADRICS]). The core of each QsNet adapter is the "Elan" network processor. To access the functionality offered by a QsNet adapter Quadrics supports two libraries ([ELAN]). Figure 2-5 gives an overview of the quadrics software stack. The Elan3 library offers a low-level interface to a QsNet adapter while the Elan library uses the functionality offered by the Elan3 library to build a high-level interface with the following communication modes:

- Direct memory access.

- Message passing.

- Queue based communication.

- Put/Get based communication.

Figure 2-5: Elan Software Stack

The principle of the QsNet is to build a kind of "network computer" that is inspired by the architecture of a single node computer. If an application is started on a single node this application will be represented by a process that is executed on the CPU. When a process is running on a CPU the whole address space of the process is mapped into the CPU. Data is copied inside the virtual address space of a process, by copying the data from the source buffer into the CPU and then from the CPU to the destination buffer. This principle of a single CPU system is shown in Figure 2-6.

**Figure 2-6 :** Single Node Principle.

The QsNet approach is to map this concept to a parallel system that consists of several nodes. On a parallel system parallel applications are executed. A parallel program consists of several processes that can be run on any node in the parallel system. The amount of processes of a parallel application is determined at the start and is fixed during the whole execution time. All processes of a parallel application are numbered from 0 .. (N-1) with the so called virtual process identifier (VPID¹). This VPID is used to identify a process inside a parallel application. A global address space of the parallel application is formed by arranging the address spaces of the processes in a sequential order of their VPIDs. The addresses of the global address space are build by prefixing the virtual address of each virtual address space with the corresponding VPID (#VPID#VADDR). The global address space is mapped into the quadrics network processor.

<sup>1.</sup> Note that the Quadrics VPID != Extoll VPID.

With the Quadrics network processor it is now possible to copy data inside this global address space from one location to another one, especially from the address space of one process to another one. An example of a parallel application with two processes is shown in Figure 2-7.

**Figure 2-7 :** Quadrics Network Processor

This is the basic concept of the QsNet. The Elan3 library offers an abstraction layer to this functionality that hides the differences of the different QsNet adapters. The library mainly offers functions to initiate the memory copy operation. The memory operations can be associated with two events that will be set when the operation is completed and two cookie values. One event/cookie is for the local side and the other one for the remote side. A process can either poll on an event or wait on an event which will cause process to be suspended until the event is set.

The Elan library works on top of the Elan3 library and offers more communication modes. The message passing interface of the Elan library allows a process to send a message to any other process of the parallel program. Each message can be tagged with a user specified value. The receiver can select by source VPID and/or specified tag which message will be received. Besides the point-to-point operations the Elan library supports some collective operations. The put/get communication mechanism consists of put and get functions that realise write and read operations from the local memory to the remote memory.

All communication operations are able to use the virtual address of the process. Therefore buffers do not need to be registered by the hardware before they can be used for communication.

### 2.5 InfiniBand - Verbs

The InfiniBand Architecture (IBA) is an industry-standard architecture for server I/O and interserver communication. The IBA was developed by the InfiniBand Trade Association ([IBTA]) as a replacement for the current I/O bus architectures. The InfiniBand architecture specifies the whole system from the link up to the software interface to control an InfiniBand adapter

([PFISTER]). The software interface is called Verbs ([VERBS]) and consists of function prototypes and the corresponding semantic. The exact implementation of the Verbs is not specified and vendor specific. The InfiniBand architecture defines the following services:

- Reliable Connections (RC)

- Unreliable Datagram (UD)

- Unreliable Connection (UC) [optional]

- Reliable Datagram (RD) [optional]

- Raw IPv6 Datagram & Raw Ethertype Datagram [optional]

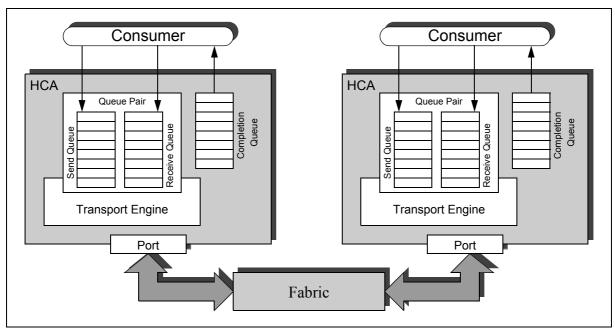

Figure 2-8: InfiniBand HCA

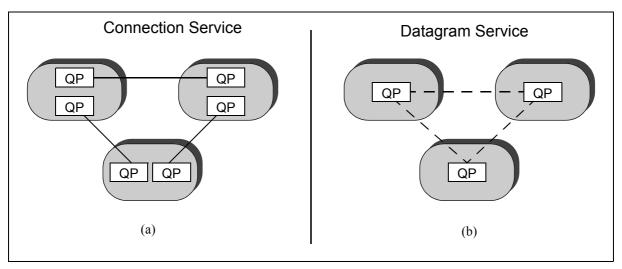

The central part of each InfiniBand communication is the so called queue pair (QP). The queue consist of two queues, one send and one receive queue (see Figure 2-8). If the user wants to start an operation the user posts a descriptor that describes the operation in the corresponding send or receive queue. If the operation is an operation that actively transmits data the descriptor will be fetched by the transport engine and be processed. The data will be transported via the InfiniBand fabric to the destination host channel adapter (HCA). On the destination side the data will be processed. If the data needs to be received the next descriptor from the receive queue will be fetched to determine the destination of the data. On both sides a completion will be generated after the operation is completed. The created notification will be stored in a completion queue. If a connection service type is used then a connection is always exclusively established between two QPs. A QP can only be member of one connection which leads to the problem that for several connection several QPs per process needs to be allocated (see Figure 2-9 (a)). Only one QP is necessary to communicate with several other processes when the datagram service is used (see Figure 2-9 (b)).

Figure 2-9: QP connection and datagram service

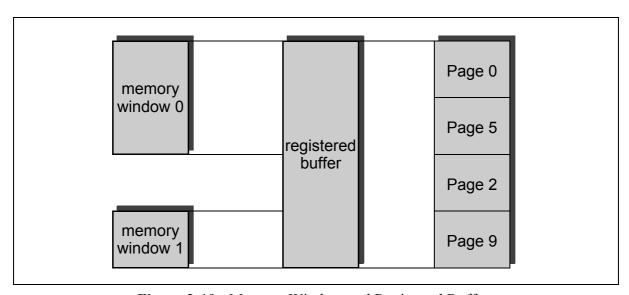

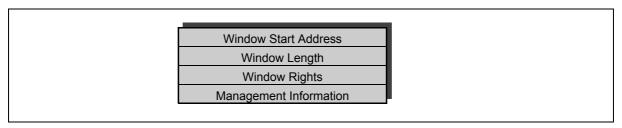

With the Verbs specification InfiniBand defines a standard set of functions to implement the previous explained operations. The Verbs offer functions to allocate and manger the introduced queues. InfiniBand supports message passing communication, via posted sends and receive, and remote memory operations. All communication operations are asynchronous. After the communication operation has been initiated the user will receive a completion when the operation has completed. It is possible to either poll for new completions or use a non polling wait function that suspends the process until a new completion is available. Additionally, the user can register a callback function that is called when a new completion in the completion queue is created. Every memory that is used by a communication operation must be registered with the HCA. A registered buffer can be further sub-divided into memory windows that have different access rights (see Figure 2-10). While the registration of a buffer can be a slow operation that involves a kernel trap, the creation of a memory window is completely done in user space by posting a corresponding operation to the QPs.

Figure 2-10: Memory Window and Registered Buffers

#### **2.6 DAPL**

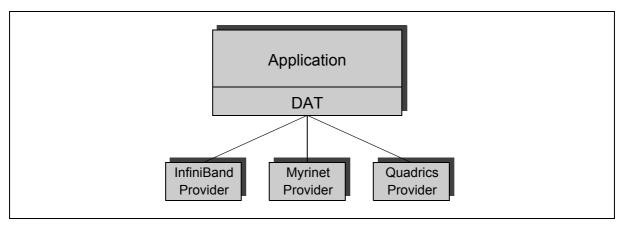

The Direct Access Application Library (DAPL) is an API that is suitable for all RDMA-capable interconnect networks. DAPL is a generic API interface specification that abstracts from the different interconnect networks and operating systems. The DAPL specification consists of a user-level (uDapl) and a kernel-level (kDapl) API specification. The whole specification of the DAPL interface is maintained and coordinated by the DAT-Consortium ([DAT]). The concept of DAPL is that all applications that have been written for DAPL are able to communicate via different interconnected networks without re-building. This is realized by selecting the used provider at the start of each DAPL program. A provider is a module that is dynamically loaded and offers the functionality for a certain communication system to the DAPL interface (see Figure 2-11).

Figure 2-11: DAT System

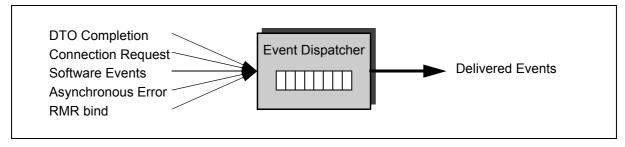

The connection setup in DAPL is similar to the BSD socket server/client approach. The server side creates a service point. A service point is like an open port that allows clients to create a connection. The DAPL endpoints are similar to BSD sockets and represent a connection to one remote node. The connection setup works similar to the BSD socket approach. The active side creates an EP and creates a connection to the remote service point. After the server side accepted the connection a corresponding EP for the connection will be returned. DAPL offers all common types of data transfer operations (DTO). This DTOs are posted send, posted receive, RDMA read and write. The DAPL communication is asynchronous. Like in InfiniBand the user must post a receive operation to receive data transferred by a send operation. The user receives all kinds of information (DTO completion, connection request, disconnection, ...) via events. The central objects of the event system are the event dispatchers (ED). An event dispatcher looks like an event queue that collects events from different event streams (see Figure 2-12).

Figure 2-12: Event Dispatcher

DAPL requires that all memory buffers have been registered before they are used with a DTO operation. Like InfiniBand DAPL supports the creation of memory windows on a registered buffer (see Figure 2-10).

#### **2.7 MPI**

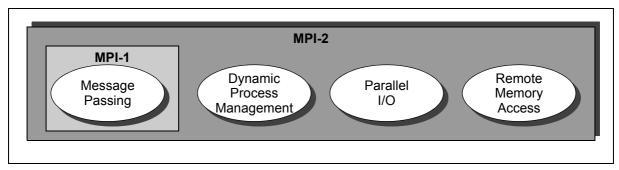

At the beginning of parallel systems each system had his own API for using the parallel resources. This lead to the problem that a program that had been developed on a certain parallel system was not likely to run on any other system. Therefore independent software providers had to write a version of their product for each system they wanted to support. To solve this problem several companies and research organisations formed the MPI-Forum ([MPIFORUM]). The goal of this forum was to define an unique API for writing parallel programs. This API was called MPI which stands for "Message Passing Interface". The idea of this approach was to have a single API and a program that has been written with this interface would be able to run on different parallel systems without modification. The only thing that needs to be adapted to the different systems is the MPI implementation. Today MPI is the de facto standard for writing parallel programs with existing implementations for all major systems. For different reasons the first version of the MPI standards covered only message passing. The second and most current version the MPI standard extended the first version by adding support for parallel I/O, dynamic process management and remote memory access (see Figure 2-13).

Figure 2-13: MPI Overview

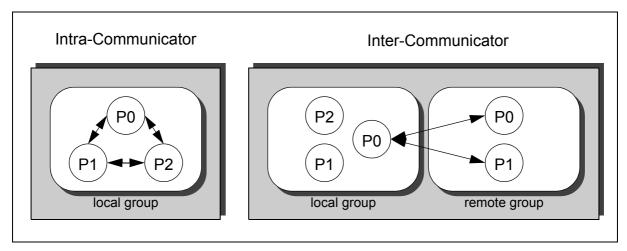

The basic object of MPI is a so called communicator. A communicator is an abstract object that allows the user to exchange messages between the processes that are associated with this communicator. Every communicator contains between one and two progress groups. Communicators with only one process group are so called Intra-Communicators. An Intra-Communicator can only be used to exchange data between processes of a single process group. A communicator with 2 process groups is called Inter-Communicator and can be used to exchange messages between 2 different process groups. This 2 different kind of communicators are visualised in Figure 2-14. Each process in a process group is identified by a unique number, the so called "rank". The first process of a group always gets the rank 0, the second rank 1, and so on. The order of the processes is not defined by MPI and depends on the implementation. This means that the same processes that is member of 2 different process groups can have a different rank in each group and that the same rank on different groups can belong to 2 different processes.

Figure 2-14: MPI Communicators

The point-to-point communication between 2 processes is realised via a send on the sender side and a matching receive on the receiver side. The matching of a send and a receive operation is based on the used communicator, the source process rank and the specified tag. The MPI standard requires that send operations with the same matching information must be delivered in-order. The MPI standard specifies blocking and non-blocking send/receive operations. The semantic of MPI defines that when a blocking send returns the user is able to use the data buffer again without any danger. This does not mean that the corresponding send already finished or that the remote side already received the data. If non-blocking operations are used, the user gets a request for the corresponding operations that allows the user to keep track of the status of the operations and/or wait until the operations are finished. Additionally to the point-to-point operations the MPI standard specifies several collective operations. The collective operations can be sub-divided in scatter-, gather- and reduce-operations. A special collective function is the barrier because this function transfers no data and is only used for synchronisation.

When an MPI program is started all processes are grouped in one big process group that is associated with the global communicator  $MPI\_COMM\_WORLD$ . Because this static approach is limiting the Dynamic Process Management (DPM) has been integrated. The DPM consists mainly of one function to start a certain number of processes in a new process-group. This function returns an Inter-Communicator that allows communication between the process groups.

To avoid a bottleneck in the I/O performance and to increase portability the MPI standard defines a set of file operations. The MPI file operations were inspired by the POSIX file operations. While the opening and closing of a MPI file is a collective operation among the processes of to the used communicator, the file may be accessed by each process separately. Several file pointers per MPI file are managed, one global (shared) file pointer that is valid for all processes and one local file pointer per process.

The last part of the MPI standard covers Remote Memory Access (RMA). RMA allows a process to directly access and modify the memory of another process. MPI defines 2 different modes of RMA operations, the passive target and the active target mode. In the active target mode the target process is actively participating in the execution/completion of an RMA operation. In contrast to the active target mode the passive target mode no involvement of the target process is required. The first thing that needs to be done to share data via RMA is to create a MPI memory window. A MPI memory window is a description of an area of memory that is accessible by other processes. The creation of a MPI memory window is a collective operation that must be done amongst all processes of the used communicator. When the MPI window has been suc-

cessfully created each processes of the communicator is able to access the corresponding windows of all other processes in the communicator. For the real modification of the remote memory the MPI standard defines a get, put and accumulate function. The get function is used to read data from a remote memory into a local buffer while the put operation writes data from a local buffer to a remote memory window. The accumulate function applies local data with a function to a remote memory window. The functions for accumulation are all logical and arithmetical base functions (e.g. AND, ADD, OR).

#### 2.8 Conclusions

As seen in the previous sections all communication systems (except the BSD sockets and the PALMS) support the following features to achieve the maximum possible performance:

- Asynchronous Communication. Asynchronous communication means that the user triggers the communication operations and will get notified when the triggered operation has ben completed. This approach allows to overlap the communication and computation and therefore leads to the maximum exploration of parallelism.

- **RDMA Capabilities**. RDMA capabilities allow the user to directly transfer to/from remote memory of another process. With this feature it is possible to realize true zero copy operations.

- Event Driven. As seen it is important to have an active notification system for the user which allows a non polling waiting operation. With this event driven approach it is possible to save CPU time and therefore increase the performance.

## **Extoll Hostport Interface**

In this chapter a design space analysis of the hostport interface is presented. First a short overview of the Atoll design is given. After the historical overview of Atoll a short description of the Extoll basic concepts is presented. Then each aspect of the Extoll hostport interface will be analysed.

#### 3.1 Atoll Basics

#### 3.1.1 Atoll Architecture

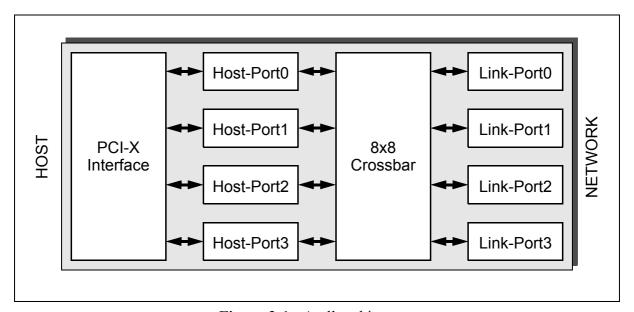

Figure 3-1: Atoll architecture

After the PCI-X interface that transforms the PCI(X) interface into an internal interface, the Atoll has 4 hostports. Each hostport is represented by a hardware structure. Each hostport can be seen as a communication unit. In the Atoll network messages can be send from one hostport to another one (including to itself). To get the maximum performance, especially low latency, the Atoll uses user-level communication. In the case of user-level communication the user process is able to trigger operations directly from the user space without the need of trapping into the operating system. Because multiple access from several different processes at the same time would lead to problems a hostport is exclusively associated with one process. The Atoll offers 4 hostports which limits the maximum number of processes per node to 4\*(number of Atoll NICs).

During the design phase of Atoll the first dual processor systems were available and 4 processor systems were expected in the near future. This was one of the reasons for the limitation to 4 host-ports. Since the start of the Atoll project the technology made huge progress. Today it is possible to build nodes with 8 CPUs and more. After the introduction of hyper-threading (HT) real multi-core CPUs were introduced. If a user puts 8 dual-core CPUs into one node he gets a 16 CPU node. The user could run 16 processes in parallel, but is limited to run a maximum of 4 processes because of the limitations of the Atoll NIC, this is unacceptable.

Another problem of the Atoll NIC, and many other SANs, is that the data needs to be copied into/from special send/receive buffers. These extra copies limit the performance dramatically. For this reason many SAN controllers were extended to support Remote Direct Memory Access operations (RDMA). RDMA operations enable a device to read/write data directly from the process memory address space without the need to make a copy in the send/receive buffers. With this feature it is possible to realize a zero copy protocol.

Figure 3-2: Atoll Hostport

As shown in Figure 3-1 the Atoll NIC supports up to 4 hostports. All hostport have their own fixed hardware resources. Each hostport has a send/receive data buffer and a corresponding descriptor table. The send/receive data buffers contain the data of the messages that should be send or have been received. The send/receive descriptor tables contain the descriptors, one for each message in the corresponding buffer. All data buffers and descriptor tables are managed as ring-buffers with wrap-around semantic. To avoid the expensive hardware accesses each hostport mirrors its status information into a page in the main memory, the so called 'replicator page'. In Figure 3-2 the relationships between the data buffers and descriptor tables are visualised. The ring-buffers are managed via read- and write-pointers. The state of an empty and a full ring-buffer is implicitly represented by the read-/write-pointer. This avoids an extra variable for an empty and full state. That approach not only reduces the number of updates it also avoids race

conditions. Because Atoll does not support a notification mechanism for newly arrived messages each process has to poll on the replicator page to check and wait for new messages. This behaviour leads to very small latency but also to a very high CPU utilisation.

#### 3.1.2 Atoll Send

A message is sent by executing the following steps:

- Copy the whole data into send data buffer.

- Update the write pointer of the send data buffer.

- Create a new descriptor in the send descriptor table.

- Update the write pointer of the send descriptor tables. This update operation triggers the Atoll NIC to fetch the next descriptor from the main memory.

- Atoll fetches all the data from the memory and sends it to the destination.

- Atoll updates the read pointer of the send data buffer.

- Atoll updates the read pointer of the send descriptor table.

#### 3.1.3 Atoll Receive

A message is received by the following steps:

- The Atoll NIC copies the message data into the receive data buffer.

- The Atoll NIC creates a message descriptor for the received message in the receive descriptor table.

- The Atoll NIC updates the receive data write pointer.

- The Atoll NIC updates the receive descriptor write pointer.

- The process detects that there is a new receive descriptor in the receive descriptor table. The process use the receive descriptor to consume the message from the receive data buffer.

- The process update the read pointer of the receive data buffer.

- The process update the read pointer of the receive descriptor table.

## **3.1.4 Summary**

The Atoll SAN has been proven to work and to be efficient. During the whole development process the following main disadvantages have been figured out:

- The Atoll only supports 4 hostports.

- The Atoll only supports polling.

- The Atoll only supports message based data transfers (extra copies).

For more information about the Atoll design refer to the dissertation of Larz Rzymianowicz ([RZY97]).

# 3.2 Extoll Overview

This section gives a short overview of the Extoll basics. For further details refer to the diploma thesis of Dirk Franger ([FRANGER04]).

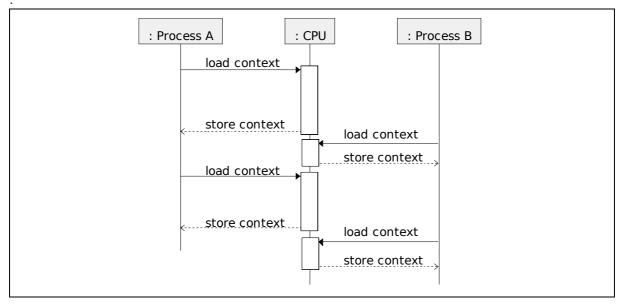

Figure 3-3: Process Scheduling

A first approach to overcome the limited number of hostports could be to increase the number of hostports that are supported by the hardware. This approach has several disadvantages. The first disadvantage is that this approach does not solve the problem that the hardware limits the available number of hostports, it only increases the threshold when the problem occurs. Another disadvantage is that if the number of directly in hardware supported hostports is increased, this also increases the area of the die, the power consumption and so on. Because of these disadvantages it is necessary to support a large number of hostports without a direct representation in hardware.

This kind of problem also occurs on a computer system where an unlimited number of processes runs simultaneously on a fixed amount of CPUs. On a computer system this problem has been solved by virtualisation of the resource CPU. Instead of associating a process with a certain CPU a process is running on a virtual CPU. A virtual CPU consists of a set of registers that represent the current context of a process. Several processes can now be executed by time multiplexing the CPU(s) between the processes. The switching between two processes is done by storing the register set (context) of the actual running process into the main memory. Then the register set (context) of the next process is loaded into the CPU and executed (see Figure 3-3).

This approach is adopted by the Extoll to form a communication processor. In this communication processor a hostport will not be associated with a specific hardware hostport. A hostport is now virtualized and is therefore called virtual hostport (VP). The current state of a VP is described by a VP descriptor (context). This VP context is loaded into the Extoll when the hostport needs to perform an action. On a computer system the operating system is responsible for the decision which process is running on the CPU. This behaviour is highly discouraged in the Extoll design because the synchronisation via the operating system would increase the latency too much. Because the Extoll is supposed to communicate via user-level communication each VP that needs to perform an action must be able to cause a switch to his context from user space. A

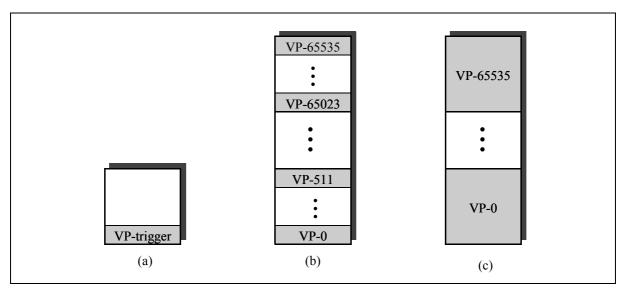

general problem is that a switch to the current process can only be done when there is not already another VP in execution. In the case that there is another VP running the request of the current VP must be rejected and the VP must perform the request again. To perform a switch the Extoll requires the VP identifier (VPID) of the VP that wants to perform an operation. A solution could be to map I/O space from the Extoll NIC into the address space of every process that opened a VP. Each process that wants to trigger an operation via a VP write the corresponding VPID at the beginning of the I/O space (see Figure 3-4 (a)). This approach has the disadvantage that the VP that triggers the Extoll via this I/O space does notdoes not have the possibility to detect if the Extoll accepted the request, because write operations have no feed back.

Figure 3-4: Trigger Page

The problem with the missing feedback can be solved by replacing the write operation with a read operation. The feedback information can be returned in the value that is read from the device. If all VPs would read from the same location in the I/O space the Extoll could not differ between the different VPs. Therefore each VP reads from a different place in the I/O space. The offset of the read operation determines the VPID (see Figure 3-4 (b)). This approach works but has the disadvantage that there is a security issue. Because all processes have access to the same I/O space it is possible that one process reads from the offset of another process. This issue is solved by increasing the trigger area of each VP to the size of one memory page the so called trigger page. Every process maps only the trigger pages of the VPs that have been opened (see Figure 3-4 (c) and Figure 3-5).

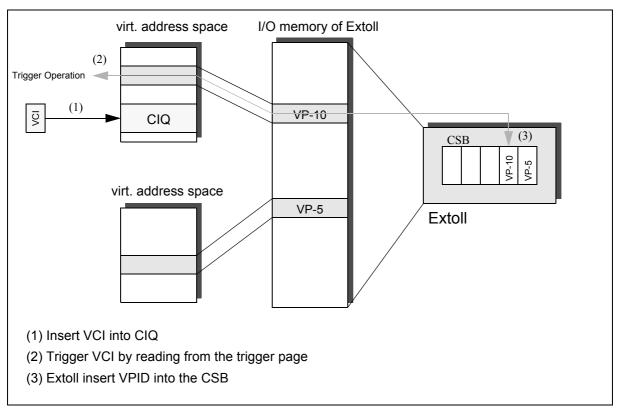

The trigger page solution solves all of these problems. As mentioned before every process of a VP that has to perform an operation triggers Extoll via the trigger page. This should cause the Extoll to switch to the current VP. But if Extoll is already executing another VP this switch cannot be performed. In this case the process has to poll on the trigger page until the Extoll NIC has accepted the request to switch to the current VP. On a busy system with much communication this case will be the standard. To overcome this situation the Extoll has a buffer for incoming request of the trigger pages. If the request for a VP has been successfully inserted into the buffer the Extoll guaranties that the corresponding VP will be executed in the future. This buffer is called conditional store buffer ([CSB])(see Figure 3-5).

Figure 3-5: Conditional Store Buffer

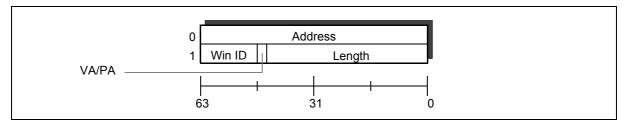

A missing feature of the Atoll design was the lack of zero-copy functionality. Therefore Extoll supports RDMA operations. Extoll will support Get and Put operations for reading / writing of the memory of a remote process. The Extoll NIC does not require to pre-register a buffer on the hardware but requires that the buffers that are used for RDMA operations are located inside a memory window. Like the QsNet adapters from Quadrics the Extoll NIC will be able to directly handle virtual addresses. Unlike QsNet, Extoll has no table-walk engine to translate the virtual addresses to physical addresses which are needed by the DMA engine. Therefore Extoll will only have a translation-lookaside buffer and the real address translation is done in software.

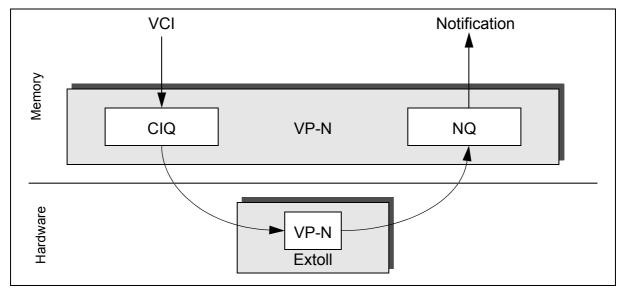

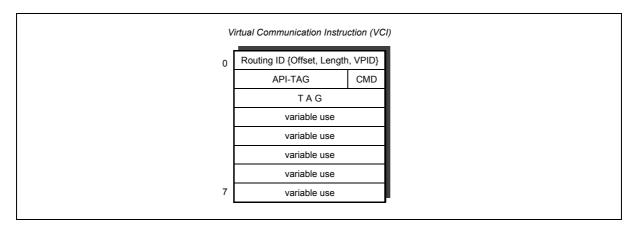

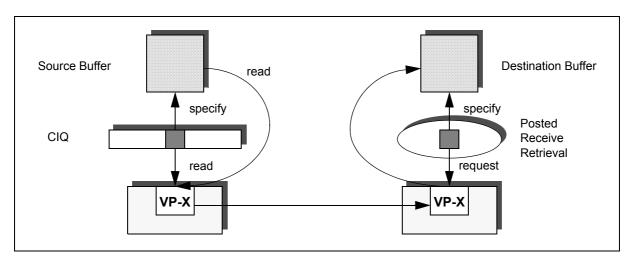

Unlike the Atoll NIC, the Extoll NIC will support notifications for the users. Notifications are supported for the completion of previously triggered operations and for the arrival of new messages. The operations that can be executed are called virtual communication instructions (VCI). The VCIs are stored in a physically continuous buffer in memory that is managed as a ring buffer. This buffer is called communication instruction queue (CIQ).

To execute a new operation a VP must create a VCI that describes the operation. This VCI is inserted into the virtual communication instruction queue (CIQ). The VP triggers the Extol NIC via the mapped trigger page. After the VPID has been successfully inserted into the conditional store buffer Extoll will load the corresponding context. After the context has been loaded the next VCI of this VP will be fetched and executed. After the execution a corresponding notification will be stored in the notification queue (NQ).

Figure 3-6: CIQ Flow

To achieve the highest possible performance the Extoll SAN supports a special communication scheme called ultra low latency transaction (ULTRA). The ULTRA mechanism is designed for small messages (<= 64 Bytes) and use a PIO approach. More details of the ULTRA unit can be found in the diploma thesis of Heiner Litz ([LITZ05]). For fast synchronisation between processes the Extoll SAN also supports a hardware barrier.

# 3.3 Global Information for VPs

Table 3-1 lists the global information for each VP.

| Name                    | Description                                                                                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPD table base address  | The start address of the VPD table in the memory. The address must be a <b>physical address</b> .                                                                    |

| VPD upper base          | Specifies the end address of the VPD table. Together with the base address the length of the VPD table is specified. The address must be a <b>physical address</b> . |

| CIQ length <sup>a</sup> | Specify the length of the CIQ in bytes. The length value must be a multiple of the VCI size.                                                                         |

| WDT length <sup>a</sup> | Specify the length of the WTD in bytes. The length value must be a multiple of the window descriptor size                                                            |

| SDR length <sup>a</sup> | Specifies the length of the SDR in bytes.                                                                                                                            |

| RDR length <sup>a</sup> | Specifies the length of the RDR in bytes.                                                                                                                            |

| NQ length <sup>a</sup>  | Specify the length of the NQ in bytes. The length value must be a multiple of the notification size                                                                  |

**Table 3-1:** Global information for VPs

a. This value is global and specifies the length of each VPD.

# 3.3.1 Global Information for Event Queue

Table 3-2 lists the global information that configure the event queue.

| Name                | Description                                                                              |

|---------------------|------------------------------------------------------------------------------------------|

| EventQ base address | This is the physical base address of the event queue.                                    |

| EventQ length       | The length of the event queue in amount of events that can be stored in the event queue. |

| EventQ ReadPtr      | The read pointer of the event queue. This pointer is managed by software.                |

| EventQ WritePtr     | The write pointer of the event queue. This pointer is managed by hardware.               |

**Table 3-2:** Global information for the Event Queue

# **3.4 Extoll Descriptors**

## 3.4.1 Virtual Port Descriptor

Figure 3-7: Virtual Port Descriptor

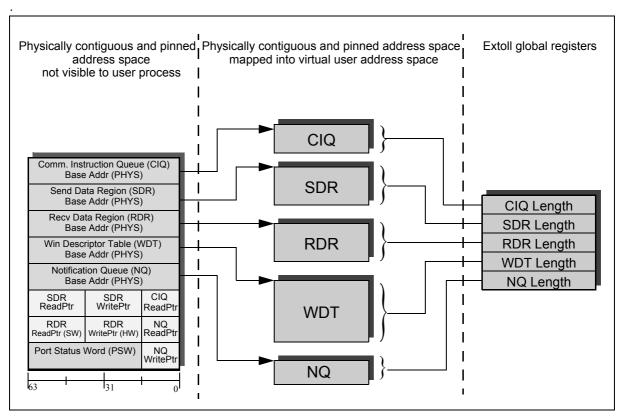

The virtual port descriptor (VPD) describes the current state of a virtual port. Table 3-3 lists the members of the virtual port descriptor. The current layout of the virtual port descriptor is shown in Figure 3-7.

| Name             | Description                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CIQ base address | The <b>physical address</b> where the CIQ starts in main memory. The length of this queue is equal for all virtual ports. See Table 3-1 for more information.                                   |

| SDR base address | The <b>physical address</b> where the send data region starts in main memory. The length for the buffer is the same for all virtual ports. See Table 3-1 for more information.                  |

| WDT base address | The <b>physical address</b> where the window descriptor table starts in main memory. The length of this descriptor table is the same for all virtual ports. See Table 3-1 for more information. |

| RDR base address | The <b>physical address</b> where the receive data region starts in the main memory. The length for the buffer is the same for all virtual ports. See Table 3-1 for more information.           |

| NQ base address  | The <b>physical address</b> where of the notification queue starts in the main memory. The length for the buffer is the same for all virtual ports. See Table 3-1 for more information.         |

| CIQ ReadPtr      | The read pointer of the communication instruction queue. This value is managed by hardware. This pointer counts in VCI and not in bytes. See Table 3-4 for more information.                    |

| RDR ReadPtr      | The read pointer of the receive data region. The meaning of this value depends on which receive system is used. See Table 3-4 for more information.                                             |

| RDR WritePtr     | The write pointer of the receive data region. The meaning of this value depends on which receive system is used. See Table 3-4 for more information.                                            |

| SDR ReadPtr      | The read pointer of the send data region. This value is managed by hardware. See Table 3-4 for more information.                                                                                |

| SDR WritePtr     | The write pointer of the send data region. This value is managed by the user. See Table 3-4 for more information.                                                                               |

| NQ ReadPtr       | The read pointer of the notification queue. The value is managed by the user. See Table 3-4 for more information.                                                                               |

| NQ WritePtr      | The write pointer of the notification queue. This value is managed by hardware. See Table 3-4 for more information.                                                                             |

| PSW              | This is the configuration status word of the VP. See Table 3-4 for further information.                                                                                                         |

**Table 3-3:** Virtual Port Descriptor Members

For performance reasons the virtual port descriptor has a limited, fixed size of 64 Bytes. Because of the limited space it is necessary to avoid the storage of useless data. In general the pointers are incremented by the size of the corresponding queue descriptor (e.g. window de-

scriptor). Therefore the least significant bits of the pointers are always 0 and can be omitted in the virtual port descriptor. Table 3-4 gives an overview of the different pointers and their unit sizes.