#### Computer Architecture Lab at Carnegie Mellon

# Fast Scalable FPGA-Based Network-on-Chip Simulation Models

Michael K. Papamichael

papamix@cs.cmu.edu

Cambridge, UK, July 2011

### This Year's MEMOCODE Contest

### Objective

- Build the fastest simulator for a class of Networks-on-Chip

- Replicate cycle-by-cycle behavior of SW reference simulator

### Simulator takes two inputs

#### 1. Network configuration

- number and input/output configuration of routers

- network topology

- number of virtual channels

- credit delay cycles

#### 2. Routing info and traffic pattern

- routing information for each network router

- number and type of packets to send

Many parameters → very large design space!

# **Dual-Engine NoC Simulator**

#### FPGA-based solution

- Developed in Bluespec System Verilog

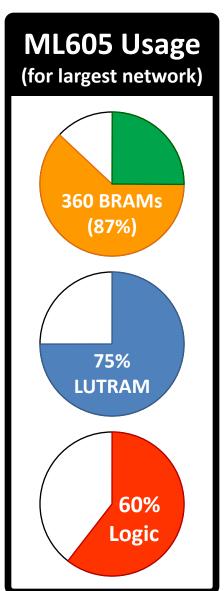

- Targets the Xilinx ML605 board

- Consists of two NoC simulation engines

### NoC simulation engines

- High-performance direct-mapped engine

- Supports up to moderately sized networks (~100 routers)

- Provides 500x-1000x speedup

- Highly scalable virtualized time-multiplexed engine

- Supports all possible networks in the design space

- Provides 5x-50x speedup

Dual-engine approach effectively covers entire design space

- Introduction

- FPGA-based NoC Simulator

- FPGA Simulation Platform

- Direct-Mapped NoC Simulation Engine

- Virtualized NoC Simulation Engine

- Results

- Discussion

- LINE + Demo

- Introduction

- FPGA-based NoC Simulator

- FPGA Simulation Platform

- Direct-Mapped NoC Simulation Engine

- Virtualized NoC Simulation Engine

- Results

- Discussion

- **[]** + Demo

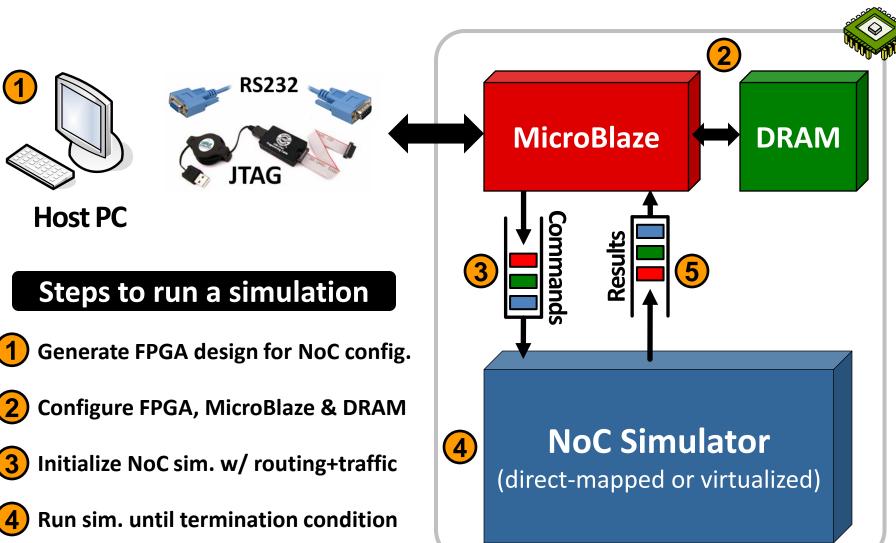

### **FPGA-based Simulation Platform**

**Extract simulation results**

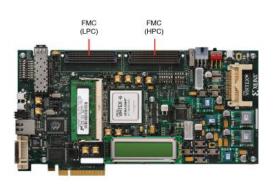

Xilinx ML605 Board

# **Direct-Mapped NoC Simulator**

- Why simulate... when you can prototype!

- Direct implementation of target NoC on the FPGA

- Instantiates all routers, links, traffic sources, etc

- Collection of routers connected according to NoC configuration

- Additional logic required to detect termination conditions

- High performance at the cost of limited scalability

- Achieves 500x-1000x speedup over software reference design

- ML605 can fit up to ~100 routers of moderate complexity

- 5-input/output, 4VC router occupies ~1% of LX240T FPGA

- Need a more scalable solution for remaining design space

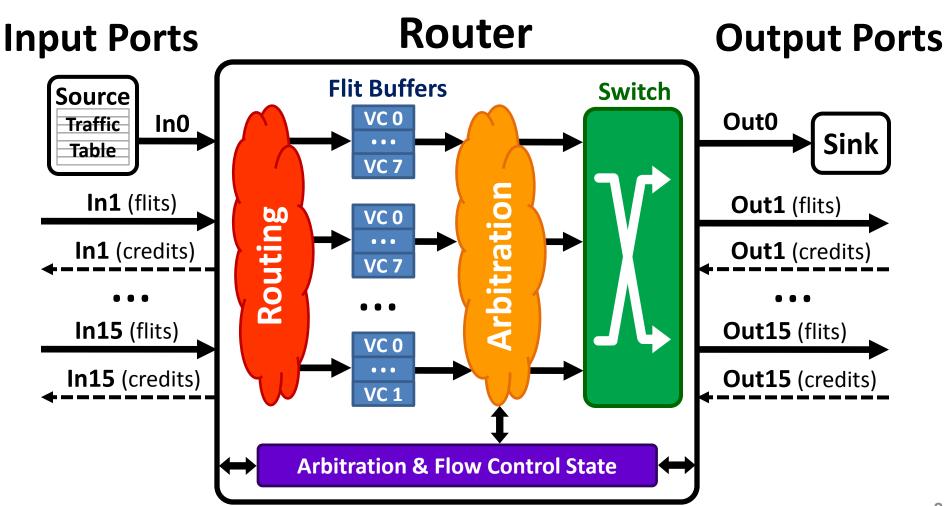

# **Direct-Mapped Router Architecture**

High-level block diagram of parameterized router

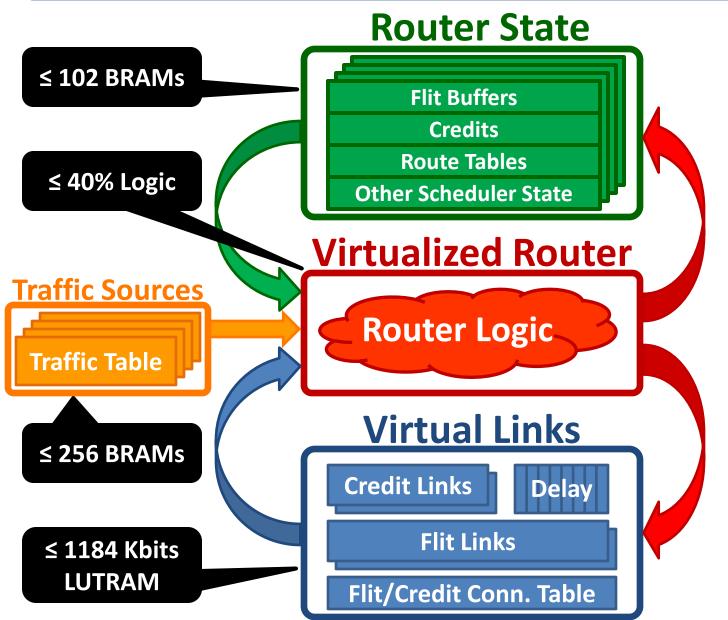

### **Virtualized NoC Simulator**

- If resources start getting scarce, virtualize!

- Time-multiplexed implementation

- Routers are simulated one at a time in successive clock cycles

- Router, traffic source and link state stored in on-chip memory

- Special care to retain proper ordering of events [Pellauer '11]

- Aggressive prefetching to maintain high simulation throughput

- Scales to very large networks with complex routers

- Can cover entire design space on ML605

- 256-router network occupies ~85% of LX240T

- Only used when direct-mapped approach will not fit

## **Virtualized NoC Simulator Details**

- Introduction

- FPGA-based NoC Simulator

- FPGA Simulation Platform

- Direct-Mapped NoC Simulation Engine

- Virtualized NoC Simulation Engine

- Results

- Discussion

- **[[]]** + Demo

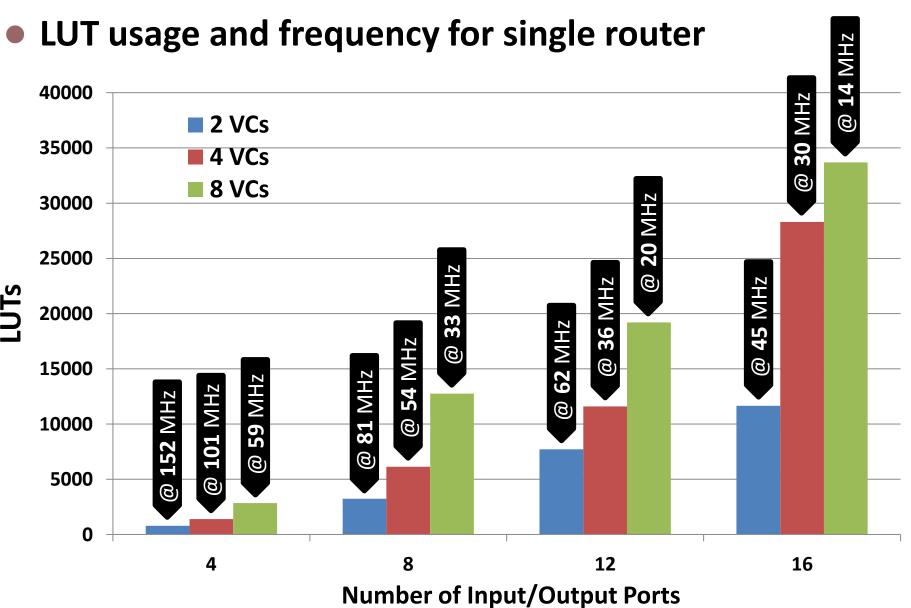

# **Direct-Mapped Implementation Results**

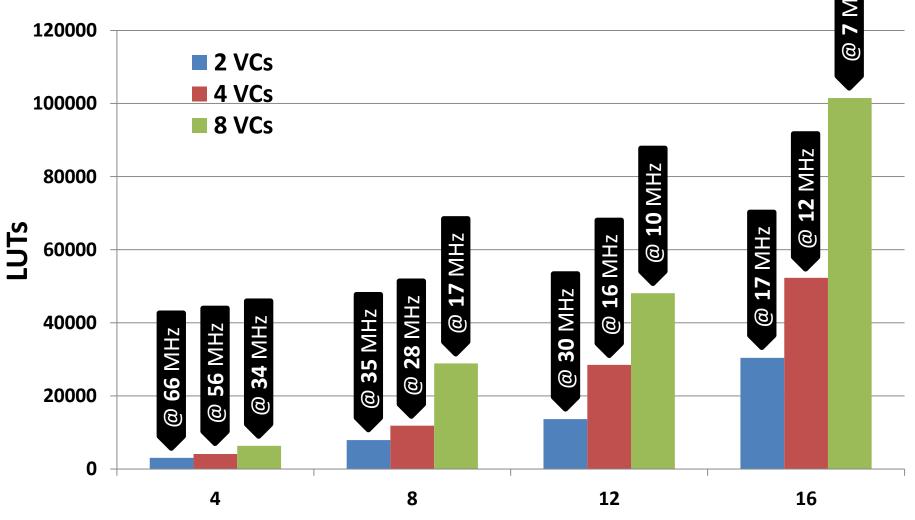

# Virtualized Implementation Results

LUT usage and frequency for 256-router network

### **Results for Contest Networks**

### Five network and router configurations

| <b>Network Name</b> | Routers | <b>Routers</b> Ports/router |   | Credit Delay |  |

|---------------------|---------|-----------------------------|---|--------------|--|

| butterfly           | 112     | 3                           | 8 | 1            |  |

| highradix           | 16      | 16                          | 8 | 15           |  |

| mesh                | 253     | 5                           | 4 | 3            |  |

| torus               | 252     | 7                           | 5 | 2            |  |

| hypercube           | 256     | 9                           | 1 | 1            |  |

All configurations lie at "edge" of design space, i.e. max-out at least one parameter

### Implementation results for contest networks

| Network   | Xilinx Virtex-6 LX240T |        |         | Xilinx Virtex-6 LX760T |        |         |

|-----------|------------------------|--------|---------|------------------------|--------|---------|

|           | Sim. Type              | % LUTs | Speedup | Sim. Type              | % LUTs | Speedup |

| butterfly | Direct Map             | 86%    | 1511x   | Direct Map             | 27%    | 2330x   |

| highradix | Virtualized            | 63%    | 6x      | Direct Map             | 93%    | 421x    |

| mesh      | Virtualized            | 3%     | 28x     | Direct Map             | 96%    | 4281x   |

| torus     | Virtualized            | 8%     | 786x    | Virtualized            | 2%     | 789x    |

| hypercube | Virtualized            | 8%     | 21x     | Virtualized            | 2%     | 33x     |

- Introduction

- FPGA-based NoC Simulator

- FPGA Simulation Platform

- Direct-Mapped NoC Simulation Engine

- Virtualized NoC Simulation Engine

- Results

- Discussion

- **[]** + Demo

# **Design Principles**

#### Correctness First

- First only focused on correctness and verify design

- Then optimize entire system and individual components

### Parameterization and Modularity

- Built parameterized versions of all submodules

- Utilize Bluespec's powerful parameterization mechanisms

### Harnessing the power of Bluespec

- Static elaboration for easy parameterization

- Define clean interfaces for modularity

- Rely on type checking for early bug detection

- Maintain high-level of abstraction to harness complexity

# Bluespec code sample for virtual design

// Write new router state

// Main simulation rule for virtualized design. Simulates network one router at a time. rule simulate\_vcycle (init\_done);

#### // Send outgoing flits/credits

routerState.write(cur router, router state after);

flitLinks.putFlits(cur\_router, out\_links.out\_flits, tickVirtualClock); // Send flits to other routers

virtualSources.putCredits(cur\_router, out\_links.out\_credits[0]); // Send credits to traffic sources

creditLinks.putCredits(cur\_router, out\_credits\_to\_routers, tickVirtualClock); // Send credits

#### // Advance to next router

cur\_router <= next\_router;

endrule</pre>

- Introduction

- FPGA-based NoC Simulator

- FPGA Simulation Platform

- Direct-Mapped NoC Simulation Engine

- Virtualized NoC Simulation Engine

- Results

- Discussion

- LINE + Demo

# Taking it to the next level - CONECT

- Direct-mapped approach implements an actual NoC

- Parameterized

- FPGA-friendly

- Supports arbitrary network topologies

Build on top of this to create a useful tool!

: Configurable Network Creation Tool

- Highly parameterized Network-on-Chip generation tool

- # routers, topology, routing, allocation, # VCs, buffer width/depth, etc

- **Back end developed in Bluespec System Verilog**

- Python command-line interface and web interface (demo)

# **CONECT Web Interface Demo**

# Thanks!

# **Questions?**