# Fast Flexible FPGA-Tuned Networks-on-Chip

Michael K. Papamichael <papamix@cs.cmu.edu>, James C. Hoe <jhoe@ece.cmu.edu>

#### **Networks-on-Chip (NoCs) and FPGAs**

#### Rapid growth of FPGA capacity & features

- Extended SoC and full-system prototyping

- FPGA-based high-performance computing

- → Need for flexible NoCs to support communication

### Map existing ASIC-oriented NoC designs on FPGAs?

- Inefficient use of FPGA resources

- ASIC-driven NoC arch. not optimal for FPGA

# **EUNNEL** FPGA-tuned NoC Architecture

- Embodies FPGA-motivated design principles

- Very lightweight, minimizes resource usage

- Publicly released flexible NoC generator

## The CONNECT NoC Architecture

#### **FPGAs peculiar HW realization substrate**

- Relative cost of speed vs. logic vs. wires vs. mem.

- Unique mapping and operating characteristics focuses on 4 FPGA characteristics:

- **Abundance of Wires**

- **Storage Shortage & Peculiarities**

- **Frequency Challenged**

- Reconfigurable Nature

FPGA characteristics uniquely influence NoC design decisions, which often go against ASIC-driven NoC conventional wisdom.

#### **CONNECT vs. ASIC-Oriented RTL**

## 16-node 4x4 Mesh Network-on-Chip (NoC)

- SOTA: state-of-the-art high-quality ASIC-oriented RTL\*

- CONNECT: identical config. LUNNELT -generated RTL

#### **Network Performance FPGA Resource Usage** (same NoC configuration) (uniform random traffic @ 100MHz) 60K (in same configuration ightarrow900-100half the resources & similar performance **S** 40Ksame LUT budget → 4x higher bandwidth 2x lower latency 20K-Avg.

\*NoC RTL from http://nocs.stanford.edu/cgi-bin/trac.cgi/wiki/Resources/Router

**Load** (in Gbps)

# The CONNECT Approach: Tailoring NoCs to FPGAs

#### **Abundance of Wires**

#### Densely connected wiring substrate

- (Over)provisioned to handle worst case

- Wires are "free" comp. to other resources

### **LUNNELLI** NoC Implications

- → Datapaths & channels as wide as possible

- → Adjust packet format

- E.g. carry control info on the dedicated side links

- → Adapt traditional credit-based flow control "Peek" flow control in CONNECT uses wider links

## **Storage Shortage & Peculiarities**

- Modern FPGAs offer storage in two forms

- Block RAMs and LUT RAMs (use logic resources)

- Only come in specific aspect ratios and sizes

- In high demand, especially Block RAMs

# **LUNNEL** NoC Implications

- → Optimize for aspect ratios and sizes Multiple logical flit buffers in each physical buffer

- → Use LUT RAM for flit buffers

- Leave Block RAM resources for rest of design

## Frequency "Challenged"

10K-

4x4 Mesh NoC

- Much lower frequencies compared to ASICs

- LUTs inherently slower than ASIC standard cells

- Large wire delays when chaining LUTs

- Rapidly diminishing returns of pipelining

#### **LUNNELT** NoC Implications

- → Design router as single-stage pipeline Also dramatically reduces network latency

- → Adjust network to meet perf. goals E.g. increase link width or adapt topology

# **Reconfigurable Nature**

- **Reconfigurable nature of FPGAs**

- Sets them apart from ASICs Allows support for diverse range of applications

#### **ELINNELLI** NoC Implications

- → Support application-specific customization Flexible parameterized NoC architecture Automated NoC design generator (demo!)

- → Adhere to standard common interface NoC appears as plug-and-play black box

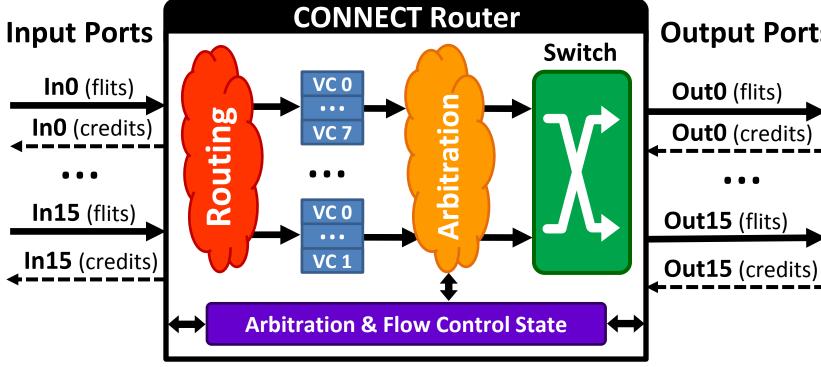

#### **CONNECT Architecture CONNECT Router Output Ports Switch**

- Topology-Agnostic Architecture • Fully parameterized, including:

- # in/out ports, # virtual channels

- flit width, buffer depths

- Flexible user-specified routing

- Four allocation algorithms

- Two flow-control mechanisms

- "Virtual Link" Support

- Contiguous delivery of multi-flit packets

- FPGA-friendly "Peek" Flow Control

- Lightweight alternative to credit-based

# **CONNECT Network Examples and Results**

- Four sample CONNECT Networks ( router, endpoint)

- 16 endpoints, 2/4 virtual channels, 128-bit datapath

**High Radix**

All above networks are interchangeable from user perspective.

## **FPGA Synthesis Results**

| Network    | Network Configuration |       |              | Xilinx Virtex-6 LX760T |                       |

|------------|-----------------------|-------|--------------|------------------------|-----------------------|

|            | # Routers             | # VCs | Ports/Router | % LUTs                 | <b>Freq.</b> (in MHz) |

| Ring       | 16                    | 4     | 3            | 3%                     | 158                   |

| Fat Tree   | 20                    | 4     | 4            | 4%                     | 143                   |

| Mesh       | 16                    | 4     | 5            | 5%                     | 113                   |

| High Radix | 8                     | 2     | 9            | 9%                     | 75                    |

< 10% LUT Utilization for all networks, No Block RAMs

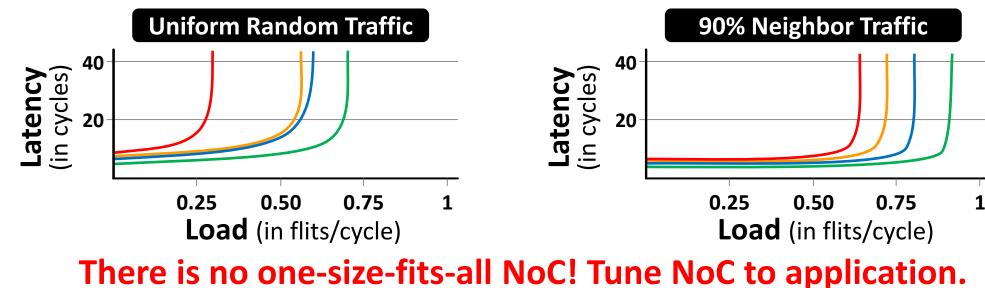

#### **Network Performance Results**

Please see our FPGA 2012 paper for more synthesis and performance results.

## **Conclusions & Public Release**

- Significant gains from tuning for FPGA

- FPGAs and ASICs have different design "sweet spot"

- Compared to ASIC-driven NoCs, CONNECT offers

- Significantly lower network latency and

- ~50% lower LUT usage or 3-4x higher network performance

- Take advantage of reconfigurable nature of FPGA

- Tailor NoC to specific communication needs of application

## **CONNECT NoC Generator Public Release**

### http://www.ece.cmu.edu/~mpapamic/connect

**Industry**

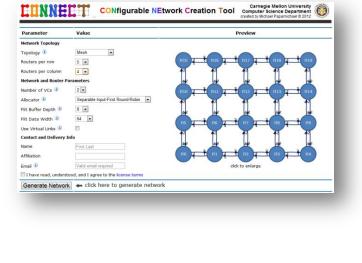

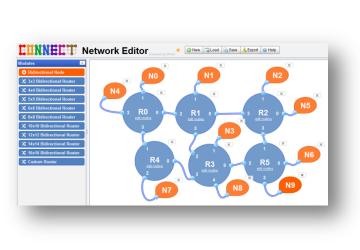

#### NoC Generator with web-based interface

- Supports multiple pre-configured topologies

- Includes graphical custom topology editor

- Some Release Stats (since release in March 2012)

- 2000+ unique visitors • **200+** network generation requests

- **Most Popular Topologies** User Breakdown Mesh/Torus – 51% **Double Ring – 14%** 35% 40% Ring/Line – 14% Other lAcademia Fully Connected – 10% 25% Custom – 6%

**Star – 5%**