# Verification Tools for Finite-State Concurrent Systems \*

E. Clarke<sup>1</sup>, O. Grumberg<sup>2</sup>, and D. Long<sup>3</sup>

Carnegie Mellon, Pittsburgh

The Technion, Haifa

AT&T Bell Labs, Murray Hill

ABSTRACT: Temporal logic model checking is an automatic technique for verifying finite-state concurrent systems. Specifications are expressed in a propositional temporal logic, and the concurrent system is modeled as a state-transition graph. An efficient search procedure is used to determine whether or not the state-transition graph satisfies the specification. When the technique was first developed ten years ago, it was only possible to handle concurrent systems with a few thousand states. In the last few years, however, the size of the concurrent systems that can be handled has increased dramatically. By representing transition relations and sets of states implicitly using binary decision diagrams, it is now possible to check concurrent systems with more than  $10^{120}$  states. In this paper we describe in detail how the new implementation works and give realistic examples to illustrate its power. We also discuss a number of directions for future research. The necessary background information on binary decision diagrams, temporal logic, and model checking has been included in order to make the exposition as self-contained as possible.

Keywords: automatic verification, temporal logic, model checking, binary decision diagrams

### Table of Contents

#### 1 Introduction

- 1.1 Temporal Logic model checking

- 1.2 New implementations

- 1.3 Related verification techniques

- 1.4 Outline of paper

### 2 Binary Decision Diagrams

<sup>\*</sup> This research was sponsored in part by the Avionics Laboratory, Wright Research and Development Center, Aeronautical Systems Division (AFSC), U.S. Air Force, Wright-Patterson AFB, Ohio 45433-6543 under Contract F33615-90-C-1465, ARPA Order No. 7597 and in part by the National Science foundation under Grant No. CCR-9217549 and in part by the Semiconductor Research Corporation under Contract 92-DJ-294. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied of the U.S. government.

- 3 Representing relations with OBDDs

- 4 Computation Tree Logics

- 5 Fixpoint characterization

- 6 Symbolic Model Checking

- 7 Fairness Constraints

- 8 Counterexamples and witnesses

- 9 LTL Model Checking

- 10 Checking language containment

- 11 The SMV Model Checker

- 12 A non-trivial example

- 13 Directions for Future Research

- 13.1 Develop compositional reasoning techniques

- 13.2 Investigate the use of abstraction for reasoning about data paths

- 13.3 Find ways of exploiting symmetry in circuits and protocols

- 13.4 Develop techniques for verifying parameterized systems

- 13.5 Use partial orders to avoid the state explosion problem

- 13.6 Investigate techniques for verifying systems with real-time constraints

- 13.7 Develop tool interfaces suitable for circuit and protocol designers

#### 1 Introduction

Finite-state concurrent systems arise naturally in several areas of computer science, particularly in the design of digital circuits and communication protocols. Logical errors found late in the design phase of these systems are an extremely important problem for both circuit designers and programmers. Such errors can delay getting a new product on the market or cause the failure of some critical device that is already in use. The most widely used verification technique is based on extensive simulation and can easily miss significant errors when the number possible states of the circuit or protocol is very large. Although there has been considerable research on the use of theorem provers, term rewriting systems and proof checkers for verification, these techniques are time consuming and often require a great deal of manual intervention. During the past ten years, researchers at Carnegie Mellon University have developed an alternative approach to verification called temporal logic model checking [26, 27]. In this approach specifications are expressed in a propositional temporal logic, and circuit designs and protocols are modeled as state-transition systems. An efficient search procedure is used to determine automatically if the specifications are satisfied by the transition systems.

Model checking has several important advantages over mechanical theorem provers or proof checkers for verification of circuits and protocols. The most important is that the procedure is completely automatic. Typically, the user provides a high level representation of the model and the specification to be checked. The model checking algorithm will either

terminate with the answer true, indicating that the model satisfies the specification, or give a counterexample execution that shows why the formula is not satisfied. The counterexamples are particularly important in finding subtle errors in complex transition systems. The procedure is also quite fast, and usually produces an answer in a matter of minutes. Partial specifications can be checked, so it is unnecessary to completely specify the circuit before useful information can be obtained regarding its correctness. When a specification is not satisfied, other formulas—not part of the original specification—can be checked in order to locate the source of the error. Finally, the logic used for specifications can directly express many of the properties that are needed for reasoning about concurrent systems.

The main disadvantage of this technique is the state explosion which can occur if the system being verified has many components that can make transitions in parallel. Because of this problem, many researchers in formal verification predicted that model checking would never be practical for large circuits and protocols. Recently, however, the size of the transition systems that can be verified by model checking techniques has increased dramatically. The initial breakthrough was made in the fall of 1987 by McMillan, who was then a graduate student at Carnegie Mellon. He realized that using an explicit representation for transition relations severely limited the size of the circuits and protocols that could verified. He argued that larger systems could be handled if transition relations were represented implicitly with ordered binary decision diagrams (OBDDs) [14]. By using the original model checking algorithm with the new representation for transition relations, he was able to verify some examples that had more than 10<sup>20</sup> states [22, 61]. He made this observation independently of the work by Coudert, et. al. [33] and Pixley [65, 66, 67] on using OBDDs to check equivalence of deterministic finite-state machines. Since then, various refinements of the OBDD-based techniques by other researchers at Carnegie Mellon have pushed the state count up to more than 10<sup>120</sup> [19].

### 1.1 Temporal Logic model checking

Temporal logics have proved to be useful for specifying concurrent systems, because they can describe the ordering of events in time without introducing time explicitly. They were originally developed by philosophers for investigating the way that time is used in natural language arguments [49]. Although a number of different temporal logics have been studied, most have an operator like G f that is true in the present if f is always true in the future (i.e., if f is globally true). To assert that two events  $e_1$  and  $e_2$  never occur at the same time, one would write  $G(\neg e_1 \lor \neg e_2)$ . Temporal logics are often classified according to whether time is assumed to have a linear or a branching structure. This classification may occasionally be misleading since some temporal logics combine both linear-time and branching-time operators. Instead, we will adopt the approach used in [41] that permits both types of logics to be treated within a single semantical framework. In this paper the meaning of a temporal logic formula will always be determined with respect to a labelled state-transition graph; for historical reasons such structures are called Kripke models [49].

Pnueli [68] was the first to use temporal logic for reasoning about the concurrent programs. His approach involved proving properties of the program under consideration from a set of axioms that described the behavior of the individual statements in the program. The method was extended to sequential circuits by Bochmann [7] and Owicki and Malachi [58]. Since proofs were constructed by hand, the technique was often difficult to use in practice. The introduction of temporal logic model checking algorithms in the early 1980's allowed this type of reasoning to be automated. Since checking that a single model satisfies a formula is much easier than proving the validity of a formula for all models, it was possible to implement this technique very efficiently. The first algorithm was developed by Clarke and Emerson in [26]. Their algorithm was polynomial in both the size of the model determined by the program under consideration and in the length of its specification in temporal logic. They also showed how fairness could be handled without changing the complexity of the algorithm. This was an important step since the correctness of many concurrent programs depends on some type of fairness assumption; for example, absence of starvation in a mutual exclusion algorithm may depend on the assumption that each process makes progress infinitely often.

At roughly the same time Quielle and Sifakis [70] gave a model checking algorithm for a similar branching-time logic, but they did not analyze its complexity or show how to handle an interesting notion of fairness. Later Clarke, Emerson, and Sistla [27] devised an improved algorithm that was linear in the product of the length of the formula and in the size of the global state graph. Clarke and Sistla [74] also analyzed the model checking problem for a variety of other temporal logics and showed, in particular, that for linear temporal logic the problem was PSPACE complete.

A number of papers demonstrated how the temporal logic model checking procedure could be used for verifying network protocols and sequential circuits ([10], [11], [12], [13], [27], [38], [63]). In the case of sequential circuits two approaches were used for obtaining state-transition graphs to analyze. The first approach extracted a state graph directly from the circuit under an appropriate timing model of circuit behavior. The second approach obtained a state-transition graph by compilation from a high level representation of the circuit in a Pascal-like programming language. Early model checking systems were able to check state-transition graphs with between 10<sup>4</sup> and 10<sup>5</sup> states at a rate of about 100 states per second for formulas. In spite of these limitations, model checking systems were used successfully to find previously unknown errors in several published circuit designs.

Alternative techniques for verifying concurrent systems were proposed by a number of other researchers. The approach developed by Kurshan [48, 52] was based on checking inclusion between two automata. The first machine represented the system that was being verified; the second represented its specification. Automata on infinite tapes (ω-automata) were used in order to handle fairness. Pnueli and Lichtenstein [56] reanalyzed the complexity of checking linear-time formulas and discovered that although the complexity appears exponential in the length of the formula, it is linear in the size of the global state graph. Based on this observation, they argued that the high complexity of linear-time model checking might still be acceptable for short formulas. Emerson and Lei [43] extended their result to show that formulas of the logic CTL\*, which combines both branching-time and linear-time operators, could be checked with essentially the same complexity as formulas of linear temporal logic. Vardi and Wolper [79] showed how the model checking problem could be formulated in terms of automata, thus relating the model checking approach to the work of Kurshan.

#### 1.2 New implementations

In the original implementation of the model checking algorithm, transition relations were represented explicitly by adjacency lists. For concurrent systems with small numbers of processes, the number of states was usually fairly small, and the approach was often quite practical. Recent implementations [22, 61] use the same basic algorithm; however, transition relations are represented implicitly by ordered binary decision diagrams (OBDDs) [14]. OBDDs provide a canonical form for boolean formulas that is often substantially more compact than conjunctive or disjunctive normal form, and very efficient algorithms have been developed for manipulating them. Because this representation captures some of the regularity in the state space determined by circuits and protocols, it is possible to verify systems with an extremely large number of states—many orders of magnitude larger than could be handled by the original algorithm.

The implicit representation is quite natural for modeling sequential circuits and protocols. Each state is encoded by an assignment of boolean values to the set of state variables associated with the circuit or protocol. The transition relation can, therefore, be expressed as a boolean formula in terms of two sets of variables, one set encoding the old state and the other encoding the new. This formula is then represented by a binary decision diagram. The model checking algorithm is based on computing fixed points of predicate transformers that are obtained from the transition relation. The fixed points are sets of states that represent various temporal properties of the concurrent system. In the new implementations, both the predicate transformers and the fixed points are represented with OBDDs. Thus, it is possible to avoid explicitly constructing the state graph of the concurrent system.

The model checking system that McMillan developed as part of his Ph.D. thesis is called SMV [61]. It is based on a language for describing hierarchical finite-state concurrent systems. Programs in the language can be annotated by specifications expressed in temporal logic. The model checker extracts a transition system from a program in the SMV language and uses a OBDD-based search algorithm to determine whether the system satisfies its specifications. If the transition system does not satisfy some specification, the verifier will produce an execution trace that shows why the specification is false. The SMV system has been distributed widely, and a large number of examples have now been verified with it. These examples provide convincing evidence that SMV can be used to debug real industrial designs.

Perhaps, the most impressive example that has been verified by model checking techniques is the cache coherence protocol described in the IEEE Futurebus+ standard (IEEE Standard 896.1-1991). Although development of the Futurebus+ cache coherence protocol began in 1988, all previous attempts to validate the protocol were based entirely on informal techniques. In the summer of 1992 researchers at Carnegie Mellon [29] constructed a precise model of the protocol in SMV language and then used SMV to show that the resulting transition system satisfied a formal specification of cache coherence. They were able to find a number of previously undetected errors and potential errors in the design of the protocol. This appears to be the first time that an automatic verification tool has been used to find errors in an IEEE standard.

#### 1.3 Related verification techniques

A number of other researchers have independently discovered that OBDDs can be used to represent large state-transition systems. Coudert, Berthet, and Madre [33] have developed an algorithm for showing equivalence between two deterministic finite-state automata by performing a breadth first search of the state space of the product automata. They use OBDDs to represent the transition functions of the two automata in their algorithm. Similar algorithms have been developed by Pixley [65, 66, 67]. In addition, several groups including Bose and Fisher [8], Pixley [65], and Coudert, et. al. [34] have experimented with model checking algorithms that use OBDDs. Although the results of McMillan's experiments [21, 22] were not published until the summer of 1990, his work is referenced by Bose and Fisher in their 1989 paper [8].

Recently, Bryant, Seger and Beatty [4, 17] have developed an algorithm based on symbolic simulation for model checking in a restricted linear time logic. Specifications consist of precondition-postcondition pairs expressed in the logic. The precondition is used to restrict inputs and initial states of the circuit; the postcondition gives the property that the user wishes to check. Formulas in the logic have the form

$$p_0 \wedge \mathbf{X} p_1 \wedge \mathbf{X}^2 p_2 \wedge \cdots \wedge \mathbf{X}^{n-1} p_{n-1} \wedge \mathbf{X}^n p_n$$

.

The syntax of the formulas is highly restricted compared to most other temporal logics used for specifying programs and circuits. In particular, the only logical operator that is allowed is conjunction, and the only temporal operator is  $next\ time\ (X)$ . By limiting the class of formulas that can be handled, it is possible to check certain properties very efficiently. In many cases, however, these restrictions can be a disadvantage, since the number of time units that a formula can "look ahead in the future" is bounded by the maximum nesting of X operators.

It is difficult to compare the performance of the various symbolic verification methods. Probably, the best method is to study how the CPU time required for verification grows asymptotically with larger and larger instances of the circuit or protocol. In most of the example circuits considered in [19, 20], this growth rate is a small polynomial in the number of components of the circuit. Of the other groups mentioned above, only Bryant, Beatty and Seger [4] have demonstrated good asymptotic performance on a nontrivial class of circuits. Berthet, Coudert and Madre [6] obtained verification times that were sublinear in the number of states in the system, but these times were still exponential in the number of components.

#### 1.4 Outline of paper

Our paper is organized as follows: The properties of OBDDs that are needed to understand the paper are given in Section 2. The next section shows how relations over a finite domain can be encoded using OBDDs. Section 4 describes the logics that are used in this paper, and Section 5 discusses some of the properties of predicate transformers that are needed in model checking. The basic model checking algorithm for branching-time temporal logic is given in Section 6. The next two sections describe extensions of the basic algorithm. Section 7 shows how fairness constraints can be handled, and Section 8

describes how counterexamples and witnessnesses are generated. A model checking algorithm for linear-time temporal logic is presented in Section 9, and the following section shows how model checking techniques can be used to test inclusion between  $\omega$ -automata. Section 11 gives a brief overview of the SMV model checking system, and Section 12 shows how SMV was used to find errors in the IEEE Futurebus standard. The paper concludes in Section 13 with some directions for future research.

### 2 Binary Decision Diagrams

Ordered binary decision diagrams (OBDDs) are a canonical form representation for boolean formulas [14]. They are often substantially more compact than traditional normal forms such as conjunctive normal form and disjunctive normal form, and they can be manipulated very efficiently. Hence, they have become widely used for a variety of CAD applications, including symbolic simulation, verification of combinational logic and, more recently, verification of sequential circuit designs.

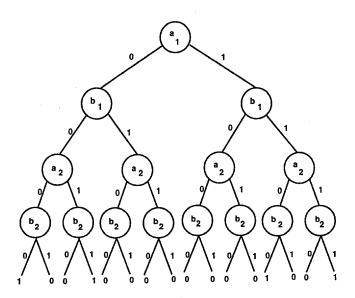

To motivate our discussion of binary decision diagrams we first consider binary decision trees. A binary decision tree is a rooted, directed tree that consists of two types of vertices, terminal vertices and nonterminal vertices. Each nonterminal vertex v is labeled by a variable v and has two successors: low(v) corresponding to the case where the variable v is assigned 0, and high(v) corresponding to the case where v is assigned 1. Each terminal vertex v is labeled by value(v) which is either 0 or 1. A binary decision tree for the two-bit comparator, given by the formula  $f(a_1, a_2, b_1, b_2) = (a_1 \leftrightarrow b_1) \land (a_2 \leftrightarrow b_2)$ , is shown in Figure 1. One can decide whether a particular truth assignment to the variables

Fig. 1. Binary decision tree for two-bit comparator

makes the formula true or not by traversing the tree from the root to a terminal vertex. If the variable v is assigned 0, then the next vertex on the path from the root to the terminal vertex will be low(v). If v is assigned 1 then the next vertex on the path will be high(v). The value that labels the terminal vertex will be the value of the function for this assignment. For example, the assignment  $\langle a_1 \leftarrow 1, a_2 \leftarrow 0, b_1 \leftarrow 1, b_2 \leftarrow 1 \rangle$  leads to a leaf vertex labeled 0; hence, the formula is false for this assignment.

Binary decision trees do not provide a very concise representation for boolean functions. In fact, they are essentially the same size as truth tables. Fortunately, there is usually a lot of redundancy in such trees. For example, in the tree of Figure 1 there are eight subtrees with roots labeled by  $b_2$ , but only three are distinct. Thus, we can obtain a more concise representation for the boolean function by merging isomorphic subtrees. This results in a directed acyclic graph (DAG) called a binary decision diagram. More precisely, a binary decision diagram is a rooted, directed acyclic graph with two types of vertices, terminal vertices and nonterminal vertices. As in the case of binary decision trees, each nonterminal vertex v is labeled by a variable var(v) and has two successors, low(v) and high(v). Each terminal vertex is labeled by either 0 or 1. Every binary decision diagram B with root v determines a boolean function  $f_v(x_1, \ldots, x_n)$  in the following manner:

- 1. If v is a terminal vertex:

- (a) If value(v) = 1 then  $f_v(x_1, \ldots, x_n) = 1$ .

- (b) If value(v) = 0 then  $f_v(x_1, \ldots, x_n) = 0$ .

- 2. If v is a nonterminal vertex with  $var(v) = x_i$  then  $f_v$  is the function

$$f_v(x_1,\ldots,x_n) = \bar{x}_i \cdot f_{low(v)}(x_1,\ldots,x_n) + x_i \cdot f_{high(v)}(x_1,\ldots,x_n)$$

In practical applications it is desirable to have a canonical representation for boolean functions. Such a representation must have the property that two boolean functions are logically equivalent if and only if they have isomorphic representations. This property simplifies tasks like checking equivalence of two formulas and deciding if a given formula is satisfiable or not. Two binary decision diagrams are isomorphic if there exists a one-to-one and onto function h that maps terminals of one to terminals of the other and nonterminals of one to nonterminals of the other, such that for every terminal vertex v, value(v) = value(h(v)) and for every nonterminal vertex v, var(v) = var(h(v)), h(low(v)) = low(h(v)), and h(high(v)) = high(h(v)).

Bryant [14] showed how to obtain a canonical representation for boolean functions by placing two restrictions on binary decision diagrams. First, the variables should appear in the same order along each path from the root to a terminal. Second, there should be no isomorphic subtrees or redundant vertices in the diagram. The first requirement is achieved by imposing a total ordering < on the variables that label the vertices in the binary decision diagram and requiring that for any vertex u in the diagram, if u has a nonterminal successor v, then var(u) < var(v). The second requirement is achieved by repeatedly applying three transformation rules that do not alter the function represented by the diagram:

Remove duplicate terminals: Eliminate all but one terminal vertex with a given label and redirect all arcs to the eliminated vertices to the remaining one.

Remove duplicate nonterminals: If nonterminals u and v have var(u) = var(v), low(u) = low(v) and high(u) = high(v), then eliminate one of the two vertices and redirect all incoming arcs to the other vertex.

Remove redundant tests: If nonterminal vertex v has low(v) = high(v), then eliminate v and redirect all incoming arcs to low(v).

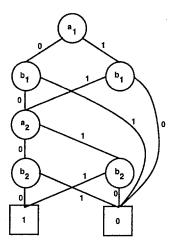

Starting with a binary decision diagram satisfying the ordering property, the canonical form is obtained by applying the transformation rules until the size of the diagram can no longer be reduced. Bryant shows how this can be done in a bottom-up manner by a procedure called *Reduce* in time which is linear in the size of the original binary decision diagram [14]. The term ordered binary decision diagram (OBDD) will be used to refer to the graph obtained in this manner. For example, if we use the ordering  $a_1 < b_1 < a_2 < b_2$  for the two-bit comparator function, we obtain the OBDD shown in Figure 2. If OBDDs

Fig. 2. OBDD for two-bit comparator

are used as a canonical form for boolean functions, then checking equivalence is reduced to checking isomorphism between binary decision diagrams. Similarly, satisfiability can be determined by checking equivalence to the trivial OBDD that consists of only one terminal labeled by 0.

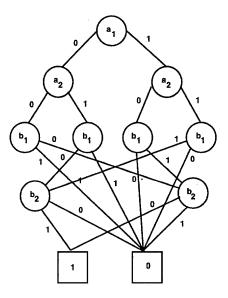

The size of an OBDD can depend critically on the variable ordering. For example, if we use the variable ordering  $a_1 < a_2 < b_1 < b_2$  for the bit-comparator function, we get the OBDD shown in Figure 3. Note that this OBDD has 11 vertices while the OBDD shown in Figure 2 has only 8 vertices. In general, for n-bit comparator, if we choose the ordering  $a_1 < b_1 < \ldots < a_n < b_n$ , then the number of OBDD vertices will be 3n + 2. On the other hand, if we choose the ordering  $a_1 < \ldots < a_n < b_1 \ldots < b_n$ , then the number of OBDD vertices is  $3 \cdot 2^n - 1$ . Finding an optimal ordering can be shown to be NP-complete in general. Moreover, there are boolean functions that have exponential size OBDDs for

any variable ordering. One example is the boolean function for the middle output (or n-th output) of a combinational circuit to multiply two n bit integers [16, 15].

Fig. 3. OBDD for two-bit comparator

Several heuristics have been developed for finding a good variable ordering when such an ordering exists. If the boolean function is given by a combinational circuit, then heuristics based on a depth-first traversal of the circuit diagram generally give good results [44, 59]. The intuition for these heuristics comes from the observation that OBDDs tend to be small when related variables are close together in the ordering. The variables appearing in a subcircuit are related in that they determine the subcircuit's output. Hence, these variables should usually be grouped together in the ordering. This may be accomplished by placing the variables in the order in which they are encountered during a depth-first traversal of the circuit diagram. A technique, called *dynamic reordering* [71], appears to be useful in those situations where no obvious ordering heuristics apply. When this technique is used, the OBDD package internally reorders the variables periodically in order to reduce the total number of vertices in use. The reordering method is designed to be fast rather than to find an optimal ordering.

We next explain how to implement various important logical operations using OBDDs. We begin with the function that restricts some argument  $x_i$  of the boolean function f to a constant value b. This function is denoted by  $f|_{x_i \leftarrow b}$  and satisfies the identity

$$f|_{x_i \leftarrow b}(x_1, \ldots, x_n) = f(x_1, \ldots, x_{i-1}, b, x_{i+1}, \ldots, x_n).$$

If f is represented as an OBDD, then the OBDD for the restriction  $f|_{x_i \leftarrow b}$  can be easily computed by a depth-first traversal of the OBDD. For any vertex v which has a pointer

to a vertex w such that  $var(w) = x_i$ , we replace the pointer by low(w) if b is 0 and by high(w) if b is 1. The resulting graph may not be in canonical form, so we apply the Reduce function to it in order to obtain the OBDD representation for  $f|_{x_i \leftarrow b}$ .

All 16 two-argument logical operations can be implemented efficiently on boolean functions that are represented as OBDDs. In fact, the complexity of these operations is linear in the size of the argument OBDDs. The key idea for efficient implementation of these operations is the *Shannon expansion*

$$f = \bar{x} \cdot f \mid_{x \leftarrow 0} + x \cdot f \mid_{x \leftarrow 1}.$$

Bryant [14] gives a uniform algorithm called Apply for computing all 16 logical operations. Below we briefly explain how Apply works. Let  $\star$  be an arbitrary two argument logical operation, and let f and f' be two boolean functions. To simplify the explanation of the algorithm we introduce the following notation:

- -v and v' are the roots of the OBDDs for f and f', and

- -x = var(v) and x' = var(v'),

We consider several cases depending on the relationship between v and v'.

- If v and v' are both terminal vertices, then  $f \star f' = value(v) \star value(v')$ .

- If x = x', then we use the Shannon expansion

$$f \star f' = \bar{x} \cdot (f \mid_{x \leftarrow 0} \star f' \mid_{x \leftarrow 0}) + x \cdot (f \mid_{x \leftarrow 1} \star f' \mid_{x \leftarrow 1})$$

to break the problem into two subproblems. The subproblems are solved recursively. The root of the resulting OBDD will be v with var(v) = x. Low(v) will be the OBDD for  $(f|_{x \leftarrow 0} \star f'|_{x \leftarrow 0})$  and high(v) will be the OBDD for  $(f|_{x \leftarrow 1} \star f'|_{x \leftarrow 1})$ .

- If x < x', then  $f'|_{x \leftarrow 0} = f'|_{x \leftarrow 1} = f'$  since f' does not depend on x. In this case the Shannon Expansion simplifies to

$$f \star f' = \bar{x} \cdot (f \mid_{x \leftarrow 0} \star f') + x \cdot (f \mid_{x \leftarrow 1} \star f')$$

and the OBDD for  $f \star f'$  is computed recursively as in the second case.

- If x' < x, then the required computation is similar to the previous case.

Since each subproblem can generate two subproblems, care must be used in order to prevent the algorithm from being exponential. By using dynamic programming, it is possible to keep the algorithm polynomial. Each subproblem corresponds to a pair of OBDDs which are subgraphs of the original OBDDs for f and f'. Since each subgraph is uniquely determined by its root, the number of subgraphs in the OBDD for f is bounded by the size of the OBDD for f. The same bound holds for f'. Thus, the number of subproblems is bounded by the product of the size of the OBDDs for f and f'. A hash table is used to record all previously computed subproblems. Before any recursive call, the table is checked to see if the subproblem has been solved. If it has, the result is obtained from the table; otherwise, the recursive call is performed. The result must be reduced to ensure that it is in canonical form.

Several extensions have been developed to decrease the space requirements of Bryant's original OBDD representation for boolean functions [9]. A single multi-rooted graph

can be used to represent a collection of boolean functions that share subgraphs. The same variable ordering is used for all of the formulas in the collection. As in the case of standard OBDDs, the graph contains no isomorphic subgraphs or redundant vertices. If this extension is used then two functions in the collection are identical if and only if they have the same root. Consequently, checking whether two functions are equal can be implemented in constant time. Another useful extension is adding labels to the arcs in the graph to denote boolean negation. This makes it unnecessary to use different subgraphs to represent a formula and its negation. Modern OBDD packages permit graphs with hundreds of thousands of vertices to be manipulated efficiently.

OBDDs can also be viewed as a form of deterministic finite automata [31]. An n-argument boolean function can be identified with the set of strings in  $\{0,1\}^n$  that evaluate to 1. Since this is a finite language and all finite languages are regular, there is a minimal finite automaton that accepts this set. This automaton provides a canonical representation for the original boolean function. Logical operations on boolean functions can be implemented by set operations on the languages accepted by the finite automata. For example, AND corresponds to set intersection. Standard constructions from elementary automata theory can be used to compute these operations on languages. The standard OBDD operations can be viewed as analogs of these constructions.

### 3 Representing relations with OBDDs

OBDDs are extremely useful for obtaining concise representations of relations over finite domains [22, 61]. If R is n-ary relation over  $\{0,1\}$  then R can be represented by the OBDD for its characteristic function

$$f_R(x_1,\ldots,x_n)=1 \text{ iff } R(x_1,\ldots,x_n).$$

Otherwise, let R be an n-ary relation over the finite domain D. Without loss of generality we assume that D has  $2^m$  elements for some m > 1. In order to represent R as an OBDD, we encode elements of D, using a bijection  $\phi : \{0,1\}^m \to D$  that maps each boolean vector of length m to an element of D. Using the encoding  $\phi$ , we construct a boolean relation R' of arity  $m \times n$  according to the following rule:

$$R'(\bar{x}_1,\ldots,\bar{x}_n)=R(\phi(\bar{x}_1),\ldots,\phi(\bar{x}_n))$$

where  $\bar{x}_i$  is a vector of m boolean variables which encodes the variable  $x_i$  that takes values in D. R can now be represented as the OBBD determined by the characteristic function  $f_{R'}$  of R'. This technique can be easily extended to relations over different domains,  $D_1, \ldots, D_n$ . Moreover, since sets can be viewed as unary relations, the same technique can be used to represent sets as OBDDs.

In order to construct complex relations it is convenient to extend propositional logic to permit quantification over boolean variables. The resulting logic is called QBF (Quantified Boolean Formulas) [1, 45] and has the following syntax. Given a set  $V = \{v_1, \ldots, v_n\}$  of propositional variables, QBF(V) is the smallest set of formulas such that

- every variable in V is a formula,

- if f and g are formulas, then  $\neg f$ ,  $f \lor g$ , and  $f \land g$  are formulas, and

- if f is a formula and  $v \in V$ , then  $\exists v f$  and  $\forall v f$  are formulas.

A truth assignment for QBF(V) is a function  $\sigma: V \to \{0,1\}$ . If  $a \in \{0,1\}$ , then we will use the notation  $\sigma(v \leftarrow a)$  for the truth assignment defined by

$$\sigma(v \leftarrow a)(w) = \begin{cases} a & \text{if } v = w \\ \sigma(w) & \text{otherwise.} \end{cases}$$

If f is a formula in QBF(V) and  $\sigma$  is a truth assignment, we will write  $\sigma \models f$  to denote that f is true under the assignment  $\sigma$ . The relation  $\models$  is defined recursively in the obvious manner:

```

\begin{array}{l}

-\sigma \models v \text{ iff } \sigma(v) = 1, \\

-\sigma \models \neg f \text{ iff } \sigma \not\models f, \\

-\sigma \models f \lor g \text{ iff } \sigma \models f \text{ or } \sigma \models g, \\

-\sigma \models f \land g \text{ iff } \sigma \models f \text{ and } \sigma \models g, \\

-\sigma \models \exists v f \text{ iff } \sigma \langle v \leftarrow 0 \rangle \models f \text{ or } \sigma \langle v \leftarrow 1 \rangle \models f, \text{ and } \\

-\sigma \models \forall v f \text{ iff } \sigma \langle v \leftarrow 0 \rangle \models f \text{ and } \sigma \langle v \leftarrow 1 \rangle \models f,

\end{array}

```

QBF formulas have the same expressive power as ordinary propositional formulas; however, they are sometimes much more concise. Every QBF formula determines an n-ary boolean relation on the set V which consists of those truth assignments for the variables in V that make the formula true. We will identify each QBF formula with the boolean relation that it determines. In the previous section we showed how to associate an OBDD with each formula of propositional logic. In principle, it is easy to construct OBDDs for  $\exists vf$  and  $\forall vf$  when f is given as an OBDD.

$$- \exists x f = f \mid_{x \leftarrow 0} + f \mid_{x \leftarrow 1}$$

$$- \forall x f = f \mid_{x \leftarrow 0} \cdot f \mid_{x \leftarrow 1}$$

In practice, however, special algorithms are needed to handle quantifiers efficiently [20]. In this paper quantifiers occur most frequently in *relational products* which have the following form

$$\exists \bar{v} \big[ f(\bar{v}) \land g(\bar{v}) \big].$$

We will restrict our attention to this case. In Figure 4, we give an algorithm RelProd that performs this computation in one pass over the BDDs  $f(\bar{v})$  and  $g(\bar{v})$ . This is important in practice since the relational product is computed without ever constructing the BDD for

$$f(\bar{v}) \wedge g(\bar{v}),$$

which is often fairly large. Like many OBDD algorithms, RelProd uses a result cache. In this case, entries in the cache are of the form (f, g, E, h), where E is a set of variables that are quantified out and f, g and h are OBDDs. If such an entry is in the cache, it means that a previous call to RelProd(f, g, E) returned h as its result.

Although the algorithm works well in practice, it has exponential complexity in the worst case. Most of the situations where this complexity is observed are cases in which the OBDD for the product is exponentially larger than the OBDDs for the arguments  $f(\bar{v})$  and  $g(\bar{v})$ . In such situations, any method of computing the product must have exponential complexity.

```

function RelProd(f, g: OBDD, E: set of variables): OBDD

if f = false \lor g = false

return false

else if f = true \land g = true

return true

else if (f, g, E, h) is in the result cache

return h

else

let x be the top variable of f

let y be the top variable of g

let z be the topmost of x and y

h_0 := RelProd(f|_{z=0}, g|_{z=0}, E)

h_1 := RelProd(f|_{z=1}, g|_{z=1}, E)

if z \in E

h := Or(h_0, h_1)

/* OBDD for h_0 \vee h_1 */

else

h := IfThenElse(z, h_1, h_0)

/* OBDD for (z \wedge h_1) \vee (\neg z \wedge h_0) */

insert (f, g, E, h) in the result cache

return h

endif

```

Fig. 4. Relational product algorithm

## 4 Computation Tree Logics

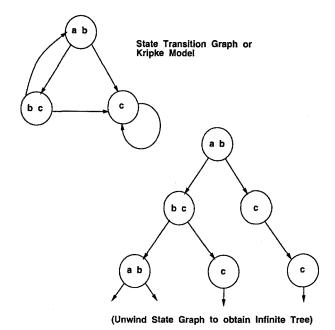

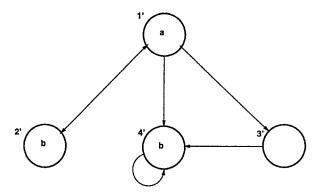

In this paper finite-state systems are modeled by labeled state-transition graphs, called Kripke Structures [49]. If some state is designated as the initial state, then the Kripke structure can be unwound into an infinite tree with that state as the root, as illustrated in Figure 5. Since paths in the tree represent possible computations of the program, we will refer to the infinite tree obtained in this manner as the computation tree of the program. Temporal logics may differ according to how they handle branching in the underlying computation tree. In a linear temporal logic, operators are provided for describing events along a single computation path. In a branching-time logic the temporal operators quantify over the paths that are possible from a given state. The computation tree logic CTL\* [26, 27, 41] combines both branching-time and linear-time operators; a path quantifier, either A ("for all computation paths") or E ("for some computation paths") can prefix an assertion composed of arbitrary combinations of the usual linear-time operators G ("always"), F ("sometimes"), X ("nexttime"), and U ("until"). The remainder of this section gives a precise description of the syntax and semantics of these logics.

There are two types of formulas in  $CTL^*$ : state formulas (which are true in a specific state) and path formulas (which are true along a specific path). Let AP be the set of

Fig. 5. Basic Model of Computation

atomic proposition names. The syntax of state formulas is given by the following rules:

- If  $p \in AP$ , then p is a state formula.

- If f and g are state formulas, then  $\neg f$  and  $f \lor g$  are state formulas.

- If f is a path formula, then  $\mathbf{E}(f)$  is a state formula.

Two additional rules are needed to specify the syntax of path formulas:

- If f is a state formula, then f is also a path formula.

- If f and g are path formulas, then  $\neg f$ ,  $f \lor g$ ,  $\mathbf{X} f$ , and  $f \lor g$  are path formulas.

CTL\* is the set of state formulas generated by the above rules.

We define the semantics of CTL\* with respect to a Kripke structure  $M = \langle S, R, L \rangle$ , where S is the set of states;  $R \subseteq S \times S$  is the transition relation, which must be total (i.e., for all states  $s \in S$  there exists a state  $s' \in S$  such that  $(s, s') \in R$ ); and  $L : S \to \mathcal{P}(AP)$  is a function that labels each state with a set of atomic propositions true in that state. Unless otherwise stated, all of our results apply only to finite Kripke structures.

A path in M is an infinite sequence of states,  $\pi = s_0, s_1, \ldots$  such that for every  $i \geq 0$ ,  $(s_i, s_{i+1}) \in R$ . We use  $\pi^i$  to denote the suffix of  $\pi$  starting at  $s_i$ . If f is a state formula, the notation  $M, s \models f$  means that f holds at state s in the Kripke structure M. Similarly, if f is a path formula,  $M, \pi \models f$  means that f holds along path  $\pi$  in Kripke structure M. When the Kripke structure M is clear from context, we will usually omit it. The relation

$\models$  is defined inductively as follows (assuming that  $f_1$  and  $f_2$  are state formulas and  $g_1$  and  $g_2$  are path formulas):

```

\Leftrightarrow p \in L(s).

1. s \models p

2. s \models \neg f_1

\Leftrightarrow s \not\models f_1.

3. s \models f_1 \lor f_2

\Leftrightarrow s \models f_1 \text{ or } s \models f_2.

4. s \models \mathbf{E}(g_1) \\ 5. \pi \models f_1

\Leftrightarrow there exists a path \pi starting with s such that \pi \models g_1.

\Leftrightarrow s is the first state of \pi and s \models f_1.

6. \pi \models \neg g_1

\Leftrightarrow \pi \not\models g_1.

\Leftrightarrow \pi \models g_1 \text{ or } \pi \models g_2.

7. \pi \models g_1 \vee g_2

\Leftrightarrow \pi^1 \models g_1.

8. \pi \models \mathbf{X} g_1

\Leftrightarrow there exists a k \geq 0 such that \pi^k \models g_2 and for all

9. \pi \models g_1 \cup g_2

0 \le j \le k, \, \pi^j \models g_1.

```

The following abbreviations are used in writing CTL\* formulas:

```

\bullet \ f \land g \equiv \neg(\neg f \lor \neg g) \\ \bullet \ \mathbf{A}(f) \equiv \neg \ \mathbf{E}(\neg f)   \bullet \ \mathbf{G} \ f \equiv \neg \ \mathbf{F} \ \neg f

```

CTL [5, 26] is a restricted subset of CTL\* that permits only branching-time operators—each of the linear-time operators G, F, X, and U must be immediately preceded by a path quantifier. More precisely, CTL is the subset of CTL\* that is obtained if the following two rules are used to specify the syntax of path formulas.

- If f and g are state formulas, then X f and f U g are path formulas.

- If f is a path formula, then so is  $\neg f$ .

Linear temporal logic (LTL), on the other hand, will consist of formulas that have the form A f where f is a path formula in which the only state subformulas permitted are atomic propositions. More precisely, a path formula is either:

- If  $p \in AP$ , then p is a path formula.

- If f and g are path formulas, then  $\neg f$ ,  $f \lor g$ ,  $\mathbf{X} f$ , and  $f \mathbf{U} g$  are path formulas.

It can be shown [24, 41, 55] that the three logics discussed in this section have different expressive powers. For example, there is no CTL formula that is equivalent to the LTL formula  $\mathbf{A}(\mathbf{FG}\,p)$ . Likewise, there is no LTL formula that is equivalent to the CTL formula  $\mathbf{AG}(\mathbf{EF}\,p)$ . The disjunction of these two formulas  $\mathbf{A}(\mathbf{FG}\,p) \vee \mathbf{AG}(\mathbf{EF}\,p)$  is a CTL\* formula that is not expressible in either CTL or LTL.

Most of the specifications in this paper will be written in the logic CTL. There are eight basic CTL operators:

- AX and EX,

- AG and EG,

- AF and EF,

- AU and EU

Each of the eight operators can be expressed in terms of three operators EX, EG, and EU:

```

-\mathbf{AX} f = \neg \mathbf{EX}(\neg f)

-\mathbf{AG} f = \neg \mathbf{EF}(\neg f)

-\mathbf{AF} f = \neg \mathbf{EG}(\neg f)

-\mathbf{EF} f = \mathbf{E}[true \ \mathbf{U} \ f]

-\mathbf{A}[f \ \mathbf{U} \ g] \equiv \neg \mathbf{E}[\neg g \ \mathbf{U} \ \neg f \land \neg g] \land \neg \mathbf{EG} \neg g

```

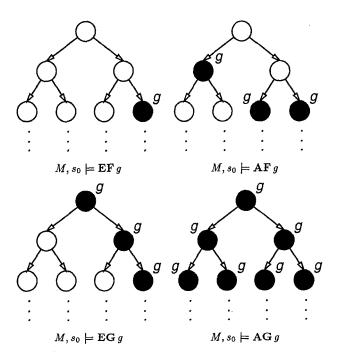

The four operators that are used most widely are illustrated in Figure 6. Each computation tree has the state  $s_0$  as its root.

Finally, some typical CTL formulas that might arise in verifying a finite state concurrent program are given below:

- EF(Started ∧¬Ready): It is possible to get to a state where Started holds but Ready

does not hold.

- AG( $Req \rightarrow$  AF Ack): If a request occurs, then it will be eventually acknowledged.

- AG(AF DeviceEnabled): The proposition DeviceEnabled holds infinitely often on every computation path.

- AG(EF Restart): From any state it is possible to get to the Restart state.

Fig. 6. Basic CTL Operators

### 5 Fixpoint characterization

Let M = (S, R, L) be an arbitrary finite Kripke structure. We use Pred(S) to denote the lattice of predicates over S where each predicate is identified with the set of states in S that make it true and the ordering is set inclusion. Thus, the least element in the lattice is the empty set, denoted by False, and the greatest element in the lattice is the set of all states, denoted by True. A functional F that maps Pred(S) to Pred(S) will be called a  $predicate\ transformer$ . Let  $\tau: Pred(S) \longrightarrow Pred(S)$  be such a functional, then

- 1.  $\tau$  is monotonic provided that  $P \subseteq Q$  implies  $\tau[P] \subseteq \tau[Q]$ ;

- 2.  $\tau$  is  $\cup$ -continuous provided that  $P_1 \subseteq P_2 \subseteq \ldots$  implies  $\tau[\cup_i P_i] = \cup_i \tau[P_i]$ ;

- 3.  $\tau$  is  $\cap$ -continuous provided that  $P_1 \supseteq P_2 \supseteq \dots$  implies  $\tau[\cap_i P_i] = \cap_i \tau[P_i]$ .

A monotonic predicate transformer  $\tau$  on Pred(S) always has a least fixpoint, Ifp  $Z [\tau(Z)]$ , and a greatest fixpoint, gfp  $Z [\tau(Z)]$  (see Tarski [76]): Ifp  $Z [\tau(Z)] = \cap \{Z \mid \tau(Z) = Z\}$  whenever  $\tau$  is monotonic, and Ifp  $Z [\tau(Z)] = \cup_i \tau^i(False)$  whenever  $\tau$  is also  $\cup$ -continuous; gfp  $Z [\tau(Z)] = \cup \{Z \mid \tau(Z) = Z\}$  whenever  $\tau$  is monotonic, and gfp  $Z [\tau(Z)] = \cap_i \tau^i(True)$  whenever  $\tau$  is also  $\cap$ -continuous.

The following lemmas are useful in working with predicate transformers defined on finite Kripke structures.

**Lemma 1.** Let M be a finite Kripke structure and let  $\tau$  be a functional over Pred(S). If  $\tau$  is monotonic then  $\tau$  is also  $\cup$ -continuous and  $\cap$ -continuous.

**Lemma 2.** If  $\tau$  is monotonic, then for every i,  $\tau^i(False) \subseteq \tau^{i+1}(False)$  and  $\tau^i(True) \supseteq \tau^{i+1}(True)$ .

Lemma 3. If  $\tau$  is monotonic and M is finite, then there is an integer  $i_0$  such that for every  $j \geq i_0$ ,  $\tau^j(False) = \tau^{i_0}(False)$ . Similarly, there is some  $j_0$  such that for every  $j \geq j_0$ ,  $\tau^j(True) = \tau^{j_0}(True)$ .

Lemma 4. If  $\tau$  is monotonic and M is finite, then there is an integer  $i_0$  such that lfp  $Z[\tau(Z)] = \tau^{i_0}(False)$ . Similarly, there is an integer  $j_0$  such that gfp  $Z[\tau(Z)] = \tau^{j_0}(True)$ .

As a consequence of the preceding lemmas, if  $\tau$  is monotonic, its least fixpoint can be computed by the program in Figure 7. The invariant for the while loop in the body of the procedure is given by the assertion

$$(Q' = \tau[Q]) \land (Q' \subseteq \operatorname{lfp} Z[\tau(Z)])$$

It is easy to see that at the beginning of the *i*-th iteration of the loop,  $Q = \tau^{i-1}(False)$  and  $Q' = \tau^i(False)$ . Lemma 2 implies that

$$False \subseteq \tau(False) \subseteq \tau^2(False) \subseteq \dots$$

Consequently, the maximum number of iterations before the while loop terminates is bounded by the number of elements in the set S. When the loop does terminate, we will have that  $Q = \tau[Q]$  and that  $Q \subseteq \text{lfp } Z [\tau(Z)]$ . It follows directly that  $Q = \text{lfp } Z [\tau(Z)]$

```

function Lfp(Tau: PredicateTransformer): Predicate

begin

Q := False;

Q' := Tau(Q);

while (Q \neq Q') do

begin

Q := Q';

Q' := Tau(Q')

end;

return(Q)

```

Fig. 7. Procedure for computing least fixpoints.

and that the value returned by the procedure is the required least fixpoint. The greatest fixpoint of  $\tau$  may be computed in a similar manner by the program in Figure 8. Essentially the same argument can be used to show that the procedure terminates and that the value it returns is  $\operatorname{\mathbf{gfp}} Z\left[\tau(Z)\right]$ .

```

function Gfp(Tau: Predicate Transformer): Predicate begin Q:=True; Q':=Tau(Q); while (Q \neq Q') do begin Q:=Q'; Q':=Tau(Q') end; return(Q)

```

Fig. 8. Procedure for computing greatest fixpoints.

If we identify each CTL formula f with the predicate  $\{s \mid M, s \models f\}$  in Pred(S), then each of the basic CTL operators may be characterized as a least or greatest fixpoint of an appropriate predicate transformer.

```

-\mathbf{A}[f_1 \cup f_2] = \operatorname{lfp} Z \left[ f_2 \vee (f_1 \wedge \mathbf{A} \times Z) \right] \\ - \mathbf{E}[f_1 \cup f_2] = \operatorname{lfp} Z \left[ f_2 \vee (f_1 \wedge \mathbf{E} \times Z) \right] \\ - \mathbf{AF} f_1 = \operatorname{lfp} Z \left[ f_1 \vee \mathbf{A} \times Z \right] \\ - \mathbf{EF} f_1 = \operatorname{lfp} Z \left[ f_1 \vee \mathbf{E} \times Z \right] \\ - \mathbf{AG} f_1 = \operatorname{gfp} Z \left[ f_1 \wedge \mathbf{A} \times Z \right] \\ - \mathbf{EG} f_1 = \operatorname{gfp} Z \left[ f_1 \wedge \mathbf{E} \times Z \right]

```

We will only prove the fixpoint characterizations for EG and EU. The fixpoint characterizations of the remaining CTL operators can be established in a similar manner.

Lemma 5.  $\tau(Z) = f_1 \wedge \mathbf{EX} Z$  is monotonic.

*Proof.* Let  $P_1 \subseteq P_2$ . To show that  $\tau[P_1] \subseteq \tau[P_2]$ , consider some state  $s \in \tau[P_1]$ . Then  $s \models f_1$  and there exists a state s' such that  $(s, s') \in R$  and  $s' \in P_1$ . Since  $P_1 \subseteq P_2$ ,  $s' \in P_2$  as well. Thus,  $s \in \tau[P_2]$ .  $\square$

**Lemma 6.** Let  $\tau(Z) = f_1 \wedge \mathbf{EX} Z$  and let  $\tau^{i_0}(True)$  be the limit of the sequence  $True \supseteq \tau(True) \supseteq \ldots$ . For every  $s \in S$ , if  $s \in \tau^{i_0}(True)$  then  $s \models f_1$ , and there is a state s' such that  $(s, s') \in R$  and  $s' \in \tau^{i_0}(True)$ .

Proof. Let  $s \in \tau^{i_0}(True)$ , then since  $\tau^{i_0}(True)$  is a fixpoint,  $\tau^{i_0}(True) = \tau[\tau^{i_0}(True)]$ . Thus,  $s \in \tau[\tau^{i_0}(True)]$ . By definition of  $\tau$  we get that  $s \models f_1$  and there is a state s', such that  $(s,s') \in R$  and  $s' \in \tau^{i_0}(True)$ .  $\square$

Lemma 7. EG  $f_1$  is a fixpoint of the functional  $\tau(Z) = f_1 \wedge \mathbf{EX} Z$ .

Proof. Suppose  $s_0 \models \mathbf{EG} f_1$ . Then by the definition of  $\models$ , there is a path  $s_0, s_1, \ldots$  in M such that for all k,  $s_k \models f_1$ . This implies that  $s_0 \models f_1$  and  $s_1 \models \mathbf{EG} f_1$ . In other words,  $s_0 \models f_1$  and  $s_0 \models \mathbf{EX} \mathbf{EG} f_1$ . Thus,  $\mathbf{EG} f_1 \subseteq f_1 \wedge \mathbf{EX} \mathbf{EG} f_1$ . Similarly, if  $s_0 \models f_1 \wedge \mathbf{EX} \mathbf{EG} f_1$ , then  $s_0 \models \mathbf{EG} f_1$ . Consequently,  $\mathbf{EG} f_1 = f_1 \wedge \mathbf{EX} \mathbf{EG} f_1$ .  $\square$

**Lemma 8.** EG  $f_1$  is the greatest fixpoint of the functional  $\tau(Z) = f_1 \wedge \text{EX } Z$ .

*Proof.* Since  $\tau$  is monotonic, by lemma 1 it is also  $\cap$ -continuous. Therefore, in order to show that EG  $f_1$  is the greatest fixpoint of  $\tau$ , it is sufficient to prove that EG  $f_1 = \bigcap_i \tau^i(True)$ .

We first show that  $\mathbf{EG} f_1 \subseteq \cap_i \tau^i(True)$ . We establish this claim by applying induction on i to show that, for every i,  $\mathbf{EG} f_1 \subseteq \tau^i(True)$ . Clearly,  $\mathbf{EG} f_1 \subseteq True$ . Assume that  $\mathbf{EG} f_1 \subseteq \tau^n(True)$ . Since  $\tau$  is monotonic,  $\tau[\mathbf{EG} f_1] \subseteq \tau^{n+1}(True)$ . By Lemma 7,  $\tau[\mathbf{EG} f_1] = \mathbf{EG} f_1$ . Hence,  $\mathbf{EG} f_1 \subseteq \tau^{n+1}(True)$ .

To show that  $\cap_i \tau^i(True) \subseteq \mathbf{EG} f_1$ , consider some state  $s \in \cap_i \tau^i(True)$ . This state is included in every  $\tau^i(True)$ . Hence, it is also in the fixpoint  $\tau^{i_0}(True)$ . By Lemma 6, s is the start of an infinite sequence of states in which each state is related to the previous one by the relation R. Furthermore, each state in the sequence satisfies  $f_1$ . Thus,  $s \models \mathbf{EG} f_1$ .  $\square$

**Lemma 9.**  $E[f_1 \cup f_2]$  is the least fixpoint of the functional  $\tau(Z) = f_2 \vee (f_1 \wedge EX Z)$ .

Proof. First we notice that  $\tau(Z) = f_2 \vee (f_1 \wedge \mathbf{EX} Z)$  is monotonic. By Lemma 1,  $\tau$  is therefore  $\cup$ -continuous. It is also straightforward to show that  $\mathbf{E}[f_1 \ \mathbf{U} \ f_2]$  is a fixpoint of  $\tau(Z)$ . We still need to prove that  $\mathbf{E}[f_1 \ \mathbf{U} \ f_2]$  is the least fixpoint of  $\tau(Z)$ . For that, it is sufficient to show that  $\mathbf{E}[f_1 \ \mathbf{U} \ f_2] = \cup_i \tau^i(False)$ . For the first direction, it is easy to prove by induction on i that for every i,  $\tau^i(False) \subseteq \mathbf{E}[f_1 \ \mathbf{U} \ f_2]$ . Consequently, we have that  $\cup_i \tau^i(False) \subseteq \mathbf{E}[f_1 \ \mathbf{U} \ f_2]$ .

The other direction,  $\mathbf{E}[f_1 \mathbf{U} f_2] \subseteq \bigcup_i \tau^i(False)$ , is proved by induction on the length of the prefix of the path along which  $f_1 \mathbf{U} f_2$  is satisfied. More specifically, if  $s \models \mathbf{E}[f_1 \mathbf{U} f_2]$  then there is a path  $\pi = s_1, s_2, \ldots$  with  $s = s_1$  and  $j \ge 1$  such that  $s_j \models f_2$  and for all l < j,  $s_l \models f_1$ . We show that for every such state s,  $s \in \tau^j(False)$ . The basis case is trivial. If j = 1,  $s \models f_2$  and therefore  $s \in \tau(False) = f_2 \vee (f_1 \wedge EX(False))$ .

For the inductive step, assume that the above claim holds for every s and every  $j \le n$ . Let s be the start of a path  $\pi = s_1, s_2, \ldots$  such that  $s_{n+1} \models f_2$  and for every l < n+1,  $s_l \models f_1$ . Consider the state  $s_2$  on the path. It is the start of a prefix of length n along which  $f_1 \cup f_2$  holds and therefore, by the induction hypothesis,  $s_2 \in \tau^n(False)$ . Since  $(s, s_2) \in R$  and  $s \models f_1, s \in f_1 \land EX(\tau^n(False))$ , thus  $s \in \tau^{n+1}(False)$ .  $\square$

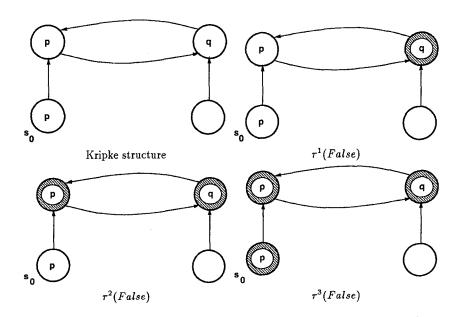

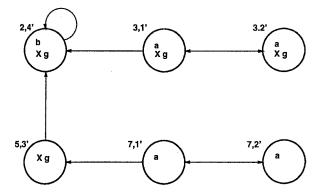

Figure 9 shows how the set of states that satisfy  $\mathbf{E}[p\ \mathbf{U}\ q]$  may be computed for a simple Kripke structure by using the procedure Lfp. In this case the functional  $\tau$  is given by

$$\tau(Z) = q \vee (p \wedge \mathbf{EX} Z).$$

The figure demonstrates how the sequence of approximations  $\tau^i(False)$  converges to  $\mathbf{E}[p\ \mathbf{U}\ q]$ . The states that constitute the current approximation to  $\mathbf{E}[p\ \mathbf{U}\ q]$  are shaded. It is easy to see that  $\tau^3(False) = \tau^4(False)$ . Hence,  $\mathbf{E}[p\ \mathbf{U}\ q] = \tau^3(False)$ . Because  $s_0$  is in  $\tau^3(False)$ , we see that  $M, s_0 \models \mathbf{E}[p\ \mathbf{U}\ q]$ .

Fig. 9. Sequence of Approximations for E[p U q]

### 6 Symbolic Model Checking

Model checking is the problem of finding the set of states in a state transition graph where a given CTL formula is true. There is a program called EMC (Extended Model Checker) that solves this problem using efficient graph-traversal techniques. If the model is represented as a state transition graph, the complexity of the algorithm is linear in the size of the graph and in the length of the formula. The algorithm is quite fast in practice [26, 27]. However, an explosion in the size of the model may occur when the state transition graph is extracted from a finite state concurrent system that has many processes or components.

In this section, we describe a symbolic model checking algorithm for CTL which uses OBDDs to represent the state transition graph. Assume that the behavior of the concurrent system is determined by n boolean state variables  $v_1, v_2, \ldots, v_n$ . The transition relation  $R(\bar{v}, \bar{v}')$  for the concurrent system will be given as a boolean formula in terms of two copies of the state variables:  $\bar{v} = (v_1, \ldots, v_n)$  which represents the current state and  $\bar{v}' = (v'_1, \ldots, v'_n)$  which represents the next state. The formula  $R(\bar{v}, \bar{v}')$  is now converted to an OBDD. This usually results in a very concise representation of the transition relation.

The symbolic model checking algorithm is implemented by a procedure *Check* that takes the CTL formula to be checked as its argument and returns an OBDD that represents exactly those states of the system that satisfy the formula. Of course, the output of *Check* depends on the system being checked; this parameter is implicit in the discussion below. We define *Check* inductively over the structure of CTL formulas. If f is an atomic proposition  $v_i$ , then Check(f) is simply the OBDD for  $v_i$ . Formulas of the form  $\mathbf{EX} f$ ,  $\mathbf{E}[f \mathbf{U} g]$ , and  $\mathbf{EG} f$  are handled by the procedures:

$$Check(\mathbf{EX} f) = CheckEX(Check(f)),$$

$Check(\mathbf{E}[f \cup g]) = CheckEU(Check(f), Check(g)),$

$Check(\mathbf{EG} f) = CheckEG(Check(f)).$

Notice that these intermediate procedures take boolean formulas as their arguments, while Check takes a CTL formula as its argument. The cases of CTL formulas of the form  $f \vee g$  or  $\neg f$  are handled using the standard algorithms for computing boolean connectives with OBDDs. Since  $\mathbf{AX} f$ ,  $\mathbf{A} [f \cup g]$  and  $\mathbf{AG} f$  can all be rewritten using just the above operators, this definition of Check covers all CTL formulas.

The procedure for CheckEX is straightforward since the formula  $\mathbf{EX} f$  is true in a state if the state has a successor in which f is true.

$$CheckEX(f(\bar{v})) = \exists \bar{v}' \left[ f(\bar{v}') \land R(\bar{v}, \bar{v}') \right].$$

If we have OBDDs for f and R, then we can compute an OBDD for

$$\exists \bar{v}' \left[ f(\bar{v}') \land R(\bar{v}, \bar{v}') \right].$$

by using the techniques described in Section 3.

The procedure for *CheckEU* is based on the least fixpoint characterization for the CTL operator **EU** that is given in Section 5.

$$CheckEU(f(\bar{v}), g(\bar{v})) = \mathbf{lfp} Z(\bar{v}) \left[ g(\bar{v}) \vee \left( f(\bar{v}) \wedge CheckEX(Z(\bar{v})) \right) \right].$$

In this case we use the function Lfp to compute a sequence of approximations

$$Q_0, Q_1, \ldots, Q_i, \ldots$$

that converges to  $\mathbf{E}[f\,\mathbf{U}\,g]$  in a finite number of steps. If we have OBDDs for f,g, and the current approximation  $Q_i$ , then we can compute an OBDD for the next approximation  $Q_{i+1}$ . Since OBDDs provide a canonical form of boolean functions, it is easy to test for convergence by comparing consecutive approximations. When  $Q_i = Q_{i+1}$ , the function Lfp terminates. The set of states corresponding to  $\mathbf{E}[f\,\mathbf{U}\,g]$  will be represented by the OBDD for  $Q_i$ .

CheckEG is similar. In this case the procedure is based on the greatest fixpont characterization for the CTL operator EG that is given in Section 5.

$$CheckEG(f(\bar{v})) = \mathbf{gfp} \, Z(\bar{v}) \, \big[ f(\bar{v}) \wedge CheckEX(Z(\bar{v})) \big].$$

If we have an OBDD for f, then the function Gfp can be used to compute an OBDD representation for the set of states that satisfy  $\mathbf{EG} f$ .

#### 7 Fairness Constraints

Next, we consider the issue of fairness. In many cases, we are only interested in the correctness along fair computation paths. For example, if we are verifying an asynchronous circuit with an arbiter, we may wish to consider only those executions in which the arbiter does not ignore one of its request inputs forever. This type of property cannot be expressed directly in CTL. In order to handle such properties we must modify the semantics of CTL slightly. A fairness constraint can be an arbitrary set of states, usually described by a formula of the logic. A path is said to be fair with respect to a set of fairness constraints if each constraint holds infinitely often along the path. The path quantifiers in CTL formulas are then restricted to fair paths. In the remainder of this section we describe how to modify the algorithm above to handle fairness constraints. We assume the fairness constraints are given by a set of CTL formulas  $H = \{h_1, \ldots, h_n\}$ . We define a new procedure CheckFair for checking CTL formulas relative to the fairness constraints in H. We do this by giving definitions for new intermediate procedures CheckFairEU, and CheckFairEG which correspond to the intermediate procedures used to define Check.

Consider the formula  $\mathbf{EG} f$  given fairness constraints H. The formula means that there exists a path beginning with the current state on which f holds globally (invariantly) and each formula in H holds infinitely often on the path. The set of such states S is the largest set with the following two properties:

- 1. all of the states in S satisfy f, and

- 2. for all fairness constraints  $h_k \in H$  and all states  $s \in S$ , there is a sequence of states of length one or greater from s to a state in S satisfying  $h_k$  such that all states on the path satisfy f.

It is easy to show that if these conditions hold, each state in the set is the beginning of an infinite computation path on which f is always true, and for which every formula in H holds infinitely often. Thus, the procedure  $CheckFairEG(f(\bar{v}))$  will compute the greatest fixpoint

$$\mathbf{gfp}\,Z(\bar{v})\,\big[f(\bar{v})\wedge\bigwedge_{k=1}^{n}\,CheckEX(CheckEU(f(\bar{v}),Z(\bar{v})\wedge\,Check(h_{k})))\big].$$

The fixed point can be evaluated in the same manner as before. The main difference is that each time the above expression is evaluated, several nested fixed point computations are done (inside CheckEU).

Checking  $\mathbf{E}\mathbf{X} f$  and  $\mathbf{E}[f\mathbf{U}g]$  under fairness constraints is simpler. The set of all states which are the start of some fair computation is

$$fair(\tilde{v}) = CheckFair(\mathbf{EG}\,True).$$

The formula  $\mathbf{E}\mathbf{X}f$  is true under fairness constraints in a state s if and only if there is a successor state s' such that s' satisfies f and s' is at the beginning of some fair computation path. It follows that the formula  $\mathbf{E}\mathbf{X}f$  (under fairness constraints) is equivalent to the formula  $\mathbf{E}\mathbf{X}(f \wedge fair)$  (without fairness constraints). Therefore, we define

$$CheckFairEX(f(\bar{v})) = CheckEX(f(\bar{v}) \wedge fair(\bar{v})).$$

Similarly, the formula  $\mathbf{E}[f \ \mathbf{U} \ g]$  (under fairness constraints) is equivalent to the formula  $\mathbf{E}[f \ \mathbf{U} \ (g \land fair)]$  (without fairness constraints). Hence, we define

$$CheckFairEU(f(\bar{v}),g(\bar{v})) = CheckEU(f(\bar{v}),g(\bar{v}) \wedge fair(\bar{v})).$$

## 8 Counterexamples and witnesses

One of the most important features of CTL model checking algorithms is the ability to find counterexamples and witnesses. When this feature is enabled and the model checker determines that a formula with a universal path quantifier is false, it will find a computation path which demonstrates that the negation of the formula is true. Likewise, when the model checker determines that a formula with an existential path quantifier is true, it will find a computation path that demonstrates why the formula is true. For example, if the model checker discovers that the formula  $\mathbf{AG} f$  is false, it will produce a path to a state in which  $\neg f$  holds. Similarly, if it discovers that the formula  $\mathbf{EF} f$  is true, it will produce a path to a state in which f holds. Note that the counterexample for a universally quantified formula is the witness for the dual existentially quantified formula. By exploiting this observation we can restrict our discussion of this feature to finding witnesses for the three basic CTL operators  $\mathbf{EX}$ ,  $\mathbf{EG}$ , and  $\mathbf{EU}$ .

In order to find the witness for some CTL formula we will need to examine the strongly connected components of the transition graph determined by the Kripke structure. We will say that two states  $s_1$  and  $s_2$  are equivalent if there is a path from  $s_1$  to  $s_2$  and also from  $s_2$  to  $s_1$ . We will call the equivalence classes of this relation strongly connected components. We can form a new graph in which the nodes are the strongly connected

components and there is an edge from one strongly connected component to another if and only if there is an edge from a state in one to a state in the other. It is easy to see that the new graph does not contain any proper cycles, i.e., each cycle in the graph is contained in one of the strongly connected components. Moreover, since we only consider finite Kripke structures, each infinite path must have a suffix that is entirely contained within a strongly connected component of the transition graph.

We start by considering the problem of how to find a witness for the formula  $\mathbf{EG} f$  under the set of fairness constraints  $H = \{h_1, \ldots, h_n\}$ . We will identify each  $h_i$  with the set of states that make it true. Recall that the set of states that satisfy the formula  $\mathbf{EG} f$  with the fairness constraints H is given by the formula

$$\operatorname{gfp} Z\left[f \wedge \bigwedge_{k=1}^{n} \operatorname{EX}(\operatorname{E}[f \cup Z \wedge h_{k}])\right] \tag{1}$$

For brevity, we will use  $\mathbf{EG} f$  to denote the set of states that satisfy  $\mathbf{EG} f$  under the fairness constraints H. Given a state s in  $\mathbf{EG} f$ , we would like to exhibit a path  $\pi$  starting with s, which satisfies f in every state, and visits every set  $h \in H$  infinitely often. In general, such a path will consist of a finite prefix followed by a repeating cycle. We construct the path incrementally by giving a sequence of prefixes of the path of increasing length until a cycle is found. At each step in the construction we must ensure that the current prefix can be extended to a fair path along which each state satisfies f. This invariant is guaranteed by making sure that each time we add a state to the current prefix, the state satisfies  $\mathbf{EG} f$ .

First, we evaluate the above fixpoint formula. In every iteration of the outer fixpoint computation, we compute a collection of least fixpoints associated with the formulas  $\mathbf{E}[f \ \mathbf{U} \ Z \wedge h]$ , for each fairness constraint  $h \in H$ . For every constraint h, we obtain an increasing sequence of approximations  $Q_0^h, Q_1^h, Q_2^h, \ldots$ , where  $Q_i^h$  is the set of states from which a state in  $Z \wedge h$  can be reached in i or fewer steps, while satisfying f. In the last iteration of the outer fixpoint when  $Z = \mathbf{EG} f$ , we save the sequence of approximations  $Q^h$  for each h in H.

Now, suppose we are given an initial state s satisfying  $\mathbf{EG} f$ . Then s belongs to the set of states computed in equation (1), so it must have a successor in  $\mathbf{E}[f \mathbf{U} (\mathbf{EG} f) \wedge h]$  for each  $h \in H$ . In order to minimize the length of the witness path, we choose the first fairness constraint that can be reached from s. This is accomplished by testing the saved sets  $Q_i^h$  for increasing values of i until one is found that contains some successor t of s. Note that since  $t \in Q_i^h$ , it has a path to a state in  $(\mathbf{EG} f) \wedge h$  and therefore t is in  $\mathbf{EG} f$ . If i > 0, we find a successor of t in  $Q_{i-1}^h$ . This is done by finding the set of successors of t, intersecting it with  $Q_{i-1}^h$ , and then choosing an arbitrary element of the resulting set. Continuing until i = 0, we obtain a path from the initial state s to some state in  $(\mathbf{EG} f) \wedge h$ . We then eliminate h from further consideration, and repeat the above procedure until all of the fairness constraints have been visited. Let s' be the final state of the path obtained thus far.

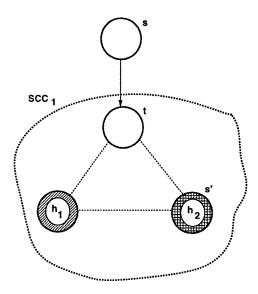

To complete a cycle, we need a non-trivial path from s' to the state t along which each state satisfies f. In other words, we need a witness for the formula  $\{s'\} \land \mathbf{EX} \ \mathbf{E}[f \ \mathbf{U} \ \{t\}]$ . If this formula is true, we have found the witness path for s. This case is illustrated in Figure 10. If the formula is false, there are several possible strategies. The simplest is

Fig. 10. Witness is in first strongly connected component

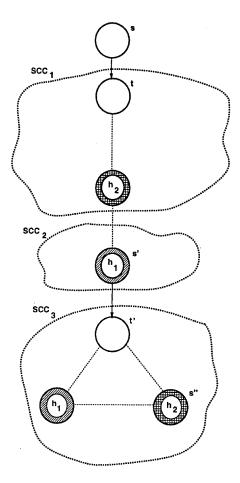

to restart the procedure from the final state s'. Since  $\{s'\} \land \mathbf{EXE}[f \ \mathbf{U} \ \{t\}]$  is false, we know that s' is not in the strongly connected component of f containing t, however s' is in  $\mathbf{EG} f$ . Thus, if we continue this strategy, we must descend in the directed acyclic graph of strongly connected components, eventually either finding a cycle  $\pi$ , or reaching a terminal strongly connected component of f. In the latter case, we are guaranteed to find a cycle, since we cannot exit a terminal strongly connected component. This case is illustrated in Figure 11.

A slightly more sophisticated approach would be to precompute  $\mathbf{E}[(\mathbf{EG}\,f)\,\mathbf{U}\,\{t\}]$ . The first time we exit this set, we know the cycle cannot be completed, so we restart from that state. Heuristically, these approaches tend to find short counterexamples (probably because the number of strongly connected components tends to be small), so no attempt is made to find the shortest cycle.

The witness procedure for EG f under fairness constraints H can be used to extend witnesses for E[f U g] and EX f to infinite fair paths. Let fair be the set of states that satisfy EG True under the fairness constraints H. We can compute E[f U g] under H by using the standard CTL model checking algorithm (without fairness constraints) to compute E[f U  $(g \land fair)$ ]. Similarly, We can compute EX f by using the standard CTL model checking algorithm to compute EX  $(f \land fair)$ .

### 9 LTL Model Checking

In this section we consider the model checking problem for linear temporal logic. Let A f be a linear temporal logic formula. Thus, f is a restricted path formula in which the only

Fig. 11. Witness spans three strongly connected components

state subformulas are atomic propositions. We wish to determine all of those states  $s \in S$  such that  $M, s \models Af$ . By definition  $M, s \models Af$  iff  $M, s \models \neg E \neg f$ . Consequently, it is sufficient to be able to check the truth of formulas of the form Ef where f is a restricted path formula. If the Kripke structure is represented explicitly as a state transition graph, this problem is known to be PSPACE-complete [74] in general.

Lichtenstein and Pnueli [56] developed an algorithm for the problem that was linear in the size of the model M and exponential in the length of the formula f. Although their algorithm was linear in the size of the model, it was still impractical for large examples because of the state explosion problem. As in the case of CTL model checking, representing the transition relation as an OBDD enables the procedure to be applied to much larger examples. The exponential complexity of their algorithm in terms of formula length is caused by a tableau construction which may require exponential space in the

size of the formula. Fortunately, the tableau can also be represented by an OBDD. This leads to an additional reduction in space and time.

We begin with an informal description of the model checking algorithm. Given a formula  $\mathbf{E} f$  and a Kripke structure M, we construct a special Kripke structure T called the tableau for the path formula f. This structure includes every path that satisfies f. By composing T with M, we find the set of paths that appear in both T and M. A state in M will satisfy  $\mathbf{E} f$  if and only if it is the start of a path in the composition that satisfies f. The CTL model checking procedure described in Section 6 is used to find these states.

We now describe the construction of the tableau T in detail. Let  $AP_f$  be the set of atomic propositions in f. The tableau associated with f is a structure  $T = (S_T, R_T, L_T)$  with  $AP_f$  as its set of atomic propositions. Each state in the tableau is a set of elementary formulas obtained from f. The set of elementary subformulas of f is denoted by el(f) and is defined recursively as follows:

```

\begin{aligned}

&-el(p) = \{p\} \text{ if } p \in AP. \\

&-el(\neg g) = el(g). \\

&-el(g \lor h) = el(g) \cup el(h). \\

&-el(\mathbf{X} g) = \{\mathbf{X} g\} \cup el(g). \\

&-el(g \mathbf{U} h) = \{\mathbf{X} (g \mathbf{U} h)\} \cup el(g) \cup el(h).

\end{aligned}

```

Thus, the set of states  $S_T$  of the tableau is  $\mathcal{P}(el(f))$ . The labeling function  $L_T$  is defined so that each state is labeled by the set of atomic propositions contained in the state.

In order to construct the transition relation  $R_T$ , we need an additional function sat that associates with each subformula g of f a set of states in  $S_T$ . Intuitively, sat(g) will be the set of states that satisfy g.

```

- sat(g) = \{ \sigma \mid g \in \sigma \} \text{ where } g \in el(f).

- sat(\neg g) = \{ \sigma \mid \sigma \notin sat(g) \}.

- sat(g \lor h) = sat(g) \cup sat(h).

- sat(g \lor h) = sat(h) \cup (sat(g) \cap sat(\mathbf{X}(g \lor h))).

```

We want the transition relation to have the property that each elementary formula in a state is true in that state. Clearly, if Xg is in some state  $\sigma$ , then all the successors of  $\sigma$  should satisfy g. Furthermore, since we are dealing with LTL formulas, if Xg is not in  $\sigma$ , then  $\sigma$  should satisfy  $\neg Xg$ . Hence, no successor of  $\sigma$  should satisfy g. The obvious definition for  $R_T$  is

$$R_T(\sigma,\sigma') = \bigwedge_{\mathbf{X}_g \in el(f)} \sigma \in sat(\mathbf{X}_g) \Leftrightarrow \sigma' \in sat(g).$$

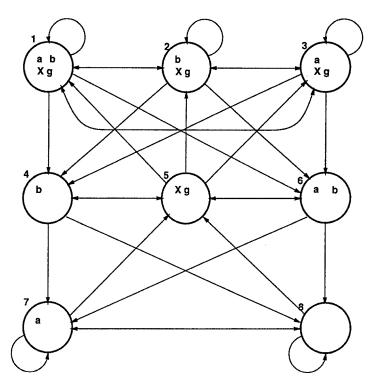

Figure 12 gives the transition relation  $R_T$  for the formula  $g = a\mathbf{U}b$ . To reduce the number of edges, we connect two states  $\sigma$  and  $\sigma'$  with a bidirectional arrow if there is an edge from  $\sigma$  to  $\sigma'$  and also from  $\sigma'$  to  $\sigma$ . Each subset of el(g) is a state of T.  $sat(\mathbf{X}g) = \{1, 2, 3, 5\}$  since each of these states contains the formula  $\mathbf{X}g$ .  $sat(g) = \{1, 2, 3, 4, 6\}$  since each of these states either contains b or contains a and a and a and a are in a are in a are in a and a are in the complement of a are in the complement of a and a are in the complement

Fig. 12. Tableau for a U b

Unfortunately, the definition of  $R_T$  does not guarantee that eventuality properties are fulfilled. We can see this behavior in Figure 12. Although state 3 belongs to sat(g), the path that loops forever in state 3 does not satisfy the formula g since b never holds on that path. Consequently, an additional condition is necessary in order to identify those paths along which f holds. A path  $\pi$  that starts from a state  $\sigma \in sat(f)$  will satisfy f if and only if

- For every subformula  $g \cup h$  of f and for every state  $\sigma$  on  $\pi$ , if  $\sigma \in sat(g \cup h)$  then either  $\sigma \in sat(h)$  or there is a later state  $\tau$  on  $\pi$  such that  $\tau \in sat(h)$ .

In order to state the key property of the tableau construction, we must introduce some new notation. Let  $\pi = s_0, s_1, \ldots$  be a path in a Kripke structure M, then  $label(\pi) = L(s_0), L(s_1), \ldots$  Let  $l = l_0, l_1, \ldots$  be a sequence of subsets of some set  $\Sigma$  and let  $\Sigma' \subseteq \Sigma$ . The restriction of l to  $\Sigma'$ , denoted by  $l \mid_{\Sigma'}$ , is the sequence  $l'_0, l'_1, \ldots$  where  $l'_i = l_i \cap \Sigma'$  for every  $i \geq 0$ . The following theorem makes precise the intuitive claim that T includes every path which satisfies f.

**Theorem 10.** Let T be the tableau for the path formula f. Then, for every Kripke structure M and every path  $\pi'$  of M, if  $M, \pi' \models f$  then there is a path  $\pi$  in T that starts in a state in sat(f), such that  $label(\pi')|_{AP_r} = label(\pi)$ .

Next, we want to compute the product P = (S, R, L) of the tableau  $T = (S_T, R_T, L_T)$  and the Kripke structure  $M = (S_M, R_M, L_M)$ .

- $-S = \{(\sigma, \sigma') \mid \sigma \in S_T, \sigma' \in S_M \text{ and } L_M(\sigma') \cap AP_f = L_T(\sigma)\}.$

- $R((\sigma, \sigma'), (\tau, \tau'))$  iff  $R_T(\sigma, \tau)$  and  $R_M(\sigma', \tau')$ .

$- L((\sigma, \sigma')) = L_T(\sigma).$