# SAT based Abstraction Refinement for Hardware Verification

Dong Wang May 2003

Electrical and Computer Engineering Department Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

### Thesis Committee:

Edmund Clarke, Chair Randal Bryant Don Thomas Orna Grumberg

Copyright © 2003 by Dong Wang

This research is sponsored by the Gigascale Silicon Research Center (GSRC), the National Science Foundation (NSF) under Grant No. CCR-9803774. Any opinions, findings and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of GSRC, NSF, or the United States Government.

#### Abstract

Model checking is a widely used automatic formal verification technique. Despite the recent advances in model checking technology, its application is still limited by the state explosion problem. For model checking large real world systems, abstraction is essential. This thesis investigates abstraction techniques for the efficient verification of hardware designs with thousands of registers.

A technique, called *SAT conflict dependency analysis*, is developed and used to derive several efficient abstraction algorithms. If a CNF formula is unsatisfiable, this technique can extract a proof of unsatisfiability by analyzing conflict clauses and conflict graphs generated by the SAT procedure.

In this thesis, we propose two new algorithms to improve the efficiency of traditional localization reduction based methods. The first algorithm combines multiple verification engines including BDD, ATPG, SAT, and 3-valued simulation for generating abstract counterexamples and for refinement. When the SAT solver determines that there are no concrete counterexamples corresponding to the abstract counterexample, we generate an unsatisfiability proof using the SAT conflict dependency analysis. The second algorithm identifies a set of registers for refinement based on the extracted proof.

Existing predicate abstraction techniques are designed for verifying infinite state systems. They become inefficient when applied to the verification of large scale hardware designs. We improve the existing predicate abstraction techniques in several directions. First, computing an abstract model involves many validity checks. A pruning technique is introduced, to avoid the validity checks that are guaranteed to fail. Second, the abstract model is refined by adding compact predicates and general transition constraints identified by unsatisfiability proofs. Third, existing refinement algorithms can add unnecessary predicates, called redundant predicates. We propose algorithms to identify and remove the redundant predicates. Fourth, to exploit high level information from Verilog designs, a method is developed to extract relevant branch conditions that can be used as predicates during refinement. Finally, to improve predicate abstraction further, we combine techniques from localization reduction into the abstraction process.

The abstraction refinement algorithms presented in this thesis have been successfully applied to the verification of industrial hardware designs with up to six thousand registers and 250 thousand gates.

### Acknowledgements

I am very fortunate to have Ed Clarke as my adviser during my graduate study. Ed has devoted much effort to teach me how to do research and how to present results effectively. Without his encouragement and invaluable guidance, this thesis would not have been possible. Thanks to all my committee members for their advice and careful reading of my thesis. Randy has given suggestions to extend this work. Don's insight on hardware description languages expands my horizon on verification. Orna has been working with me extensively during her visits to CMU. She has helped me to formalize my ideas and extends them in various directions.

Many thanks to members in our research group. Sergey has always been helpful. I benefit a lot from inspiring discussions with Yuan. His encouragement helps me to get started with research. Helmut, Pankaj and Murali are my research collaborators. Ofer has provided benchmarks used in this thesis. Finally, it has been a great pleasure to work with all the other group members: Will Marrero, Marius Minea, Armin Biere, Yunshan Zhu, Sagar Chaki, Flavio Lerda, Anubhav Gupta, Alex Groce, Nishant Sinha, Daniel Kroening, Joel Ouakinine, Michael Theobald, Karen Yorav and everyone else.

I spent summer 2000 in Synopsys woking with Pei-Hsin Ho, Jiang Long, James Kukula etc. The experience was incredible. The work there becomes an important part of my thesis.

I thank people in ECE and CS facilities for providing an efficient working environment. I would like to acknowledge the financial support of GSRC and NSF. Their support has made this work possible.

I am very grateful to my parents, my brother and my sister. They are always there to support me. And Finally, most of my gratitude goes to my dear wife, Zhuo, for her patience, encouragement and faith in what I am doing.

## Contents

|   | Abs  | bstract<br>cknowledgements |                                                  |    |  |  |  |  |  |  |

|---|------|----------------------------|--------------------------------------------------|----|--|--|--|--|--|--|

|   | Ack  |                            |                                                  |    |  |  |  |  |  |  |

| 1 | Intr | oducti                     | on                                               | 1  |  |  |  |  |  |  |

|   | 1.1  | Backgr                     | round                                            | 2  |  |  |  |  |  |  |

|   | 1.2  | Scope                      | of This Thesis                                   | 5  |  |  |  |  |  |  |

|   | 1.3  | Relate                     | d Work                                           | 9  |  |  |  |  |  |  |

|   |      | 1.3.1                      | SAT Unsatisfiability Proofs                      | 9  |  |  |  |  |  |  |

|   |      | 1.3.2                      | Localization Reduction and Counterexample Guided |    |  |  |  |  |  |  |

|   |      |                            | Refinement                                       | 10 |  |  |  |  |  |  |

|   |      | 1.3.3                      | Predicate Abstraction                            | 12 |  |  |  |  |  |  |

|   |      | 1.3.4                      | Other Abstraction Techniques                     | 15 |  |  |  |  |  |  |

| 2 | Exi  | stential Abstraction       |                                                  |    |  |  |  |  |  |  |

|   | 2.1  | Notati                     | on                                               | 17 |  |  |  |  |  |  |

|   | 2.2  | Existe                     | ntial Abstraction                                | 19 |  |  |  |  |  |  |

|   | 2.3  | Predic                     | ate Abstraction                                  | 22 |  |  |  |  |  |  |

|   |      | 2.3.1                      | A Software Example                               | 29 |  |  |  |  |  |  |

Contents

|   |     | 2.3.2                                               | A Hardware Example                               | 31 |  |  |  |  |

|---|-----|-----------------------------------------------------|--------------------------------------------------|----|--|--|--|--|

|   | 2.4 | Locali                                              | zation Reduction                                 | 39 |  |  |  |  |

|   | 2.5 | Abstra                                              | action Refinement                                | 40 |  |  |  |  |

| 3 | SAT | $\Gamma$ and $\Gamma$                               | Unsatisfiability Proofs                          | 42 |  |  |  |  |

|   | 3.1 | Confli                                              | ct based Learning in SAT Solvers                 | 42 |  |  |  |  |

|   | 3.2 | SAT (                                               | Conflict Dependency Analysis                     | 48 |  |  |  |  |

|   |     | 3.2.1                                               | Dependencies between Conflict Graphs and Clauses | 48 |  |  |  |  |

|   |     | 3.2.2                                               | Incremental SAT                                  | 54 |  |  |  |  |

| 4 | Loc | alizatio                                            | on Reduction                                     | 55 |  |  |  |  |

|   | 4.1 | Overa                                               | pproximate the Abstract Models                   | 56 |  |  |  |  |

|   | 4.2 | Check                                               | ing the Validity of an Abstract Counterexamples  | 59 |  |  |  |  |

|   | 4.3 | 4.3 Invisible Variables In Abstract Counterexamples |                                                  |    |  |  |  |  |

|   |     | 4.3.1                                               | Guided SAT/ATPG                                  | 60 |  |  |  |  |

|   |     | 4.3.2                                               | Efficient Abstract Model Checking                | 62 |  |  |  |  |

|   |     | 4.3.3                                               | Check Counterexample                             | 65 |  |  |  |  |

|   |     | 4.3.4                                               | Refinement Algorithms                            | 66 |  |  |  |  |

|   |     | 4.3.5                                               | Experimental Results                             | 70 |  |  |  |  |

|   | 4.4 | Invisib                                             | ole Variables in Unsatisfiability Proofs         | 75 |  |  |  |  |

|   |     | 4.4.1                                               | Identifying Important Variables                  | 76 |  |  |  |  |

|   |     | 4.4.2                                               | Refinement Minimization                          | 78 |  |  |  |  |

|   |     | 4.4.3                                               | Experimental Results                             | 79 |  |  |  |  |

|   |     | 4.4.4                                               | Performance Improvements                         | 82 |  |  |  |  |

| 5 | SAT | Γ based                                             | d Predicate Abstraction                          | 87 |  |  |  |  |

Contents vi

|   | 5.1 | SAT based Abstraction                                                         |

|---|-----|-------------------------------------------------------------------------------|

|   |     | 5.1.1 Reducing the number of testpoints                                       |

|   | 5.2 | SAT based Refinement                                                          |

|   |     | 5.2.1 Refinement to Exclude Spurious Transitions 97                           |

|   |     | 5.2.2 Refinement by adding a New Predicate 101                                |

|   | 5.3 | Exploit RTL Information                                                       |

|   |     | 5.3.1 Extracting Branch Conditions                                            |

|   |     | 5.3.2 Counterexample-based Lazy Refinement 111                                |

|   | 5.4 | Experimental Results                                                          |

| 6 | Cor | ${f nbine\ Localization\ Reduction\ with\ Predicate\ Abstraction 121}$        |

|   | 6.1 | Identifying Control Variables                                                 |

|   | 6.2 | Combining with Localization Reduction                                         |

|   | 6.3 | Correlations between Control Variables and Predicates 125                     |

|   | 6.4 | Correlations Between Formula Predicates                                       |

|   | 6.5 | Experimental Results                                                          |

| 7 | Rer | noving Redundant Predicates 131                                               |

|   | 7.1 | The Replacement Function                                                      |

|   | 7.2 | Removing Redundant Predicates                                                 |

|   | 7.3 | Redundant Predicates for Safety Properties                                    |

|   | 7.4 | Redundant Predicates for Bisimulation Equivalence 144                         |

|   | 7.5 | Difference in the Bisimulation and $\mathbf{AG}p$ conditions 146              |

|   |     | 7.5.1 A transition relation that satisfies the Bisimulation                   |

|   |     | condition                                                                     |

|   |     | 7.5.2 A transition relation that satisfies the $\mathbf{AG}p$ condition . 148 |

|          | ••   |

|----------|------|

| Contents | VII  |

| Contents | V 11 |

8 Conclusion and Future Work

**150**

## List of Figures

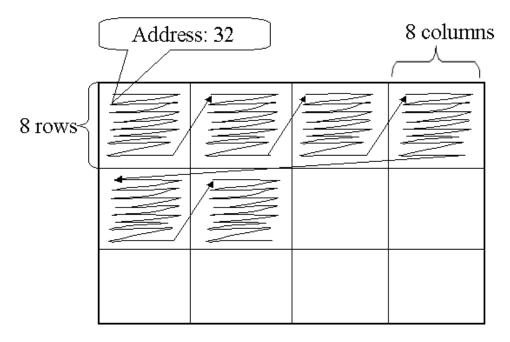

| 2.1 | Fetch each 8x8 pixel block                                                                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

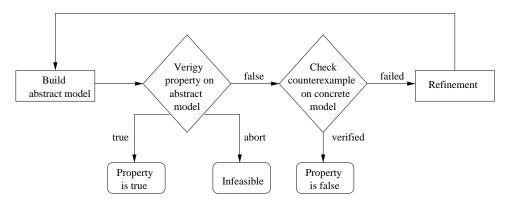

| 2.2 | General Abstraction Refinement framework 41                                                                                                        |

| 3.1 | Basic DPLL backtracking search                                                                                                                     |

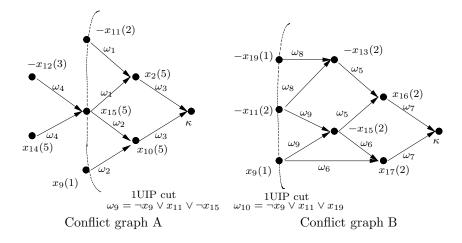

| 3.2 | Two dependent conflict graphs                                                                                                                      |

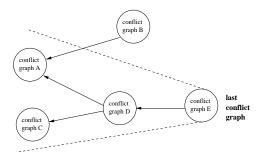

| 3.3 | The conflict dependency graph and the proof graph (within                                                                                          |

|     | dotted lines)                                                                                                                                      |

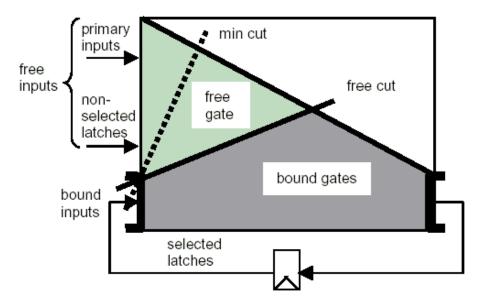

| 4.1 | no-cut and min-cut abstract models (from [40]) 57                                                                                                  |

| 4.2 | Guided-SAT Algorithm                                                                                                                               |

| 4.3 | Refinement Minimization Algorithm                                                                                                                  |

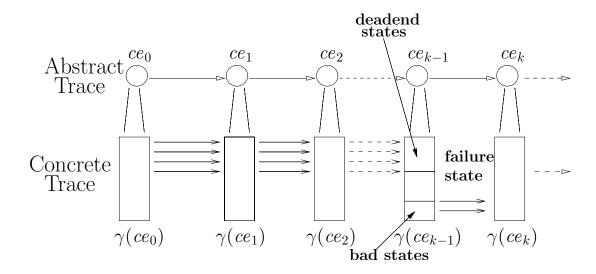

| 4.4 | A spurious prefix and the associated deadend/bad states 77                                                                                         |

| 5.1 | Greedy Minimization Based on Incremental SAT 105                                                                                                   |

| 5.2 | Replace branch conditions using unique signals                                                                                                     |

| 5.3 | A refinement example                                                                                                                               |

| 5.4 | Algorithm to compute $ece_0 \dots \dots$     |

| 5.5 | Algorithm to compute $ece_{i+1} \dots \dots$ |

| 5.6 | Algorithm to compute invalidating predicates                                                                                                       |

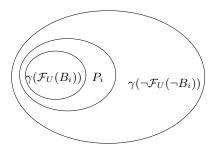

| 7.1 | Relationship                     | between | the | conc | retizati | on of | $B_i$ , | $\mathcal{F}_U$ | $\tau(E)$ | $S_i$ | , 8 | anc | l |     |

|-----|----------------------------------|---------|-----|------|----------|-------|---------|-----------------|-----------|-------|-----|-----|---|-----|

|     | $\neg \mathcal{F}_U(\neg B_i)$ . |         |     |      |          |       |         |                 |           |       |     |     |   | 135 |

## List of Tables

| 2.1 | Predicate abstraction for a C program                                | 31  |

|-----|----------------------------------------------------------------------|-----|

| 4.1 | 3-value simulation of an abstract counterexample                     | 68  |

| 4.2 | Property Verification Results                                        | 72  |

| 4.3 | Unreachable-coverage-state analysis results                          | 74  |

| 4.4 | Comparison between Cadence SMV (CSMV), heuristic score               |     |

|     | based refinement and proof based refinement for larger cir-          |     |

|     | cuits.                                                               | 81  |

| 4.5 | Comparison between [22], heuristic score based refinement and        |     |

|     | proof based refinement for smaller circuits                          | 82  |

| 5.1 | Comparison between localization reduction and predicate abstraction. | 120 |

| 6.1 | Compare the pure predicate abstraction (PRED) with the               |     |

|     | combined algorithm (COMB)                                            | 130 |

## Chapter 1

### Introduction

Model checking is an automatic exhaustive search method for the formal verification of finite state systems. As hardware designs are becoming more and more complex, traditional simulation based methodology has been proven insufficient to find subtle design errors. For many hardware designs, the application of model checking is absolutely essential. For example, bugs in high volume electronic products, such as microprocessors, could cause recall of the chips and incur crippling costs to the manufacturers. Furthermore, design errors in mission critical or safety critical systems may cause catastrophic consequences. One major obstacle for the adoption of model checking into the mainstream design flow is the state explosion problem. This thesis investigates abstraction techniques to alleviate this problem, thus enabling the successful application of model checking to verify large scale hardware designs.

### 1.1 Background

Model checking [25] as introduced by Clarke and Emerson has three basic elements:

- A Kripke structure to model the finite state system under verification,

- A formula in computation tree logic (CTL), which belongs to the temporal logic [63] introduced by Pnueli, to specify the property, and

- An efficient model checking algorithm that for each state determines the truth value of subformulas of the given CTL formula.

Since the system states are explicitly manipulated in the original model checking algorithm, only relatively small designs can be verified. Over the past several years, considerable research has been done to improve the basic model checking algorithm of [25]. Symbolic model checking, bounded model checking (BMC), compositional reasoning and abstraction are some of the major techniques to enable model checking of large systems.

Symbolic model checking based on BDDs was introduced by McMillan [50] as a viable solution to alleviate the state explosion problem. In this approach, sets of states and relations are all encoded using ordered binary decision diagrams (OBDD) [14]. Much larger systems [16] have been verified using this method compared to explicit state model checkers. As part of his Ph.D. thesis, McMillan created a symbolic model checker, the *SMV* system. In SMV, the system under verification is described using an SMV program and the property is described using a CTL formula. SMV encodes the system and performs the fixpoint based model checking algorithms only

using OBDDs. If the formula does not hold on the model, SMV usually produces a counterexample which is a witness for the failure<sup>1</sup>.

A symbolic bounded model checking (BMC) algorithm based on Boolean satisfiability (SAT) solvers was introduced by Biere, Cimatti, Clarke and Zhu in [10]. In BMC, given a linear time temporal logic (LTL) formula, counterexamples of increasing lengths are searched via a reduction to Boolean satisfiability problems. If one of the SAT instances is satisfiable, a counterexample has been found. Recent advances in SAT technology [56, 68, 76] has greatly increased the size of the systems that can be handled by BMC, compared to BDD based model checkers. The effectiveness of BMC has been demonstrated in many verification problems in industry [11,13,26]. However, in order to show the correctness of the LTL formula, a large bound may be necessary. A number of approaches [2,12,37,53,67,73] have been investigated to use SAT solvers for unbounded model checking.

Compositional reasoning [1,4,36,39,51,52,62] is used to reduce the verification of a large system to a number of smaller verification problems. The correctness of the overall system is then established by composing the proofs of correctness of various parts. In this approach, properties of each part are verified by making assumptions on the behavior of other parts. For a part, other parts act as an environment. These assumptions must be proved later when the correctness of other parts is proved. In practice, a complex hardware system is broken into smaller blocks based on the design modularity.

<sup>&</sup>lt;sup>1</sup>Counterexamples are produced only for universal CTL formulas which have either a path or a loop counterexample. Other counterexamples are not produced, only their falsehood is indicated.

For the verification of each block, the assumptions about the environment are specified as input constraints. Over-constraining the inputs will result in false confidence in the correctness of the design. On the other hand, under-constraining the inputs leads to false errors. The difficulty in generating the exact input constraints is a major obstacle to the application of compositional reasoning in industry.

Abstraction is an effective method to alleviate the state explosion problem. There are many abstraction techniques, including the localization reduction [9,18,22,33,43,72], the homomorphic abstraction [21,23,64], the abstraction without explicit abstraction function [60], abstract interpretation [46], the free and constrained abstractions [27], predicate abstraction [6, 65, 66], etc. All abstraction techniques compute abstract models of the given concrete system by leaving out "irrelevant" details, thus model checking the abstract models is considerably simpler than directly applying model checking to the concrete system. For an abstraction technique to be effective, it is important to come up with the right kind of abstract models to preserve the relevant behavior for the property. Usually, the initial abstraction is too coarse. It needs to be successively refined to gradually add more behavior to determine the result of the verification. It is desirable to keep the abstract model as small as possible, while still being sufficient for the verification. The existing abstraction techniques do not consider refinement at all, or the refinement process is computationally expensive or ineffective. Therefore, the major challenge is to automate the refinement process to find the small and sufficient abstract models efficiently.

### 1.2 Scope of This Thesis

This thesis investigates new abstraction techniques for the efficient verification of large scale hardware designs. Two abstraction methods, the localization reduction and the predicate abstraction, have been enhanced to solve the following problems:

- 1. In localization reduction, abstract models are constructed by retaining certain parts of the concrete model. Thus the size of the abstract models can be large, which could make model checking even the abstract models computationally expensive.

- 2. In localization reduction, for hardware designs with thousands of registers, identifying a small set of registers to build the abstract model required for the verification of the given property is difficult. Also, existing techniques invalidate one abstract counterexample at a time for refinement.

- 3. Existing predicate abstraction techniques are suitable for the verification of infinite state systems. However, they are inefficient when applied to the verification of large scale hardware systems. In particular, the algorithm to build the abstract model, the algorithm to refine the abstract transition relation and the algorithm to compute new predicates are not effective for hardware verification.

- 4. Predicate abstraction may perform badly for control intensive systems, because simulating the control structure may require a large number of predicates.

- 5. Although a typical design flow starts at register transfer level (RTL), existing model checking engines and verification tools use the gate level representation of the design under verification. High level RTL designs are synthesized to lower gate level designs before a verification tool can read and encode them. High level design information, e.g. predicates in Verilog descriptions, can be crucial for the success of the verification.

- 6. Counterexample guided abstraction refinement may add redundant predicates that are not necessary for the verification of the given property.

This unnecessarily increases the size of the abstract model. There is no automatic way to identify and remove those redundant predicates.

The goal of this thesis is to address these problems. The principal contributions of this work are detailed below:

SAT conflict dependency analysis. Our abstraction refinement algorithms are based on SAT procedures. These algorithms rely on the identification of unsatisfiability proofs of SAT formulas. A technique, called SAT conflict dependency analysis, is developed to extract a small unsatisfiability proof of the given SAT formula. Using the unsatisfiability proof, a subformula of an unsatisfiable SAT formula can be shown to be unsatisfiable. Based on SAT conflict dependency analysis, an incremental SAT solver is built on top of the modern SAT solver zChaff [56], which can considerably speed up solving a set of related SAT problems whether they are satisfiable or not.

Localization reduction based on multiple verification engines. Localization reduction overapproximates the given concrete model by keeping

a set of important registers (visible registers) and hiding the rest (invisible registers). We enhance traditional localization reduction for the verification of hardware designs with thousands of registers. A hybrid BDD/ATPG algorithm is developed to compute efficiently abstract counterexamples for abstract models with large number of inputs. A 3-valued simulator and a SAT solver are used to identify a minimal set of registers that cause the given abstract counterexample to fail on the concrete model.

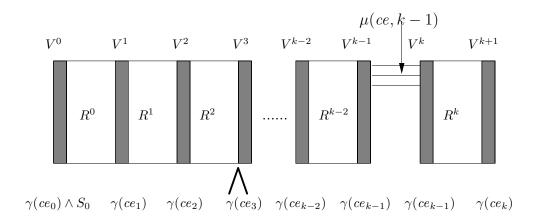

Localization reduction based on unsatisfiability proofs. A new localization reduction algorithm is developed, where the refinement only adds those invisible registers that appear in the unsatisfiability proof generated when the abstract counterexample is proved to be unsatisfiable on the concrete model. Furthermore, we propose two new algorithms to generalize counterexamples based localization reduction. The first algorithm generates better initial abstractions by the use of BMC and the unsatisfiability proofs of the corresponding SAT formulas. The second algorithm is used to invalidate multiple abstract counterexamples at once.

SAT based predicate abstraction for RTL Verilog design verification. The construction of an abstract model using predicate abstraction involves potentially exponential number of validity checks. Each of these checks requires one call to the SAT solver. We developed a pruning technique to reduce the number of calls to the SAT solver. To eliminate a spurious abstract counterexample, two efficient SAT based refinement algorithms are developed. The first algorithm requires only one call to the SAT solver, while the number of calls in the existing algorithm [28] is twice the number of predicates. Our second refinement algorithm computes new predicates that are compact, while the existing algorithm [65] does not consider the size of the new predicates. Furthermore, we developed a practical method to exploit high level information in predicate abstraction. This method extracts relevant branch conditions in RTL Verilog designs before verification starts. To use these branch conditions in predicate abstraction, a lazy refinement algorithm is developed. This algorithm identifies a subset of the branch conditions that can invalidate a spurious counterexample without constructing the full refined abstract model.

Combine localization reduction with predicate abstraction. For control variables that determine the behavior of the concrete system, the number of predicates required to simulate their behavior may be much larger than the number of control variables. We develope a clustering based heuristic to identify when such a blow up of the abstract model is likely to occur for predicate abstraction. Then a modified localization reduction algorithm is used to include these variables into the abstract model. Furthermore, it is usually the case that different predicates are not independent. Efficient algorithms are designed to compute constraints between predicates. The computed constraints are added as invariants to the abstract model to make it more accurate.

Removing redundant predicates. Existing predicate abstraction algorithms use counterexamples to guide the computation of new predicates. For

the verification of the given property, it is possible for the refinement algorithm to include unnecessary predicates, called redundant predicates. We have developed two criteria to identify when a predicate is redundant based on the concept of *replacement functions*. We also show how to remove the redundant predicates efficiently, once they are identified.

I believe that the novel ideas presented significantly advance the state of the art in hardware verification. We performed a large number of experiments on industrial benchmarks with thousands of registers and greatly improved upon the results of the existing verification techniques.

### 1.3 Related Work

In this section, we briefly review some of the related work.

### 1.3.1 SAT Unsatisfiability Proofs

Extracting unsatisfiability proofs is also studied by Zhang and Malik in [75] and by McMillan and Amla in [55]. Their approaches to extract unsatisfiability proofs are similar to the one presented in this thesis, except that they use resolution rather than the boolean constraint propagation method to represent the reasoning in a conflict graph.

In [75], experimental study is performed to measure the quality of the extracted proofs. For their examples, only 19% to 90% of the generated conflict clauses during SAT search are actually needed in the proofs. For an unsatisfiable CNF formula, they also show through experiments that the set of clauses in the unsatisfiability proof is not the minimal unsatisfiable subformula, con-

firming the claim in this thesis. Compared with our work, the extracted unsatisfiability proofs are used for different purposes. We use unsatisfiability proofs to perform counterexample guided abstraction refinement; while in [75], the unsatisfiability proofs are verified to check the correctness of the SAT solver. McMillan and Amla use unsatisfiability proofs to perform localization reduction without counterexamples. We will discuss their algorithm in the following subsection.

Incremental SAT is independently studied by Kim, Whittemore and Sakallah in [42]. They show how an incremental SAT solver can be used to solve a set of related SAT problems, where constraints are added in last-in-first-out order. Similar to our dependency analysis, their algorithm to enable the reuse of conflict clauses maintains the relationship between a conflict clause and the clauses that are responsible for it.

## 1.3.2 Localization Reduction and Counterexample Guided Refinement

In [43,64], Kurshan proposed the high-level strategy called localization reduction for the language containment problem between a system of L-processes and a specification of the system in terms of L-automata. The abstract models are subsets of the L-processes. Refinement is based on adding L-processes to invalidate the abstract counterexamples, which is guided by the dependency graph among L-processes. However, the description of the algorithm does not provide enough details to implement a practical tool.

Balarin et al. [5] reported a similar iterative algorithm for checking lan-

guage emptiness of networks of communicating automata. The abstract models are subsets of the communicating automata. Refinement is based on adding some extra communicating automata to the abstract model. The choice is based on the degree of common support between the current abstract model and the automata that have not been included in the abstract model. The verification result of a collection of dining philosophers using BDD-based image computation is reported.

Lu [48] developed a counterexample guided abstraction refinement framework. Lu was the first to propose refinement based on separation of deadend and bad states. Our refinement algorithm is also based on this concept. However, there are several differences. The biggest bottleneck in his method is the use of BDD based image computations on concrete systems for validating counterexamples. We use symbolic simulation based on SAT to accomplish this task. His method to separate deadend and bad states is based on splitting the variable domains, while our methods either hide irrelevant parts of the design or introduce new predicates.

In [22], Clarke et al. proposed localization reduction algorithms based on separation of deadend and bad states using integer linear programming (ILP) and machine learning techniques. They sample the deadend and bad states and produce optimal separating variables for the samples. This process is repeated till the separating variables are sufficient to separate deadend and bad states.

Subsequently, Chauhan et al. proposed a SAT conflict analysis based heuristic score algorithm for refinement in [18]. This algorithm analyzes the structure of SAT search to identify important registers. The algorithm is computationally inexpensive and does not need multiple SAT checks for refinement. We also introduced SAT conflict dependency analysis to extract unsatisfiability proofs in [18]. The set of registers identified by heuristic score method for refinement is usually larger than that identified by SAT unsatisfiability proof based methods.

In [55], McMillan and Amla proposes a new localization reduction algorithm that does not use abstract counterexamples to perform refinement. Instead, in each iteration of the abstraction refinement procedure, SAT based bounded model checking with increasing bounds is performed on the concrete model. If there is no concrete counterexample of a given length, the registers in the extracted unsatisfiability proofs are used to construct an abstract model. Then, BDD based model checking is used to verify the property on the abstract model. If the property is false on the abstract model, the above procedure is repeated. Their algorithm is similar to the proof based method to extract a set of important registers from bounded model checking presented in Section 4.4.4. However, there are important differences. We use the method based on BMC only to generate initial abstraction. Moreover, we are not required to use all the registers in the unsatisfiability proofs, since the proofs are not minimal and there could be too many registers in the proofs.

### 1.3.3 Predicate Abstraction

Predicate abstraction was introduced by Graf and Saidi in [65]. They used PVS theorem prover to perform on the fly Overapproximate reachability analysis of infinite state systems. In their approach, the abstract state space is represented as monomials over predicates. No abstract model is explicitly built. In [66], Saidi and Shankar introduced an algorithm to compute abstractions for infinite state systems that preserve all  $\mu$ -calculus formulas. Their algorithm does not introduce any approximations in the abstract model, however, it requires an exponential number of validity checks. They present a simplistic refinement process to remove the nondeterministic behaviors introduced by predicate abstraction.

An algorithm to make the abstract model more accurate given a fixed set of predicates is presented in [28]. To speed up the abstraction process, they introduce approximations in the abstract model. This results in spurious transitions in the abstract model. To remove a spurious transition, their algorithm requires 2m number of calls to a theorem prover, where m is the number of predicates. Our algorithm is more efficient in that no additional calls to a SAT solver are required. Note that, in general, their algorithm can come up with a more general constraint than ours. However, we can get the same constraints, probably using much less time, by combining both algorithms together. Furthermore, the work in [28] does not consider the problem of introducing new predicates to refine the abstract model.

Exploiting high level hardware description language features for abstraction has been investigated in [23]. They extract conditions of **case** statements in the SMV language in order to build the initial abstraction. The extraction method in [23] requires modifying the *source code* of an existing translator of SMV language. We transform the given Verilog design to an equivalent design where the predicates are uniquely named. The modified design can be processed by commercial synthesis tools to generate verification models

where the predicates are preserved. In [23], the extracted conditions are used only for the initial abstraction; while we use the predicates for both initial abstraction and refinement.

Lazy abstraction for the verification of C programs has been investigated in [38]. The goals of their algorithm and ours are different. In [38], the construction of the abstract model and abstract model checking are performed only from the state where the spurious abstract counterexample fails on the concrete system. While our lazy refinement algorithm builds the refined abstract model only to the point where the counterexample is invalidated.

Some researchers have considered combining unabstracted control variables (visible variables) with predicate abstraction [57], but their methods are not automatic. Using the correlations between all predicates to constrain the abstract model has been investigated in [6]. The correlations are computed using a general theorem prover. We first partition the set of predicates into clusters based on the sharing of support sets, then correlations are computed for each cluster separately. Although our result is more approximate, the complexity of our algorithm is much less sensitive to the total number of predicates. We also give a BDD-based algorithm to compute the correlations between predicates. We also given an algorithm to compute the correlations between unabstracted control variables and predicates. As far as we know, no one else has considered these kind of correlations before.

Similar to our algorithms for removing redundant predicates, in [6] a technique called *strengthening* is proposed. To build the abstract model, the weakest precondition is converted to an expression over the set of predicates in the abstraction. Thus, strengthening is somewhat similar to the concept

of replacement functions in this thesis. However, in [6], the result of the strengthening is over all the predicates, while the replacement functions used here are defined over a subset of the predicates. Finally, the two transformations have different purposes. Strengthening is only used to build an abstract model; while our transformation is used to remove redundant predicates and thus reduce the complexity of the abstract model.

### 1.3.4 Other Abstraction Techniques

Rather than building abstract models explicitly and relying on counterexamples to guide the refinement, Pardo and Hachtel [60] used BDD subsetting to perform on-the-fly abstraction and refinement. Based on the polarity of a CTL subformula, under or over approximation is used. In our experience, subsetting-based abstraction methods are very unpredictable and too drastic to prove properties. The scalability problem of BDD-based methods also makes finding real counterexamples on original designs with thousands of registers almost impossible.

In [35], Govindaraju and Dill proposed an abstraction refinement algorithm for verifying safety properties. The abstract models are collections of state machines that form an overlapping partition of the original design. Post-image and pre-image computation methods are used to prove the property or generate an abstract counterexample on the partitioned design. Refinement is based on enlarging individual state machines in the overlapping partition of the original design, guided by heuristics based on the Hamming distance. An experiment on the verification of a PCI chip with 429 latches is

16

reported. We believe that this method also suffers from the scalability issue of BDD-based methods, and it will have difficulties in handling big designs even when they are partitioned.

## Chapter 2

### Existential Abstraction

In this chapter we review the relevant theory of existential abstraction introduced by Clarke, Grumberg and Long in [21] and Loiseaux et al. in [46]. Using this theory we describe the predicate abstraction framework of Saidi and Shankar [66] and the localization reduction [43]. To handle spurious abstract counterexamples, the abstraction refinement framework is introduced.

### 2.1 Notation

Let  $V = \{v_1, v_2, \ldots, v_n\}$  be a set of variables, where each variable  $v_i$  has a domain  $D_{v_i}$ . Let c be a function which maps each variable  $v_i \in V$  to a value in its domain  $D_{v_i}$ . If  $V_1 \subseteq V$ , the projection of c over  $V_1$ , denoted by  $proj[V_1](c)$ , is a function defined over  $V_1$  that is consistent with c over  $V_1$ .

Let  $S_1$  and  $S_2$  be sets of states, and let f be a function mapping the powerset of  $S_1$  to the powerset of  $S_2$ , i.e.,  $f: 2^{S_1} \to 2^{S_2}$ . The dual of the function f is defined to be

2.1. Notation 18

$$\widetilde{f}(X) = \overline{f(\overline{X})},$$

where the overbar indicates complementation in the appropriate set of states.

Let  $\rho$  be a relation from  $S_1$  to  $S_2$ , and let A be a subset of  $S_2$ , then the function  $pre[\rho](A)$  gives the *preimage* of A under the relation  $\rho$ . Formally,

$$pre[\rho](A) = \{s_1 \in S_1 \mid \exists s_2 \in A. \ \rho(s_1, s_2)\}.$$

Similarly, let B be a subset of  $S_1$ , then the function  $post[\rho](B)$  gives the postimage of B under the relation  $\rho$ . More formally,

$$post[\rho](B) = \{s_2 \in S_2 \mid \exists s_1 \in B. \ \rho(s_1, s_2)\}$$

**Lemma 2.1.1** [46] If relation  $\rho$  is a total function on  $S_1$ , then  $\widetilde{pre}[\rho]$  is the same as  $pre[\rho]$

**Proof:** We prove it by showing that  $\forall S \in 2^{S_2} \ pre[\rho](S) = \widetilde{pre}[\rho](S) = \overline{pre}[\rho](\overline{S})$ . First, if  $x \in pre[\rho](S)$ , then there exists  $s \in S$  such that  $\rho(x,s)$  holds. Hence there does not exists  $y \in \overline{S}$  such that  $\rho(x,y)$  holds (since  $\rho$  is a function). Thus  $\neg(x \in pre[\rho](\overline{S}))$ . So  $x \in \overline{pre[\rho](\overline{S})}$ .

Next, suppose  $x \in \overline{pre[\rho](\overline{S})}$ , then  $\neg(x \in pre[\rho](\overline{S}))$ . Now  $\rho$  is total so  $\rho(x,s)$  holds for some s. Since  $\neg(x \in pre[\rho](\overline{S}))$ , it follows that  $\neg(s \in \overline{S})$ . Thus  $s \in S$  and  $x \in pre[\rho](S)$ .

We will be reasoning about a concrete state machine and an abstraction of that machine. To establ a relationship between the set of concrete states  $S_1$  and the set of abstract states  $S_2$  we will use the concept of a *Galois connection*.

**Definition 2.1.1** Let  $Id_S$  denotes the identity function on the powerset of S. A Galois connection between  $2^{S_1}$  and  $2^{S_2}$  is a pair of monotonic functions  $(\alpha, \gamma)$ , where  $\alpha: 2^{S_1} \to 2^{S_2}$  and  $\gamma: 2^{S_2} \to 2^{S_1}$ , such that  $Id_{S_1} \subseteq \gamma \circ \alpha$  and  $\alpha \circ \gamma \subseteq Id_{S_2}$ .

The following duality property of Galois connections is well known [46].

**Proposition 2.1.1** For any Galois connection  $(\alpha, \gamma)$  from  $2^{S_1}$  to  $2^{S_2}$ , we have,

- $\gamma(Y) = \bigcup \{X \in 2^{S_1} \mid \alpha(X) \subseteq Y\},\$

- $\alpha(X) = \bigcap \{Y \in 2^{S_2} \mid X \subseteq \gamma(Y)\}.$

Note that, given either one of  $\alpha$  or  $\gamma$ , the other is uniquely determined. Typically,  $\alpha$  and  $\gamma$  are used to define the relationship between the abstract and concrete models. The functions  $\alpha$  and  $\gamma$  are often called the *abstraction function* and the *concretization function*, respectively. The Galois connection that we will be using in this paper is described in the following proposition.

**Proposition 2.1.2** [46] Given a relation  $\rho \subseteq S_1 \times S_2$ , the pair  $(post[\rho], \widetilde{pre}[\rho])$  is a Galois connection between  $2^{S_1}$  and  $2^{S_2}$ .

We denote this Galois connection by  $(\alpha_{\rho}, \gamma_{\rho})$ . Sometimes, we write  $(\alpha, \gamma)$  when the relation  $\rho$  is clear from the context.

### 2.2 Existential Abstraction

We model circuits and programs as transition systems. Given a set of atomic propositions, A, let  $M = (S, S_0, R, L)$  be a transition system, where S is the

set of states,  $S_0 \subseteq S$  is a set of initial states,  $R \subseteq S \times S$  is a transition relation and  $L: S \to 2^A$  is the labeling function from the set S to the powerset of A. Often a state of a system will be described as an assignment of values to the set of state variables  $V = \{v_1, v_2, ..., v_m\}$ . In this case, R will be given as a formula over two copies of the state variables, one representing the *current state* and the other the *next state*. If the set of current state variables is  $V = \{v_1, v_2, ..., v_m\}$  then the set of next state variables is  $V' = \{v'_1, v'_2, ..., v'_m\}$ . Note that functions that are applicable to unprimed variables will be applicable to the corresponding primed versions too, the only difference is that the result will also be in terms of primed variables.

**Definition 2.2.1** Given two transition systems  $M = (S, S_0, R, L)$  and  $\hat{M} = (\hat{S}, \hat{S}_0, \hat{R}, \hat{L})$ , with atomic propositions A and  $\hat{A}$  respectively, a relation  $\rho \subseteq S \times \hat{S}$ , which is total on S, is a *simulation relation* between M and  $\hat{M}$  if and only if for all  $(s, \hat{s}) \in \rho$  the following conditions hold:

- $L(s) \cap \hat{A} = \hat{L}(\hat{s}) \cap A$

- For each state  $s_1$  such that  $(s, s_1) \in R$ , there exists a state  $\hat{s_1} \in \hat{S}$  with the property that  $(\hat{s}, \hat{s_1}) \in \hat{R}$  and  $(s_1, \hat{s_1}) \in \rho$ .

We say that  $\hat{M}$  simulates M through the simulation relation  $\rho$ , denoted by  $M \preceq_{\rho} \hat{M}$ , if for every initial state  $s_0$  in M there is an initial state  $\hat{s_0}$  in  $\hat{M}$  such that  $(s_0, \hat{s_0}) \in \rho$ . We say that  $\rho$  is a bisimulation relation between M and  $\hat{M}$  if  $M \preceq_{\rho} \hat{M}$  and  $\hat{M} \preceq_{\rho^{-1}} M$ . If there is a bisimulation relation between M and  $\hat{M}$  then we say that M and  $\hat{M}$  are bisimilar, and we denote this by  $M \equiv_{bis} \hat{M}$ .

Given a transition system M and a  $CTL^*$  formula f on the atomic propositions A associated with M, the satisfaction relation  $\models$  is defined in the standard fashion (see [24]). The following is a well-known theorem relating the formulas satisfied by two transitions systems where one simulates the other (see [21,24]).

### Theorem 2.2.1 (Preservation of ACTL\* [24])

Let  $M=(S,S_0,R,L)$  and  $\hat{M}=(\hat{S},\hat{S}_0,\hat{R},\hat{L})$  be two transition systems, with A and  $\hat{A}$  as the respective sets of atomic propositions and let  $\rho\subseteq S\times\hat{S}$  be a relation such that  $M\preceq_{\rho}\hat{M}$ . Then, for any ACTL\* formula  $\Phi$  with atomic propositions in  $A\cap\hat{A}$

$$\hat{M} \models \Phi \text{ implies } M \models \Phi.$$

### Theorem 2.2.2 (Preservation of CTL\* [24])

Let  $M = (S, S_0, R, L)$  and  $\hat{M} = (\hat{S}, \hat{S}_0, \hat{R}, \hat{L})$  be two transition systems, with A and  $\hat{A}$  as the respective sets of atomic propositions and let  $\rho \subseteq S \times \hat{S}$  be a bisimulation relation between M and  $\hat{M}$ . Then, for any CTL\* formula  $\Phi$  with atomic propositions in  $A \cap \hat{A}$

$$\hat{M} \models \Phi \Leftrightarrow M \models \Phi.$$

The reader is referred to [46] and [21] for details of the proof. The former paper uses a different notation.

Let  $M = (S, S_0, R, L)$  be a concrete transition system over a set of atomic propositions A. Let  $\hat{S}$  be a set of abstract states and  $\rho \subseteq S \times \hat{S}$  be a total function on S. Further, let  $\rho$  and L be such that for any  $\hat{s} \in \hat{S}$ , all states in  $pre[\rho](\hat{s})$  have the same labeling over a subset  $\hat{A}$  of A. Then an abstract transition system  $\hat{M} = (\hat{S}, \hat{S}_0, \hat{R}, \hat{L})$  over  $\hat{A}$  which simulates M can be constructed as follows:

$$\hat{S}_0 = post[\rho](S_0) = \exists s. \ S_0(s) \land \rho(s, \hat{s})$$

$$(2.1)$$

$$\hat{R}(\hat{s}, \hat{s}') = \exists s \ s'. \ \rho(s, \hat{s}) \land \rho(s', \hat{s}') \land R(s, s')$$

$$(2.2)$$

for each

$$\hat{s} \in \hat{S}$$

,  $\hat{L}(\hat{s}) = \bigcap_{s \in pre[\rho](\hat{s})} (L(s) \cap \hat{A})$  (2.3)

### **Proposition 2.2.1** For M and $\hat{M}$ in the above construction $M \leq_{\rho} \hat{M}$

In the above construction  $\hat{R}$  is defined in terms of the abstract current state  $\hat{s}$  and the abstract next state  $\hat{s}'$ . This construction is from [21], and it is also implicit in the paper by Loiseaux et al. [46]. The idea behind the transition system is as follows: two abstract states are related if there exist two concrete states that they are related to each other under the concrete relation and map to the abstract states under  $\rho$ . This kind of abstraction is called existential abstraction. The set of initial states in the abstract system are those states of  $\hat{S}$  that are related to the initial states of M. Note that for any two states s and  $\hat{s}$  related under  $\rho$  the property  $L(s) \cap \hat{A} = \hat{L}(\hat{s})$  holds.

### 2.3 Predicate Abstraction

Predicate abstraction [6, 7, 28, 29, 38, 57, 65, 66], can be viewed as a special case of existential abstraction. In predicate abstraction a set of predicates  $\{P_1, \ldots, P_k\}$ , including those in the property to be verified, are identified from the concrete program. These predicates are defined on the variables of

the concrete system. They also serve as the atomic propositions that label the states in the concrete and abstract transition systems. That is, the set of atomic propositions is  $A = \{P_1, P_2, ..., P_k\}$ . A state in the concrete system will be labeled with all the predicates it satisfies. The abstract state space has a boolean variable  $B_j$  corresponding to each predicate  $P_j$ . So each abstract state is a valuation of these k boolean variables. An abstract state will be labeled with predicate  $P_j$  if the corresponding bit  $B_j$  is 1 in that state. The predicates are also used to define a total function  $\rho$  between the concrete and abstract state spaces. A concrete state s will be related to an abstract state s through s if and only if the truth value of each predicate on s equals the value of the corresponding boolean variable in the abstract state s. Formally,

$$\rho(s,\hat{s}) = \bigwedge_{1 \le j \le k} P_j(s) \Leftrightarrow B_j(\hat{s})$$

(2.4)

Note that  $\rho$  is a total function because each  $P_j$  can have one and only one value on a given concrete state and so the abstract state corresponding to the concrete state is unique. Based on Section 2.1, the pair of functions  $post[\rho]$  and  $\widetilde{pre}[\rho]$  generated from relation  $\rho$  forms a Galois connection. We will denote this Galois connection by  $(\alpha, \gamma)$ . Note that since  $\rho$  is a total function,  $\widetilde{pre}[\rho] = pre[\rho]$ . The following lemma establishes that the set of concrete states corresponding to a set of abstract states can be computed by simply substituting predicates for the bits in the formula representing the abstract states. In the following,  $\hat{Y}[B_i \leftarrow P_i]$  denotes the formula obtained by substituting each boolean variable  $B_i$  by the corresponding predicate  $P_i$ .

**Lemma 2.3.1** Let  $\rho$  be an abstraction function. For a set of abstract states

$$\hat{Y}, \gamma_{\rho}(\hat{Y}) = \hat{Y}[B_i \leftarrow P_i]$$

#### **Proof:**

$$\begin{array}{ll} \gamma_{\rho}(\hat{Y}) \\ = & pre[\rho](\hat{Y}) \\ = & \exists \hat{s}. \; \hat{Y}(\hat{s}) \land \rho(s,\hat{s}) \\ = & \exists \hat{s}. \; \hat{Y}(\hat{s}) \land \rho(s,\hat{s}) \\ = & \exists \hat{s}. \; \hat{Y}(\hat{s}) \land \bigwedge_{1 \leq i \leq k} P_i(s) \Leftrightarrow B_i(\hat{s}) \\ = & \hat{Y}[B_i \leftarrow P_i] \end{array} \qquad \begin{array}{ll} since \; \widetilde{pre}[\rho] = pre[\rho] \\ definition \; of \; pre[\rho] \\ definition \; of \; \rho \\ definition \; of \; substitution \end{array}$$

Using this  $\rho$  and the construction given in Section 2.2, we can build an abstract model which simulates the concrete model. Since  $(\alpha_{\rho}, \gamma_{\rho})$  is a Galois connection, for any concrete state X,  $\alpha_{\rho}(X) = \bigwedge \{\hat{f} \mid X \to \gamma_{\rho}(\hat{f})\}$ , where  $\hat{f}$  is an arbitrary formula over the abstract state variables. According to [66], it is enough to only consider all disjunctions over the abstract state variables in calculating abstractions. Thus the set of abstract initial states for predicate abstraction is:

$$\hat{S}_0 = \bigwedge \{ \hat{Y}_1 \mid \forall V. (S_0 \Rightarrow \gamma(\hat{Y}_1)) \}$$

(2.5)

In equation (2.5),  $\hat{Y}_1$  is an arbitrary disjunction of the literals of the current state variables  $\{B_1, B_2, \dots, B_k\}$ . In [66] the abstract transition relation  $\hat{R}$  is defined as

$$\bigwedge \{ \hat{Y} \to \hat{Y}' \mid \forall V, \ V'.(R(V, V') \Rightarrow \gamma(\hat{Y} \to \hat{Y}')) \}$$

(2.6)

In equation (2.6),  $\hat{Y}$  is an arbitrary conjunction of the literals of the current state variables  $\{B_1, B_2, \ldots, B_k\}$  and  $\hat{Y}'$  is an arbitrary disjunction of literals of the next state variables  $\{B'_1, B'_2, \ldots, B'_k\}$ . In the above two equations, V is the set of concrete current state variables and V' is the set of concrete next state variables. The set of concrete initial states  $S_0$  is represented by its characteristic function over V. Similarly, the concrete transition relation R is represented by its characteristic function over  $V \cup V'$ . Note that  $\gamma(\hat{Y}_1)$  can be represented by a formula over V, and  $\gamma(\hat{Y} \to \hat{Y}')$  can be represented by a formula over  $V \cup V'$ . Thus the implications in the equations (2.5) and (2.6) are well formed. It is easy to see that both the set of abstract initial states and the abstract transition relation in the above equations are the most accurate overapproximation of the set of concrete initial states and concrete transition relations respectively. We will show that (2.6) is equivalent to (2.2).

**Theorem 2.3.1** Let R be a concrete transition relation,  $\rho$  be a simulation relation as in (2.4), then

$$\exists s \ s'. \ \rho(s,\hat{s}) \land \rho(s',\hat{s}') \land R(s,s') =$$

$$\bigwedge \{ \hat{Y} \to \hat{Y}' \mid (\forall V, \ V'.(R(V,V') \land \gamma(\hat{Y})) \to \gamma(\hat{Y}')) \}$$

where  $\hat{Y}$  is a conjunction over  $\{B_1, \ldots, B_k\}$  and  $\hat{Y}'$  is a disjunction over  $\{B'_1, \ldots, B'_k\}$ .

**Proof:** First we prove that if two states are related under

$$R_1 = \exists s \ s'. \ \rho(s,\hat{s}) \land \rho(s',\hat{s}') \land R(s,s')$$

then they are related under  $R_2 = \bigwedge \{\hat{Y} \to \hat{Y}' \mid \forall V, \ V'.((R(V,V') \land \gamma(\hat{Y})) \to \gamma(\hat{Y}'))\}$ . Suppose  $R_1(\hat{s},\hat{s}')$  and let the corresponding concrete states be s and s'. So  $\rho(s,\hat{s})$  and  $\rho(s',\hat{s}')$  hold. To prove that  $\hat{s}$  and  $\hat{s}'$  satisfy  $R_2$ , we need to show that every implication of the form  $\hat{Y} \to \hat{Y}'$ , which satisfies  $(R \land \gamma(\hat{Y})) \to \gamma(\hat{Y}')$ , is true for  $\hat{s},\hat{s}'$ . Suppose  $\hat{Y}(\hat{s})$  is false, then the implication  $\hat{Y} \to \hat{Y}'$  is automatically true for  $(\hat{s},\hat{s}')$ . Consider the case where  $\hat{Y}(\hat{s})$  is true. We know that state s satisfies  $\rho(s,\hat{s})$  and since  $\gamma = pre[\rho]$ , thus  $s \in \gamma(\hat{Y})$ . Now since  $(R \land \gamma(\hat{Y})) \to \gamma(\hat{Y}')$ ,  $s \in \gamma(\hat{Y})$  and R(s,s'), we also have  $s' \in \gamma(\hat{Y}')$ . Now we show that  $\hat{s}' \in \hat{Y}'$ .

$$\begin{array}{ll} s' \in \gamma(\hat{Y}') & \text{just proved} \\ \alpha(s') \subseteq \alpha(\gamma(\hat{Y}')) & \text{monotonicity of } \alpha \\ \alpha(\gamma(\hat{Y}')) \subseteq \hat{Y}' & \alpha \circ \gamma \subseteq Id_{\hat{S}} \\ \hat{s}' \in \alpha(s') & \alpha(s') = post[\rho](s') \text{ and } \rho(s', \hat{s}') \\ \hat{s}' \in \hat{Y}' & \text{by the above results.} \end{array}$$

Therefore, we have shown that every implication  $\hat{Y} \to \hat{Y}'$ , which satisfies  $(R \wedge \gamma(\hat{Y})) \to \gamma(\hat{Y}')$ , is true for any pair of states  $(\hat{s}, \hat{s}')$  related under  $R_1$ .

For the other direction, we need to prove that if two states are related through  $R_2$  then they are related under  $R_1$ . Equivalently, we can prove that if two states are not related under  $R_1$  then they cannot be related under  $R_2$  either. Consider two states  $\hat{s}$  and  $\hat{s}'$  which are not related under  $R_1$ . We will show that there exists an implication  $\hat{Y} \to \hat{Y}'$  that satisfies  $(R \wedge \gamma(\hat{Y})) \to \gamma(\hat{Y}')$  and is false for the pair  $(\hat{s}, \hat{s}')$ . We define two formulas

$C_{\hat{s}}$  and  $C'_{\hat{s}'}$  as follows.

$$C_{\hat{s}} = \bigwedge \{ B_i \mid \hat{s}(B_i) = 1 \} \land \bigwedge \{ \neg B_i \mid \hat{s}(B_i) = 0 \}$$

$$C'_{\hat{s}'} = \bigwedge \{ B'_i \mid \hat{s}'(B'_i) = 1 \} \land \bigwedge \{ \neg B'_i \mid \hat{s}'(B'_i) = 0 \}$$

We will show that  $C_{\hat{s}} \to \neg C'_{\hat{s}'}$  is the required implication. Clearly, the implication  $C_{\hat{s}} \to \neg C'_{\hat{s}'}$  is false for the pair  $(\hat{s}, \hat{s}')$  because by definition  $C_{\hat{s}}(\hat{s})$  is true and  $\neg C'_{\hat{s}'}(\hat{s}')$  is false. To complete the proof we just need to show that  $(R \wedge \gamma(C_{\hat{s}})) \to \gamma(\neg C'_{\hat{s}'})$  is true. We first show that  $\rho(s, \hat{s}) \Leftrightarrow s \in \gamma(C_{\hat{s}})$ .

$$\rho(s,\hat{s}) \Leftrightarrow s \in pre[\rho](\hat{s})$$

$$\Leftrightarrow s \in \gamma(\hat{s}) \quad (\text{ since } \gamma = pre[\rho] )$$

$$\Leftrightarrow s \in \gamma(C_{\hat{s}}) \quad (\text{ since } C_{\hat{s}} = \{\hat{s}\} ).$$

Next we show that  $\neg \rho(s', \hat{s}') \Leftrightarrow s' \in \gamma(\neg C'_{\hat{s}'})$ .

$$\neg \rho(s', \hat{s}') \Leftrightarrow s' \not\in pre[\rho](\hat{s}')$$

$$\Leftrightarrow s' \not\in \widetilde{pre}[\rho](\hat{s}') \text{ (since } \rho \text{ is a total function)}$$

$$\Leftrightarrow s' \in pre[\rho](\overline{\hat{s}'})$$

$$\Leftrightarrow s' \in \gamma(\overline{\hat{s}'})$$

$$\Leftrightarrow s' \in \gamma(\neg C'_{\hat{s}'}).$$

Finally,

$$(\hat{s}, \hat{s}') \notin R_1$$

$$\Leftrightarrow \forall s, s'. \ \neg(\rho(s, \hat{s}) \land \rho(s', \hat{s}') \land \ R(s, s'))$$

$$\Leftrightarrow \forall s, s'. \ (R(s, s') \land \rho(s, \hat{s})) \Rightarrow \neg \rho(s', \hat{s}')$$

$$\Leftrightarrow \forall s, s'. \ (R(s, s') \land \gamma(C_{\hat{s}})(s)) \Rightarrow \gamma(\neg C'_{\hat{s}'})(s')$$

Thus  $(\hat{s}, \hat{s}') \notin R_2$ . which is the required result.

There are several reasons to prefer (2.6) over (2.2) for computing the abstract transition relation. Traditionally (2.2) is computed using BDDs, but this method is not feasible for the large systems considered in this work. Alternatively, we could formulate (2.2) as a SAT problem. Computing the abstract transition relation would then require enumerating all possible satisfying assignments to the SAT formula. Furthermore, it is not easy to get an over-approximation using the SAT formulation of (2.2). However, in formula (2.6), an implication of the form  $\hat{Y} \to \hat{Y}'$  is included in  $\hat{R}$  if and only if  $R \wedge \gamma(\hat{Y}) \wedge \neg \gamma(\hat{Y}')$  is unsatisfiable. Checking unsatisfiability is much easier than enumerating all the satisfying assignments. Moreover, an overapproximation can be easily obtained using this method by restricting the choice of  $\hat{Y} \to \hat{Y}'$  to be considered [66].

Equations (2.5) and (2.6) can be used to compute abstract models for both hardware and software verification. To determine the validity of the proof obligations involved, a general theorem prover, such as Simplify [58], is used. Since variables in hardware designs are usually bit-vectors with small length and the predicates involved in hardware verification are propositional formulas, using a SAT solver, such as zChaff, can be more efficient for hardware verification.

The abstract model built according to equations (2.5) and (2.6) is called the most accurate abstract model. Note that, in this abstract model, every abstract initial state has at least one corresponding concrete initial state, and every abstract transition has at least one corresponding concrete transition. However, to build the most accurate abstract model, there are exponential number (in the number of predicates) of implications that need to be checked in worst case. To reduce the abstraction time, in practice an approximate abstract model is constructed by intentionally excluding certain implications from consideration. Therefore, there are more behaviors in the approximate model than in the most accurate abstract model. We call the abstract transitions that do not have any corresponding concrete transitions spurious transitions (Precise definitions are given in Chapter 5). Since an approximate abstract model contains all the behaviors of the original concrete system, the preservation theorem still holds. In this thesis, to reduce the abstraction time, we restrict  $\hat{Y}_1$  and  $\hat{Y}'$  to be at most one literal, and restrict  $\hat{Y}$  to include at most two literals. The model so obtained will be an over-approximation of the abstract model. We rely on refinement to compute a precise enough abstract model when necessary.

## 2.3.1 A Software Example

In this subsection, we will illustrate how an abstract program can be generated for a given concrete C program and a set of predicates using the

framework presented in [6]. Let  $\{P_1, \ldots, P_k\}$  denote the given set of concrete predicates. For each predicate  $P_i$ , let  $B_i$  be the corresponding boolean variable in the abstract program. Let  $B = \{B_1, \ldots, B_k\}$ . A cube c in the abstract program is a conjunction  $c_1 \wedge \cdots \wedge c_m$ , where each literal  $c_j \in \{B_j, \neg B_j\}$  for some  $B_j \in B$ . The concretization of a cube c, denoted  $\gamma(c)$ , is the conjunction of the concretization of each literal in c. For a statement s and a formula  $\phi$  over the concrete state variables, the weakest precondition, denoted  $\mathcal{WP}(s,\phi)$ , is the weakest predicate whose truth before s entails the truth of s after s terminates. Let s denote the largest disjunction of cubes s over s such that s denote s denote the largest disjunction of cubes s over s such that s denote the function s denoted the

$$\mathcal{H}(e, f) = \begin{cases} & \text{true} & \text{if } e \\ & \text{false} & \text{if } f \end{cases}$$

$$\{\text{true, false}\} & \text{otherwise}$$

To abstract a C program, each line of code is abstracted separately. For each literal over B, the weakest precondition is first calculated, then an expression over B is calculated using  $\mathcal{F}_B$  for the weakest precondition. This is illustrated by the following example from [8].

**Example 2.3.1** Let  $P = \{(x == 1), (x == 2), (x \leq 3)\}$  and let  $B = \{B_1, B_2, B_3\}$  be the three corresponding boolean variables. Consider the assignment statement x := x + 1. The following table shows the calculation of weakest precondition and the strengthening using the predicates. Based on

|                                                 | e = (x == 1)                 | e = (x == 2)                      | $e = (x \le 3)$ |

|-------------------------------------------------|------------------------------|-----------------------------------|-----------------|

| $\mathcal{WP}(x := x + 1, e)$                   | x == 0                       | x == 1                            | $x \le 2$       |

| $\mathcal{F}(\mathcal{WP}(x := x + 1, e))$      | false                        | $B_1$                             | $B_1 \vee B_2$  |

| $\mathcal{WP}(x := x + 1, \neg e)$              | $x \neq 0$                   | $x \neq 1$                        | $x \ge 3$       |

| $\mathcal{F}(\mathcal{WP}(x := x + 1, \neg e))$ | $B_1 \vee B_2 \vee \neg B_3$ | $\neg B_1 \lor B_2 \lor \neg B_3$ | $\neg B_3$      |

Table 2.1: Predicate abstraction for a C program

this table, the following abstract program is constructed.

$B_1 := \mathcal{H}(\text{false}, B_1 \vee B_2 \vee \neg B_3)$

$B_2$  :=  $\mathcal{H}(B_1, \neg B_1 \lor B_2 \lor \neg B_3)$

$B_3 := \mathcal{H}(B_1 \vee B_2, \neg B_3)$

#### 2.3.2 A Hardware Example

In this subsection, we present a hardware example and show how it can be verified based on the framework in [66]. Note that, this example is only used to illustrate the traditional predicate abstraction techniques. It does not represent the kind of hardware systems and properties that this thesis is focused on. In fact, we are more interested in verifying the control logic of hardware designs rather than the memory read address calculation described in this example.

This example is a simplified version of the fetch unit of a jpeg encoder implemented using Xilinx FPGAs [45]. This fetch unit is responsible to read each 8 pixels by 8 pixels of grey scale image data and pass it for further processing until the whole image is read (Figure 2.1). The image data is stored in an external memory, where each pixel is represented by one byte. The image data is stored line by line. The fetch unit begins by first reading

the width and height of the input grey-scaled image. Noted that the width and height are both multiples of 8. Then starting from memory address 0, 8 pixels by 8 pixels of image data is fetched according to the order following the arrows in Figure 2.1. Essentially the fetch unit has reordered the image data. Given a 8 pixels by 8 pixels image block, the *top-left* pixel is the first

Figure 2.1: Fetch each 8x8 pixel block

pixel of this block. For any pixel in this block, the *left-most* pixel is the first pixel in the same row. Given two adjacent 8x8 image blocks, where the second block is to the right of the first one, the second block is the *next-right block* of the first one. Following is the Verilog implementation. Input signals *WIDTH* and *HEIGHT* are the width and height of the image. We assume they are parameters to the design that do not change. Output signal *addr* is the memory read address. Since the property for this example only concerns the memory read address calculation, the read and write operations of the

image data are omitted. Signals *cwidth* and *cheight* are the width and height of the top-left pixel of the current 8x8 block. Signal *row* is the row number within the current 8x8 block. Signal *rowaddr* is the address of the top-left pixel in the next-right block.

```

module fetch(clk, reset, addr, WIDTH, HEIGHT);

input

clk, reset;

output [15:0]

addr;

input [7:0]

WIDTH;

input [7:0]

HEIGHT;

reg [15:0]

addr;

reg [7:0]

cwidth;

reg [7:0]

cheight;

reg [2:0]

row;

reg [15:0]

rowaddr;

always @(posedge clk or posedge reset) begin

if (reset) begin

\operatorname{cwidth} \leq 0;

cheight \leq 0;

row \leq 0;

addr \le 0;

rowaddr \leq 0;

end else begin

if (addr[2:0] < 3'h7)

addr \le addr + 1;

else begin

if (row == 3'h0)

rowaddr \le addr + 1;

if (row < 3'h7) begin

row \le row + 1;

addr \le (addr \& 16'hfff8) + WIDTH;

end else begin

row \leq 0;

if (cwidth + 8 < WIDTH) begin

\operatorname{cwidth} \leq \operatorname{cwidth} + 8;

```

```

addr \le rowaddr;

end else begin

addr \le addr + 1;

\operatorname{cwidth} \leq 0;

if (cheight + 8 < \text{HEIGHT})

cheight \leq cheight + 8;

else begin

cheight \leq 0;

addr \le 0:

row \leq 0;

end

end

end

end

end

end

endmodule

```

The property to be verified is that the read memory address is always smaller than the multiplication of the image width and height. To verify this property using predicate abstraction, the following signals and predicates are identified manually:

- Signal row[2:0]. It represents the row number of the current pixel within its 8x8 block.

- Signal addr[2:0]. It is the lowest 3 bits of the signal addr. It represents the column number of the current pixel within its 8x8 block.

- Predicate "addr & 16'hfff8 = (cheight+row) \* WIDTH + cwidth". It is an invariant, which says that the address of the left-most pixel is the addition of (row \* WIDTH) and the address of the top-left pixel which is (cheight \* WIDTH + cwidth).

- Predicate "rowaddr = cheight \* WIDTH + cwidth + 8". It is not an invariant, which is only true when (row >= 1). The predicate says that, the address of the top-left pixel in the next-right 8x8 block (If one exists), is 8 more than the address of the top-left pixel of the current 8x8 block. Because signal rowaddr does not get the correct value until the end of the first row, so until then, this predicate is false in the design.

- Predicates "cwidth + 8 < WIDTH" and "cheight + 8 < HEIGHT".</li>

These two predicates are branch conditions in the program.

- Predicate "addr < WIDTH \* HEIGHT". It is the property to be proven.

- Besides the above predicates, we assume the following invariants in building the abstract model. The correctness of this assumption can be checked easily by a syntactic analysis of the given Verilog code.

- 8 divides cwidth

- 8 divides cheight

- cwidth < WIDTH

- cheight < HEIGHT

Note that, signals row[2:0] and addr[2:0] are retained in the abstraction, so that their initial states and transition relations are copied from the concrete model. The algorithms presented in [66] works for guarded command languages. It is easy to translate the above Verilog code into a guarded command language based program. The corresponding abstract model expressed in SMV language is shown below:

#### MODULE main

```

VAR

```

```

row : 0..7;

addr2_0 : 0..7;

p_addr : boolean; -addr & 16'hfff8 = (cheight+row) * WIDTH + cwidth

p_rowaddr : boolean; -rowaddr = cheight * WIDTH + cwidth + 8

p_cwidth2 : boolean; -cwidth + 8 < WIDTH

p_cheight2 : boolean; -cheight + 8 < HEIGHT

prop : boolean; -addr < WIDTH * HEIGHT

```

#### ASSIGN

init(row)

:= 0;

```

1: \{0,1\};

esac;

next(addr2\_0)

case

addr2_0 < 7: addr2_0 + 1;

row < 7: 0;

p_cwidth2:

case p_rowaddr: 1; 1: \{0,1,2,3,4,5,6,7\}; esac;

1: 0;

esac;

next(p\_addr)

:=

case

addr2_0 < 7: case p_addr: 1; 1: \{0,1\}; esac;

row < 7: case p_addr: 1; 1: \{0,1\}; esac;

p_{\text{width2}}: case p_{\text{rowaddr}}: 1; 1: \{0,1\}; esac;

p_cheight2: case p_addr: 1; 1:{0,1}; esac;

1: 1;

esac;

next(row)

::=

case

addr2_0<7: row;

```

```

row < 7: row + 1;

1: 0;

esac;

next(p\_cwidth2) ::=

case

addr2_0<7 | row<7: p_cwidth2;

p_cwidth2: \{0,1\};

1: 1;

esac;

next(p_cheight2) ::=

case

addr2_0<7 | row<7 | p_cwidth2: p_cheight2;

p_cheight2: {0,1};

1: 1;

esac;

next(prop)

::=

case

addr2_0<7: case prop: 1; 1: {0,1}; esac;

row < 7: case p_addr: 1; 1: \{0,1\}; esac; -p_addr, cwidth<WIDTH, cheight<HEIGHT,

- 8 divides HEIGHT, 8 divides cheight

p_c width 2: case p_r rowaddr: 1; 1: \{0,1\}; esac;

```

```

p_cheight2: case p_addr: 1; 1: \{0,1\}; esac; 1: 1; esac;

```

SPEC AG (prop)

We have verified that this abstract model satisfies the required property, thus the concrete Verilog program satisfies the same property.

#### 2.4 Localization Reduction

Localization reduction [43] is also a special case of existential abstraction. In localization reduction, a set of important state variables, called *visible* variables, are retained in the abstract model; while the rest, called *invisible* variables, are left unconstrained (Their values are assigned nondeterministically). The abstract transition is obtained by conjuncting the transition relations for the visible variables. Formally, let V be the set of concrete state variables, and S be the concrete state space. For each state  $s \in S$ , the value of a variable  $v \in V$  in state  $s \in S$  is denoted by s(v). In localization reduction, given a set of visible variables  $V_1 \subseteq V$ , the abstract state variables  $v \in V$  in state  $v \in V$  in the set of abstract states for localization reduction is  $v \in V \cap V \cap V$ . The set of abstract states for localization reduction is  $v \in V \cap V \cap V \cap V$ . The simulation relation is  $v \in V \cap V \cap V \cap V$ . The set of related concrete states is  $v \in V \cap V \cap V \cap V \cap V \cap V$ . The set of related concrete states is  $v \in V \cap V \cap V \cap V \cap V \cap V$ .

We also assume that neither the concrete transition relation nor the set of initial states is described as a single formula. Instead, for each individual variable  $v \in V$ , the transition relation of v is represented as a propositional formula  $R_v$  and the set of initial states of v is represented as a propositional formula  $I_v$ . The most accurate abstract model for localization reduction can be easily built. That is, the abstract initial states  $\hat{S}_0$  and the abstract transition relation  $\hat{R}$  are defined as

$$\hat{S}_0 = \wedge_{v \in U} I_v \tag{2.7}$$

$$\hat{R} = \wedge_{v \in U} R_v \tag{2.8}$$

It is usually the case that  $\hat{R}$  depends not only on current and next state variables on U, but also some invisible variables which occur in some  $R_v$  or  $I_v$ . In the abstract model, these invisible variables are treated as primary inputs. In general, the size of the abstract transition relation may be large since it is directly copied from the concrete model. In Section 4, we will show techniques to reduce the size of the abstract model using approximation.

## 2.5 Abstraction Refinement

Existential abstraction is a conservative approach for model checking universal temporal logic [24] properties (we only consider safety properties in this thesis). That is, the correctness of any universal formula on an abstract system automatically implies the correctness of the formula on the concrete system. However, a counterexample on an abstract system may not correspond to any real path, in which case it is called a *spurious* counterexample [23]. To get rid of a spurious counterexample, the abstraction needs

refinement [23,38,72] (CEGAR) automates this procedure. It works as follows: For a given system, an abstract model that is guaranteed to include all behaviors of the original system is built. Model checking is then applied to the abstract model. If the property holds, it is true of the concrete model and verification terminates. In case the property is violated on the abstract model a counterexample is generated. This abstract counterexample is checked against the concrete model. If the abstract counterexample corresponds to a concrete execution path, the property is proved to be false and verification terminates. Otherwise, the abstract counterexample is spurious and it is used to guide the refinement of the abstract model. The above procedure repeats until the property is confirmed or refuted. Figure 2.2 shows the fours steps in the above abstraction refinement framework.

Figure 2.2: General Abstraction Refinement framework

# Chapter 3

# SAT and Unsatisfiability Proofs

In this chapter, we first briefly review Davis-Putnam-Logeman-Loveland (DPLL) backtracking SAT algorithms with conflict learning. Then, an unsatisfiability proof extraction algorithm is presented. Based this algorithm, we explain how to implement an incremental SAT solver.

# 3.1 Conflict based Learning in SAT Solvers

In this section, we briefly describe the learning mechanism used by modern SAT solvers, such as GRASP [68], Chaff [56,76] and BerkMin [31]. These SAT solvers are based on the Davis-Putnam-Logeman-Loveland (DPLL) backtracking SAT algorithm.