### Algorithms for Parallel Cache Hierarchies

#### Guy Blelloch Carnegie Mellon University

#### **Memory Hierarchies**

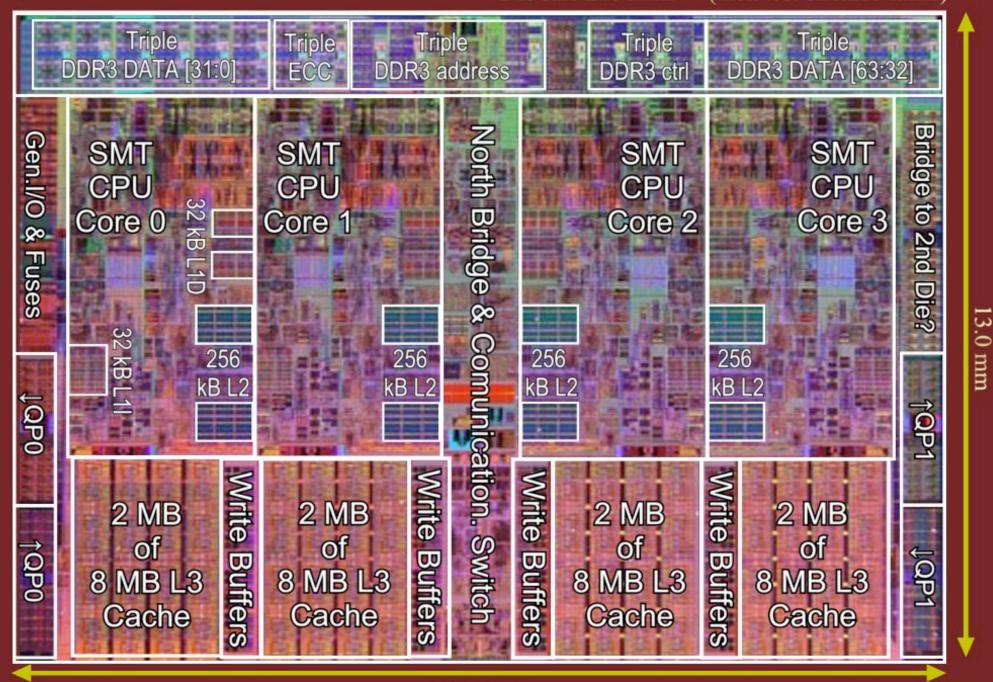

Die size 246 mm2 (incl. test circ.265 mm2)

18.9 mm

####

L2 cache tiles: 7.5 mm2 / MB,

L3 cache tiles: 7.5 mm2 / MB (excl.tags)

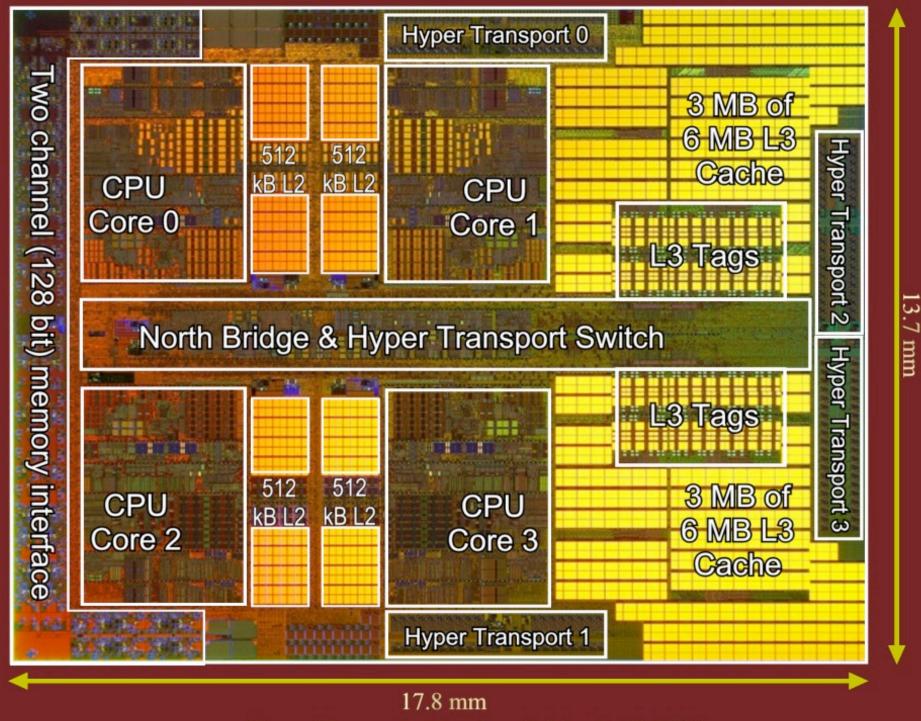

Die size 243 mm2 (incl. test circ.263 mm2)

www.chip-architect.com --- Rev.2 March-17, 2008

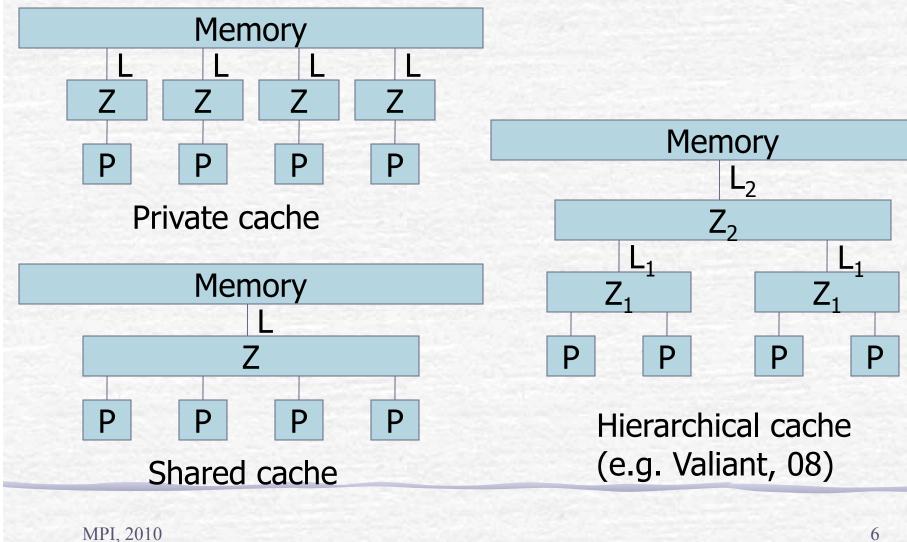

#### What about in Parallel

6

### Observation

- Many "parallel" algorithms have natural "sequential" locality

- Can we take advantage of this on a parallel machine. In particular can we describe/ program/analyze such algorithms in a highlevel way, but still understand performance on various cache architectures.

### Sequential Locality

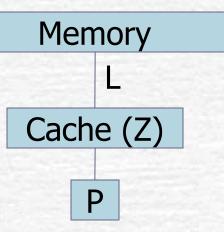

Assume unbounded memory and an ideal cache with a capacity of Z words and cache-lines of L words each.

Q(C; Z, L) – number of cache misses

An algorithm is

<u>cache-oblivious</u> if it does not use these parameters (Z and L)

#### Quicksort

```

function quicksort(S) =

if (#S <= 1) then S

else let

a = S[rand(#S)];

S1 = {e in S | e < a};

S2 = {e in S | e = a};

S3 = {e in S | e > a};

R = {quicksort(v) : v in [S1, S3]};

in R[0] ++ S2 ++ R[1];

```

Cache Oblivious with:  $Q(n;Z,L) = O(n/L \log n/Z)$  w.h.p {} indicates parallelism

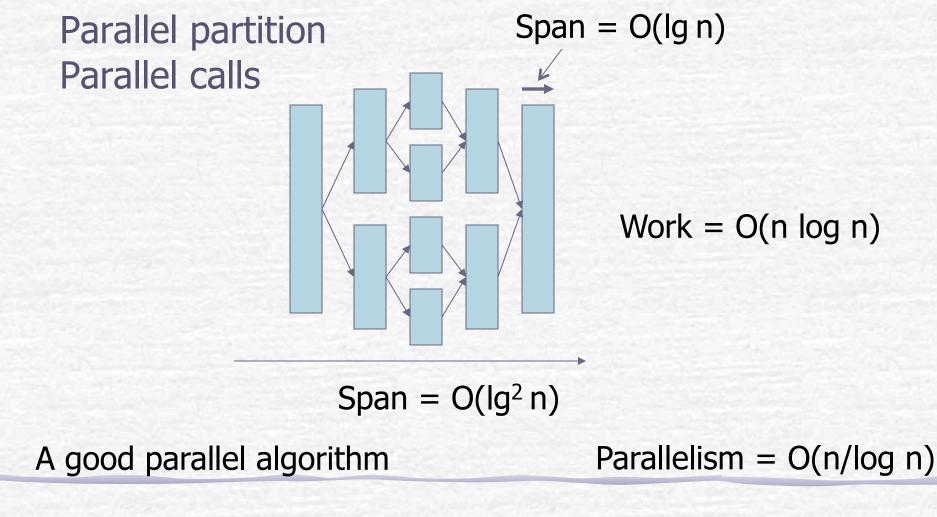

# Nested parallelism

Standard programming model with fork-join parallelism and no synchronization among tasks. No notion of processors (processor oblivious). Cost calculated using: • Work (W) : sum over parallel calls • Span (D) : take maximum over parallel calls ID, NESL, Cilk++, X10, Open MP, Microsoft TPL Typically much more parallelism than processors Lots of flexibility for scheduler

#### **Qsort Complexity**

#### **Greedy Schedules**

<u>Greedy schedule</u>: a processor cannot sit idle if there is work to do:

For any greedy schedule ([EZL, 1989]):

$$\max\!\left(\frac{W}{P}, D\right) \le T_P \le \frac{W}{P} + D$$

What about:

- Space usage

- Scheduling overheads

- Locality

#### **Matrix Multiplication**

Fun A\*B { if #A < k then baseCase..  $A = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix}$   $C_{11} = A_{11}*B_{11} + A_{12}*B_{21}$   $C_{12} = A_{11}*B_{12} + A_{12}*B_{22}$   $C_{21} = A_{21}*B_{11} + A_{22}*B_{21}$   $C_{22} = A_{21}*B_{12} + A_{22}*B_{22}$ return C

$$W_{*}(n) = 8W(n/2) + O(n^{2}) \qquad D(n) = D(n/2) + O(1)$$

=  $O(n^{3}) \qquad = O(\log n)$

Parallelism =  $\frac{W}{D} = O\left(\frac{n^{3}}{\log n}\right) \qquad Q(n;Z,L) = O\left(\frac{n^{1.5}}{\sqrt{100}}\right)$

MPI, 2010

LL

#### Matrix Inversion

fun invert(M) { if small baseCase  $M = \begin{vmatrix} A & B \\ C & D \end{vmatrix}$  $D^{-1} = invert(D)$  $S = A - BD^{-1}C$  $S^{-1} = invert(S)$  $E = S^{-1}$  $M^{-1} = \begin{vmatrix} E & F \\ G & H \end{vmatrix}$  $\mathbf{F} = \mathbf{S}^{-1}\mathbf{B}\mathbf{D}^{-1}$  $G = -D^{-1}CS^{-1}$  $H = D^{-1} + D^{-1}CS^{-1}BD^{-1}$  $W(n) = 2W(n/2) + 6W_*(n/2) \qquad D(n) = 2D(n/2) + 6D_*(n/2)$  $= O(n^3)$ = O(n) $Parallelism = \frac{W}{D} = O(n^2)$

#### Summary of Results Q(n;Z,L) =

Scan Memory, prefix sums, merge, median,  $O\left(\frac{n}{L}\right)$  matrix transpose:

Matrix Multiply Matrix Inversion: FFT:

$$O\left(\frac{n^{1.5}}{LZ^{.5}}\right)$$

$$O\left(\frac{n}{L}\log_{Z} n\right)$$

Mergesort, Quicksort, NNs, KD-trees:  $O\left(\frac{n}{L}\log_2(n/Z)\right)$ Funnel Sort:  $O\left(\frac{n}{L}\log_Z n\right)$

Summary of Results D(n) =

Scan Memory, prefix sums, merge, median,  $O(\log n)$ matrix transpose: Matrix Multiply  $O(\log n)$ Matrix Inversion:  $O(\sqrt{n})$ FFT:  $O(\log^2 n)$ Mergesort, Quicksort, NNs, KD-trees:  $O(\log^2 n)$

Funnel Sort: Blocked Sample Sort:  $O(\log^2 n)$

#### Some Basic Results

- **r** Scan memory:  $D(n) = O(\log n)$

- Matrix transpose (divide-and-conquer): D(n) = O(log n)

- Simple matrix multiply (divide-and-conquer): D(n) = O(log<sup>2</sup> n)

- Quicksort and Mergesort:  $D(n) = O(\log^2 n)$

- Funnel sort: D(n) = O(n)

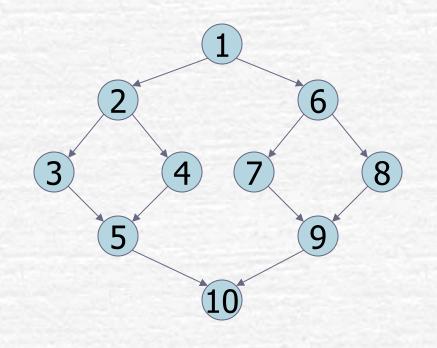

#### Depth-first (sequential) schedule

Depth-First ordering. Same as sequential execution

Q<sub>1</sub>(C;Z,L) – cache complexity for DFS order.

# **Greedy Schedulers**

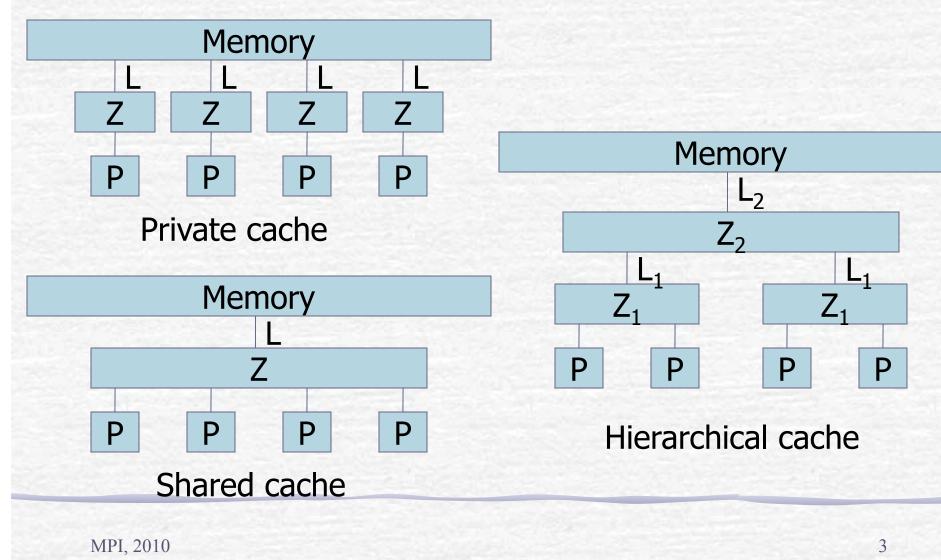

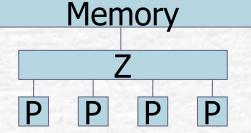

Work stealing ([B+96,ABB00])  $Q_{P}(C;Z,L) = Q_{1}(C;Z,L) + O(PDZ/L) \quad Z \quad Z \quad Z$ private cache  $P \quad P \quad P$

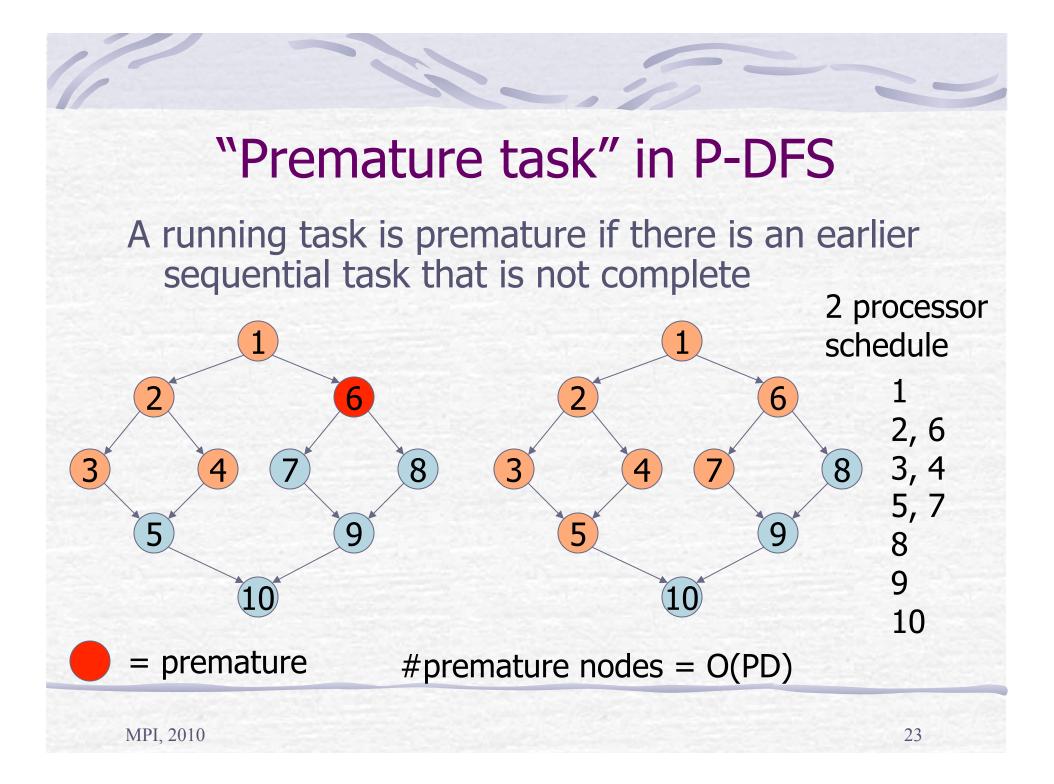

P-DFS [BG02]

$Q_P(C;Z+PDL,L) = Q_1(C;Z,L)

shared cache$

Eg. Matrix multiply  $Q_p(n;Z,L) = O(n^{3/2}/LZ^{1/2} + PZ \log n/L)$  $Q_p(n;Z+PL \log n,L) = O(n^{3/2}/LZ^{1/2})$  P

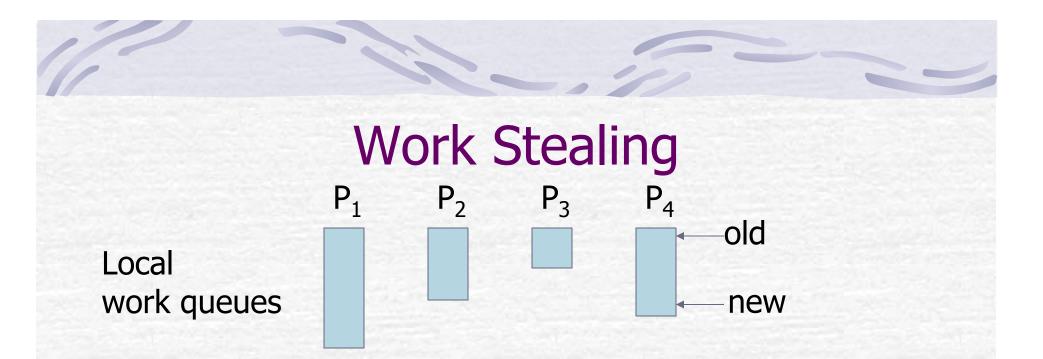

- push new jobs on "new" end

- pop jobs from "new" end

- If processor runs out of work, then "steal" from another "old" end

- Each processor tends to execute a sequential part of the computation.

#### Work Stealing

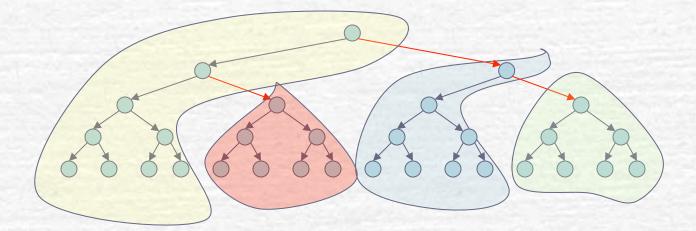

#### Tends to schedule "sequential blocks" of tasks

= steal

#steals = O(PD) [BL98]

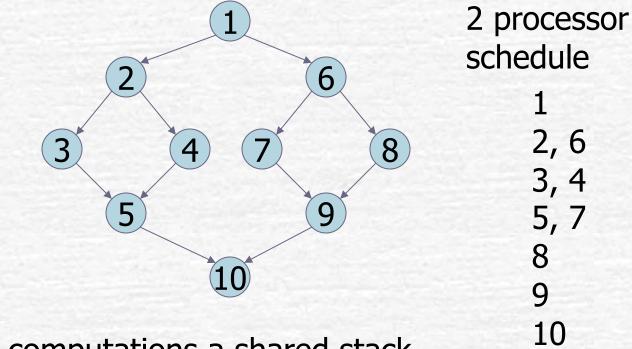

# Parallel Depth First Schedules (P-DFS)

List scheduling based on Depth-First ordering

For strict computations a shared stack implements a P-DFS

### What problems remain?

- What about sorting?

O(log<sup>2</sup>n) span version of sample sort [BGV09]

- Other algorithms? (e.g. geometry, dynamic data structures)

- What about high-span algorithms

Work-efficient Matrix inversion has span O(n<sup>1/2</sup>)

- What about hierarchical caches???

- Idea 1: modify definition of Q<sub>P</sub>

- Idea 2: balance space and work

#### Depth-first (sequential) schedule

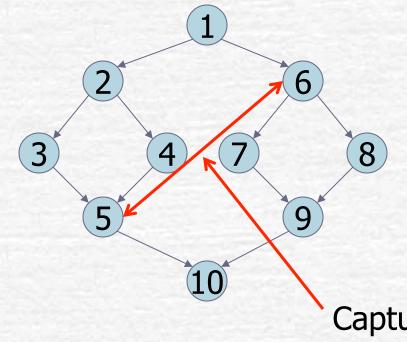

#### Depth-First ordering.

Q<sub>1</sub>(C;Z,L) – cache complexity for DFS order.

Captures artificial locality

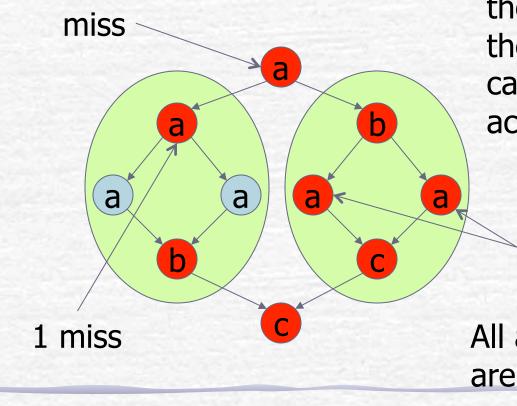

## Idea 1: A variant of the CO model

Idea 1: If a task fits in cache, then any ordered access to the same location will be a cache hit, otherwise an access is a miss

2 misses

All algorithms we have studied are not asymptotically affected

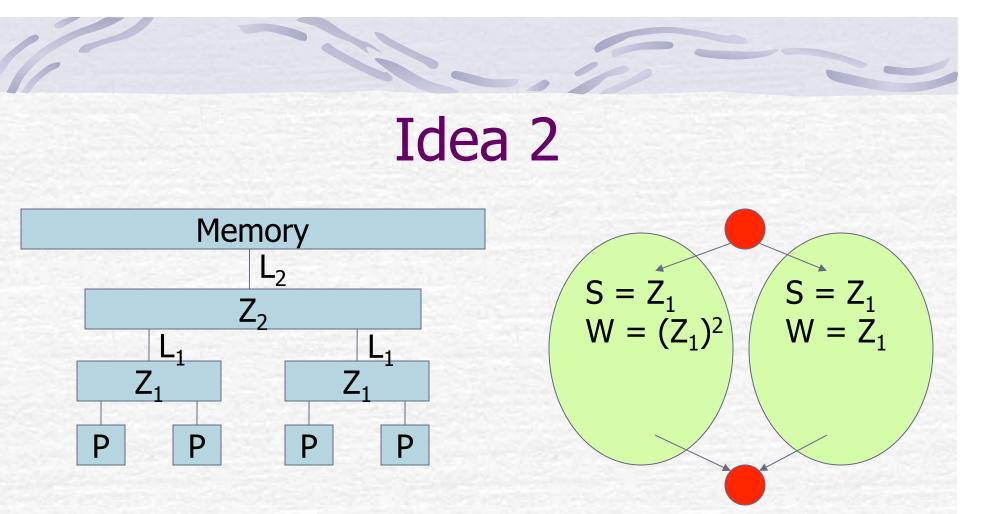

Note that processing power is tied to space.

We need to somehow balance space and work.

#### Idea 2: Effective Cache Complexity

$Q^{*}(a \parallel b) = \max \begin{cases} Q^{*}(a) + Q^{*}(b) \\ s(a \parallel b)^{\alpha} \times \max \{ \frac{Q^{*}(a)}{s(a)^{\alpha}}, \frac{Q^{*}(b)}{s(b)^{\alpha}} \} \end{cases}$

Where s(x) is the space taken by x. Parallelism is bounded by s(a)<sup> $\alpha$ </sup>  $\alpha = 0$ , is sequential execution. For all algorithms we considered top term dominates when  $\alpha < 1$

#### Main Result

A scheduler such that:  $T(n) = \sum_{i=0}^{l} C_i Q^*(n; Z_i, L_i) / P$ For an l-level cache:  $(C_0, Z_0, L_0, P_0), \dots, (C_l, Z_l, L_l, P_l)$   $P_0 = Z_0 = L_0 = 1$  (operations on registers)  $P = P_1 \times \dots \times P_l$

With condition (approx):  $P_i < (Z_i/Z_{(i-1)})^{\alpha}$ \*Requires space annotations on tasks

MPI, 2010

Memory

#### Conclusions

- 1. Can model locality at a high level

- 2. Many cache-oblivious algorithms are naturally parallel, and cache-oblivious nature can be used on hierarchical caches.

- 3. Many open problems.