15-398

15-398 Introduction to Nanotechnology

Nanotechnology And Computer Architecture

Seth Copen Goldstein seth@cs.cmu.edu CMU

lecture 8 15,398

2004 Seth Copen Goldstein

# Today

- · Device requirements

- Manufacturing requirements

- Fabrication

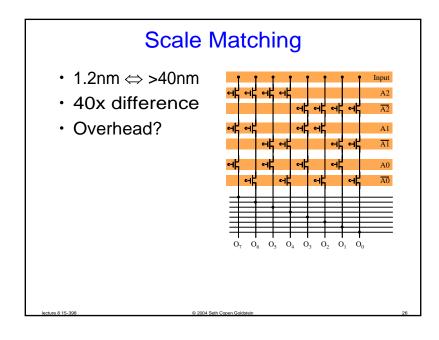

- Micro-nano scale matching

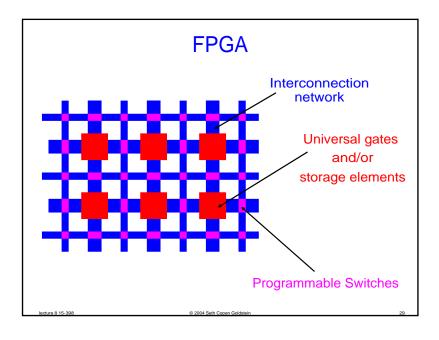

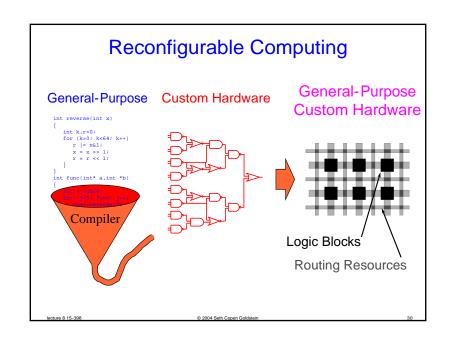

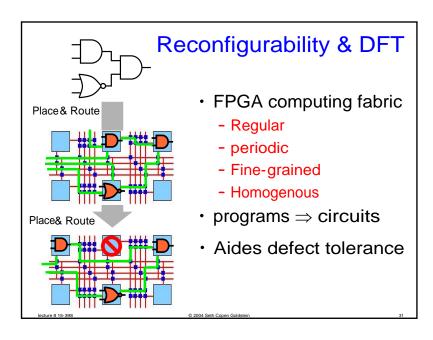

- · Reconfigurable computing

- Architectures

© 2004 Seth Copen Goldstein

# **Computing Devices**

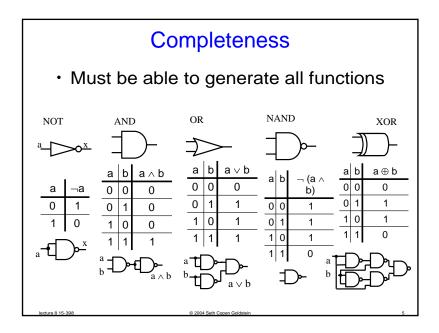

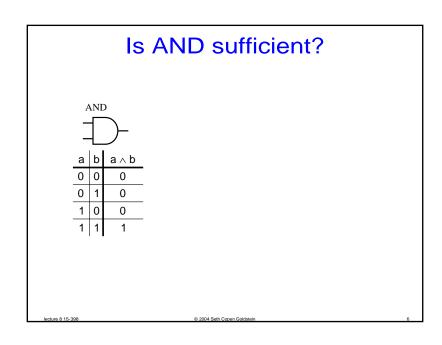

- Completeness

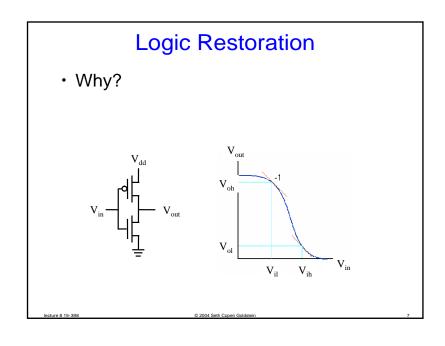

- Logic Restoration

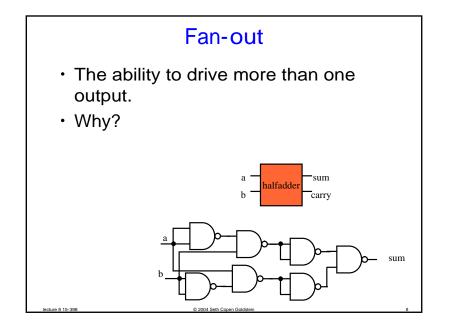

- Fan-out

- Input/Output Isolation

- Power Gain

- Inexpensive

- Low power (zero static power)

- · Dense packing

- Reliable

lecture 8 15-39

© 2004 Seth Copen Goldstein

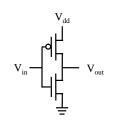

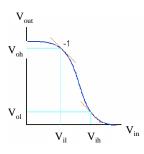

# **Switching**

Devices must have some non-linear characteristic that supports logical computation

lecture 8 15-398

lecture 5

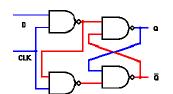

### I/O Isolation

- A change in the output does not affect the value of the input.

- · Why?

# Power gain

· Is it strictly necessary?

SirM model

- Switching

- Isolation

- Restoration

- Memory

# **Necessary Device Abstraction**

- Transistor provides it all

- Switch

- Fan-out

- I/O isolation

- Signal restoration

- Necessary for

Necessary for logic

- large designs

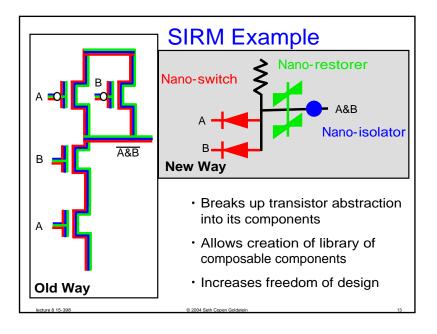

- · Replace single abstraction with multiple abstractions: SIRM

- Enables an incremental path to direct nano-circuits

### **SIRM**

- · SIRM decomposes the abstraction into its fundumental components.

- Switch

- I solation

- Restoration

- Memory

Necessary for logic

Necessary for large designs

- SIRM already in use

- · Allows circuit designers to explicitly manage the different components of a scalable circuit technology

# Manufacturing Requirements

- Inexpensive

- Reliable

- · High yield

- Dense packing

- Scalable

- Top-Down: Photolithography-Combines manufacturing and assembly into one step!

- · Bottom-up: ?

lacture 8 15-30

2004 Seth Copen Goldstein

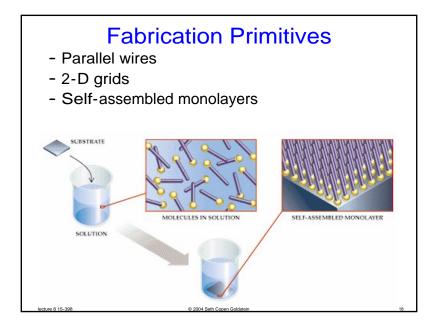

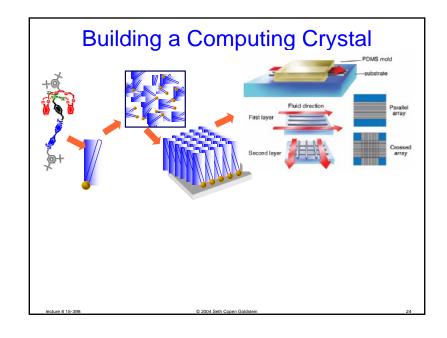

### (scalable) Bottom-up assembly

- Many different techniques:

- Langmuir-Blodgett files

- Flow-based alignment

- EM alignment

- Self-assembled monolayers

- Chemical synthesis

- DNA-based assembly

- Nano-imprinting

- Separates manufacturing and assembly!

- Often, no precise placement control

lecture 8 15-398

© 2004 Seth Copen Goldstein

### **Fabrication Is Different**

- Devices & wires alone are not useful

- Key to nanoscale computing is bottom-up assembly

lecture 8 15-398

2004 Sein Copen Goldstein

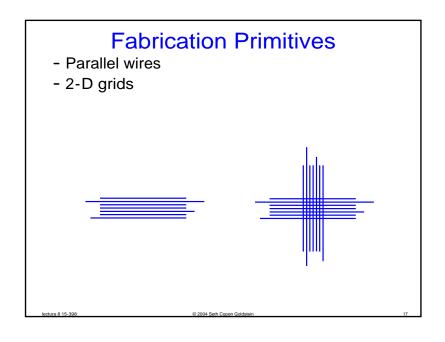

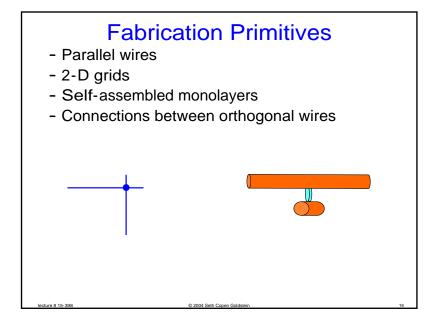

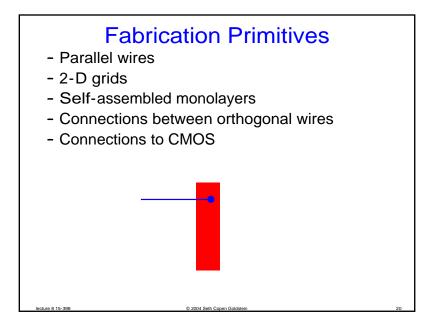

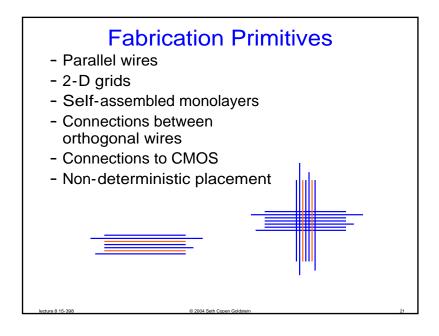

### **Fabrication Primitives**

- Parallel wires

- 2-D grids

- Self-assembled monolayers

- Connections between orthogonal wires

- Connections to CMOS

- Non-deterministic placement

- Selective variability on a lithographic scale

lecture 8 15-398 © 2004 Seth Copen Goldstr

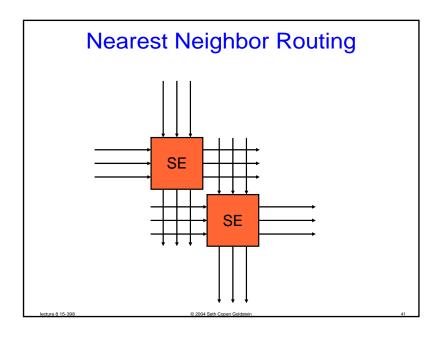

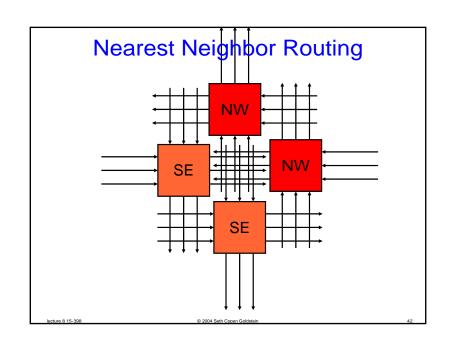

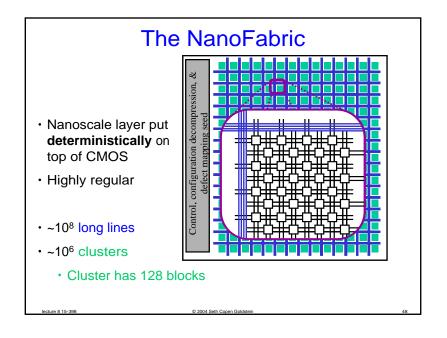

# Harnessing Randomness Fab primitives prefer low information content structures Can we design circuits that can exploit this? Example: Scale Matching Address 1 nanoscale wire with 5log(N) micronscale wires Based on random placement of molecules Nanoscale wires

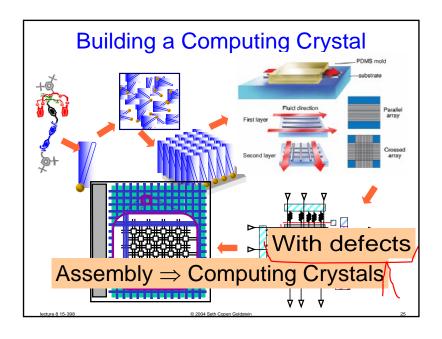

# **Implications**

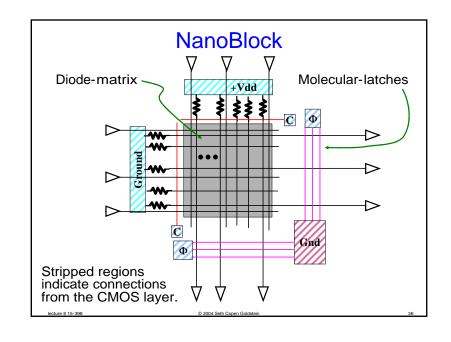

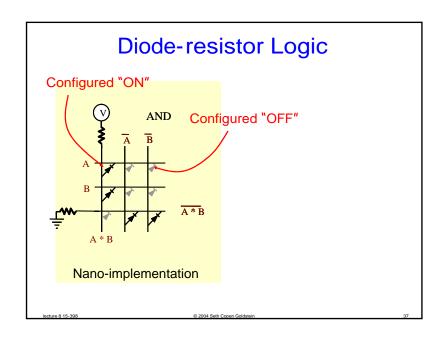

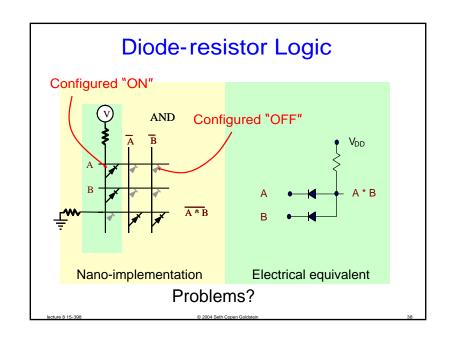

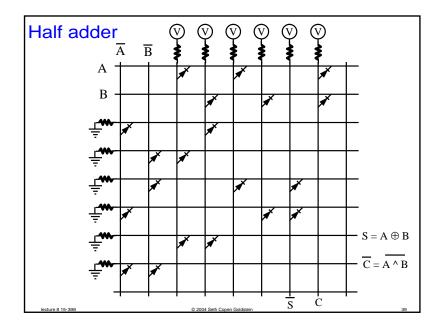

- Prefer devices at cross-points (only 2 terminal devices?)

- Only regular structures

- Defect-tolerance required

- Functionality must be added post-fabrication

lecture 8 15-398

2004 Seth Copen Goldstein

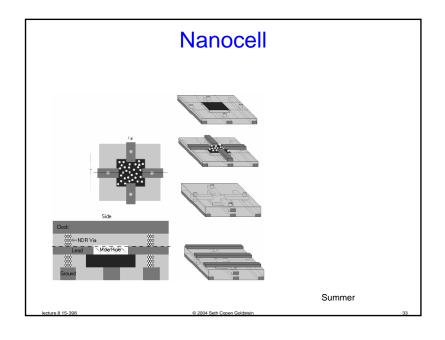

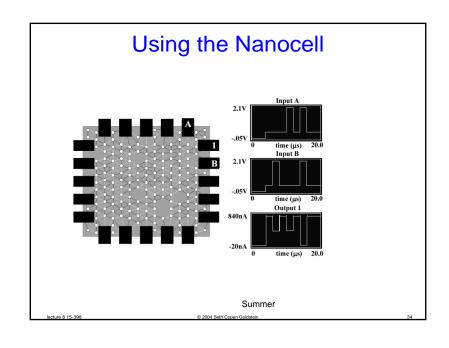

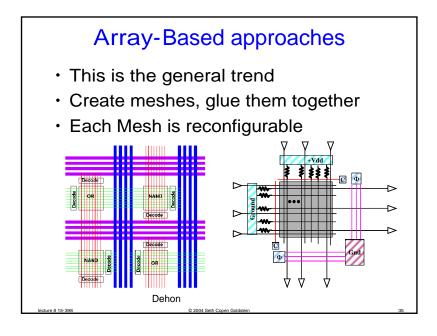

# Sample Proposals

- Can be evaluated on determinism required at fab time

- Nanocell: purely random

- Array-based: quasi-regular

- Nanoscale silicon: determinisitc

5-398 © 2004

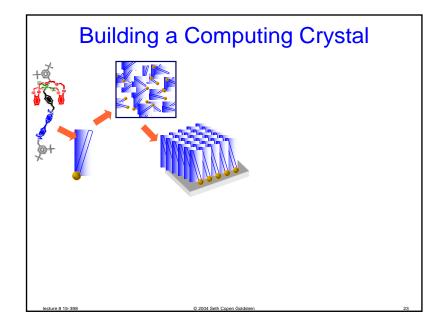

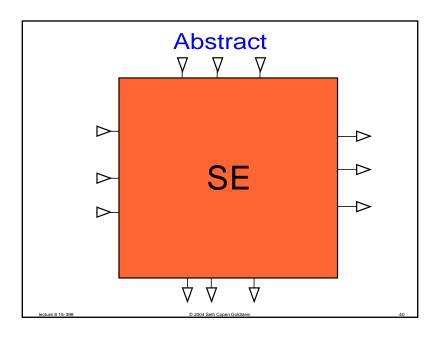

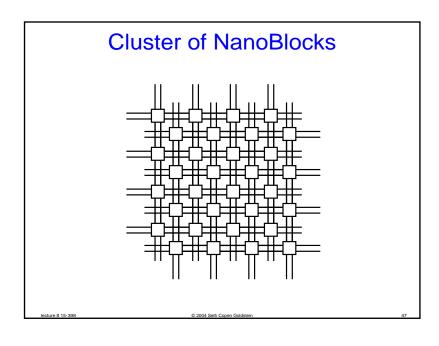

### NanoFabric Attributes

- · Hierarchical fabrication

- 1. Manufacture devices

- 2. Non-deterministically align wires

- 3. Self-assemble monolayers onto wires

- 4. Create meshes

- 5. Deterministically align w/CMOS

- Reconfigurable

- Defect tolerant

lecture 8 15-39

2004 Seth Copen Goldstein

### **Next Time**

- Take a closer look at nano-devices

- · Read chapter 5

- · Recommended Ratner 1973

lecture 8 15-398

© 2004 Seth Copen Goldstein

# Trade-offs

- Ease of Manufacturing Vs. ?

- · Device capabilities Vs. ?

- Device reliability Vs?

- Information content in design Vs?

lecture 8 15-398

© 2004 Seth Copen Golds

This document was created with Win2PDF available at <a href="http://www.daneprairie.com">http://www.daneprairie.com</a>. The unregistered version of Win2PDF is for evaluation or non-commercial use only.