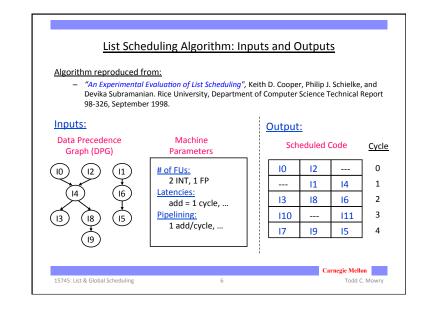

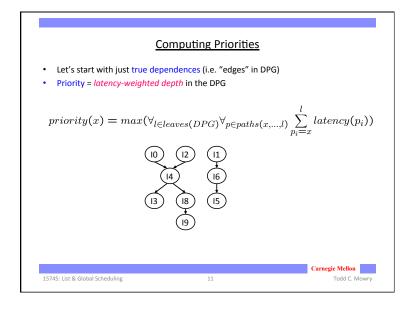

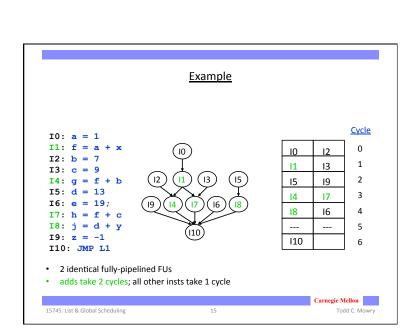

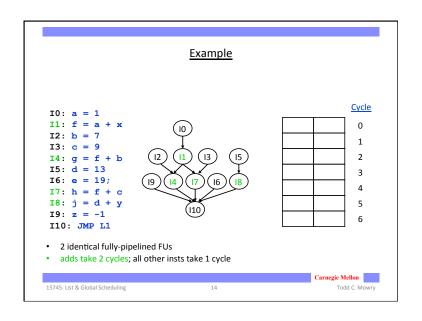

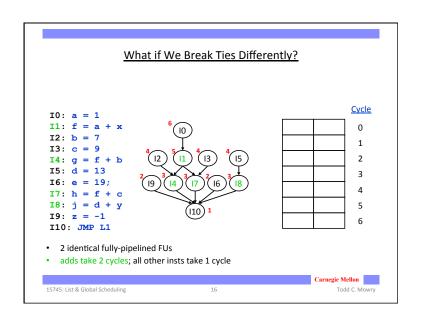

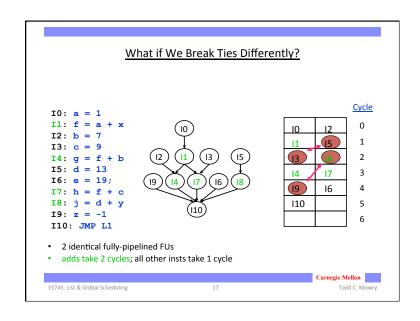

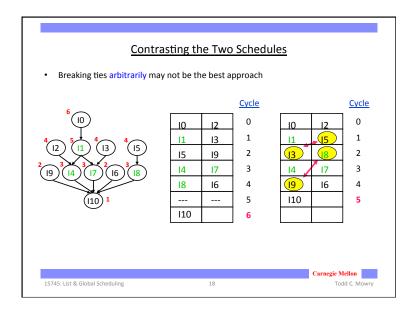

# Intuition Behind Priorities Intuitively, what should the priority correspond to? What factors are used to compute it? data dependences? machine parameters? # of FUS: 2 INT, 1 FP Latencies: add = 1 cycle, ... Pipelining: 1 add/cycle, ... Pipelining: 1 add/cycle, ... Caraegie Mellon Todd C. Mowry

```

List Scheduling Algorithm

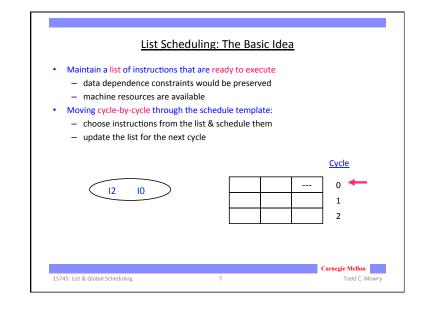

cycle = 0;

ready-list = root nodes in DPG; inflight-list = {};

while ((|ready-list|+|inflight-list| > 0) \&\& an issue slot is available) {

for op = (all nodes in ready-list in descending priority order) {

if (an FU exists for op to start at cycle) {

remove op from ready-list and add to inflight-list;

add op to schedule at time cycle;

if (op has an outgoing anti-edge)

add all targets of op's anti-edges that are ready to ready-list;

}

cycle = cycle + 1;

for op = (all nodes in inflight-list)

if (op finishes at time cycle) {

remove op from inflight-list;

check nodes waiting for op & add to ready-list if all operands

available;

}

Carnegie Mellon

15745: List & Global Scheduling

Todd C. Mowry

```

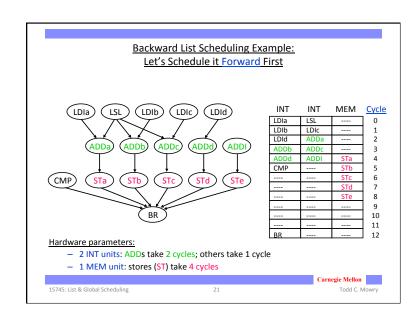

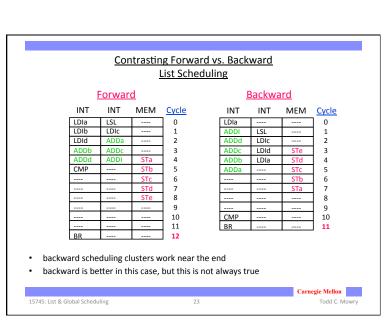

### Now Let's Try Scheduling Backward INT INT MEM Cycle LSL (LDIb) (LDIc) 0 ADDI LSL (ADDd ADDc LDId ADDb LDIa ADDa (CMP) BR CMP 10 Hardware parameters: - 2 INT units: ADDs take 2 cycles; others take 1 cycle 1 MEM unit: stores (ST) take 4 cycles Carnegie Mellon 15745: List & Global Scheduling

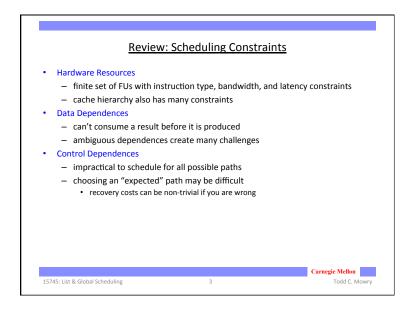

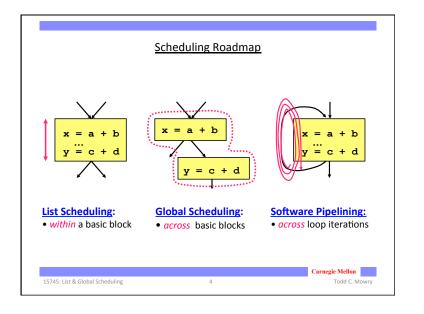

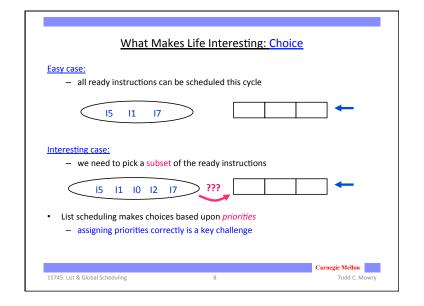

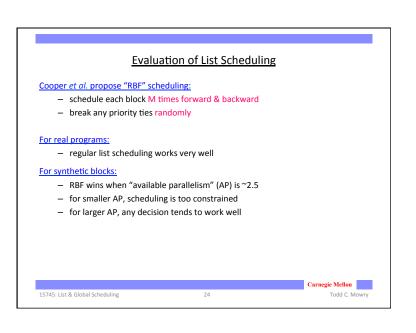

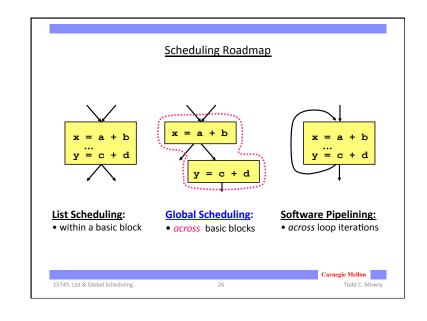

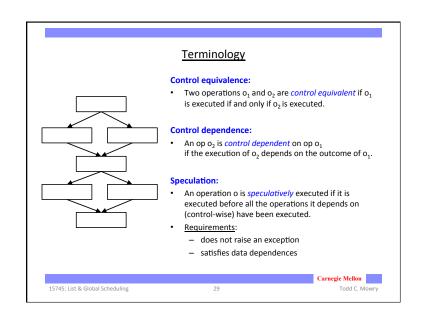

## List Scheduling Wrap-Up • The priority function can be arbitrarily sophisticated – e.g., filling branch delay slots in early RISC processors • List scheduling is widely used, and it works fairly well • It is limited, however, by basic block boundaries Carnegie Mellon 15745: List & Global Scheduling 25 Carnegie Mellon

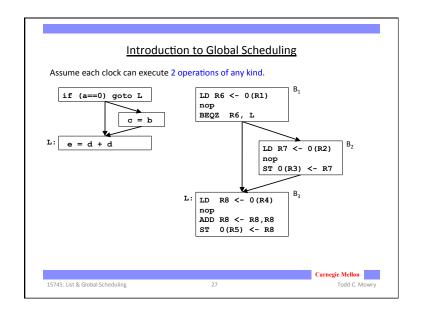

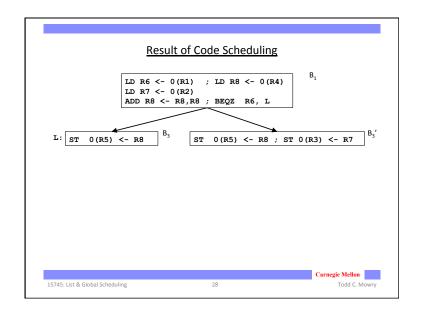

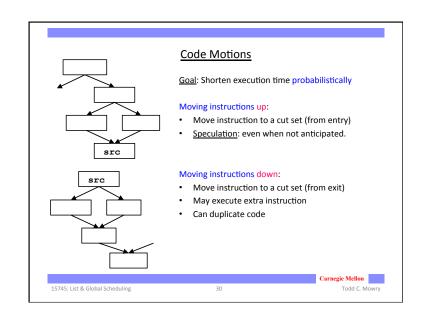

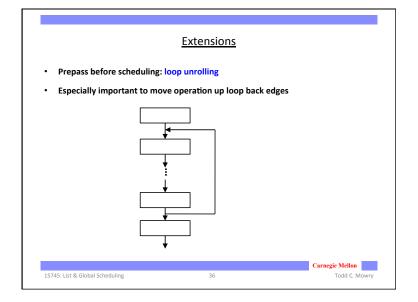

### A Basic Global Scheduling Algorithm Schedule innermost loops first Only upward code motion No creation of copies Only one level of speculation Carnegie Mellon 15745: List & Global Scheduling 33 Todd C. Mowry

### Algorithm Compute data dependences; For each region from inner to outer { For each basic block B in prioritized topological order { CandBlocks = ControlEquiv{B} U Dominated-Successors{ControlEquiv{B}}; CandInsts = ready operations in CandBlocks; For (t = 0, 1, ... until all operations from B are scheduled) { For (n in CandInst in priority order) { if (n has no resource conflicts at time t) { S(n) = < B, t >Update resource commitments Update data dependences Update CandInsts; Priority functions: non-speculative before speculative Carnegie Mellon 15745: List & Global Scheduling Todd C. Mowry

## Program Representation • A region in a control flow graph is: — a set of basic blocks and all the edges connecting these blocks, — such that control from outside the region must enter through a single entry block. • A procedure is represented as a hierarchy of regions — The whole control flow graph is a region — Each natural loop in the flow graph is a region — Natural loops are hierarchically nested • Schedule regions from inner to outer — treat inner loop as a black box unit — can schedule around it but not into it — ignore all the loop back edges → get an acyclic graph

# Summary • Global scheduling - Legal code motions - Heuristics Carnegie Mellon 15745: List & Global Scheduling 37 Todd C. Mowry