#### Outline

- Navigating and changing the IR

- The machine type system

- Using and writing passes

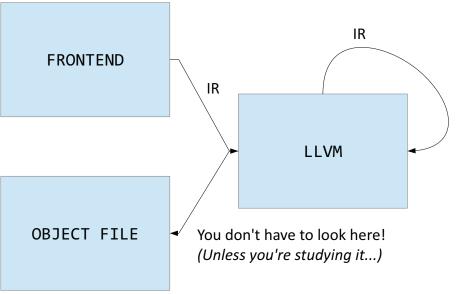

## LLVM, in Greater Detail

Thanks to Gabe Weisz for some content.

**LLVM Overview**

1

# LLVM IR

- C++-based compiler framework

- (Fairly) well documented API

- Structures to help you process programs

- Iterators for modules, functions, blocks, uses

- Functions to inspect data types and constants

- Many classes have dump() member functions that print instances to standard error

- In GDB, use p obj->dump() to see the contents of obj

- Mostly machine-independent assembly

- Target triples define alignment, pointer sizes

- Arbitrary number of "registers"

- Really, stack locations or SSA values

- Virtual registers appear in lower-level IRs

- Locals start with %, globals with @

- Instructions that produce values can be named

2

# Iterators – navigating the IR

- Module::iterator

- Modules are translation units

- Iterates through functions in the module

- · Function::iterator

- Iterates through a function's basic blocks

- BasicBlock::iterator

- Iterates through instructions in a block

- Value::use\_iterator

- Iterates through uses

- Instructions are values; so are constants

- How does SSA help?

- User::op\_iterator

- Iterates over operands.

(Instructions are users!)

- Many instruction classes define convenient accessors

- LoadInst::getPointerOperand

#### More Iterators

- Some iterators wrap other iterators

- inst iterator walks over all instructions in a function

- In Transforms/Utils/FunctionUtils.h

- Prefer ++i over i++ and precompute the end iterator

- Especially for fancier iterators

- Most iterators automatically cast to a pointer to the object type (inst\_iterator does not)

- Be careful about modifying the object you're iterating over during iteration

5

6

#### Instructions

- Instruction is subclassed for various types of operation

- Loadinst, Storeinst, Cmpinst, Branchinst, etc

- Most arithmetic operations are BinaryOperators that contain a code for the operation

- Some instructions can only appear in certain places

- Branches are only at the end of a basic block

- Phi instructions are only at the beginning

# (Re)moving Instructions

- eraseFromParent()

- Remove from basic block, drop all references, delete

- removeFromParent()

- Remove from basic block

- Use if you will re-attach the instruction

- Does not drop references (or clear the use list), so if you don't re-attach it Bad Things will happen

- moveBefore/insertBefore/insertAfter are also available

- ReplaceInstWithValue and ReplaceInstWithInst are also useful to have

## IR Types

- Primitive types

- Integers (iN of N bits, N from 1 to 2<sup>23</sup>-1)

- Floating point (half, float, double, x86\_fp80, ...)

- Weirdos (x86mmx, void, ...)

- Derived types

- Arrays ([# elements (>= 0) x element type])

- Functions (<u>returntype</u> (<u>paramlist</u>))

- Pointers (<u>type</u>\*, <u>type</u> addrspace(<u>N</u>)\*)

- Vectors (<<u># elements (> 0)</u> x <u>element type</u>>)

- Structures ({ typelist }) ...

#### IR Types

- getelementptr instruction gives you the address of a field or an array cell (why have this?)

- Types in the LLVM IR are structural

- Mostly compared by shape, not by name

- Once allocated, there is only one 32-bit integer until the end of time

- Only one instance of a given shape exists at once

- Benefit?

- Exception: "identified" structures

- Problem: how do you write down the type of a singly-linked list?

#### **Identified Structs**

- LLVM 3 came with a redesign of the IR type system mainly over the issue of recursive and abstract types

- Literal structs are compared by shape and must not be recursive; all fields must be known

- {i32, i32}; StructType::get

- Only identified structs can be recursive; declaration and definition of fields is separate

- %T1 = type { type list }; StructType::create

- <u>type list</u> may directly or indirectly refer to %T1

- %T1 = type opaque "I'll fill in the fields later."

- LLVM may rename your identifiers

# **Examples of Types**

```

[40 x i32]

[3 x [4 x i32]]

%sll =

type { i32, %sll* }

i32 (%sll*)*

%struct.a =

type { %struct.b* }

%struct.b =

type opaque

{ i32, [0 x float] }

```

10

# Last words about opaque types

- Opaque types are not void\* (C void\* is i8\*)

- Consider %local a = alloca %a, align 4

```

- %a = type { %b* }

%b = type opaque

• OK!

- %a = type { %b }

%b = type opaque

• "Cannot allocate unsized type"

- %a = type { %b }

```

• "Segmentation fault"

%b = type { %a }

# Module Verifier (-verify)

- opt runs this automatically unless you disable it

- Sanity-checks passes

- You may need to break module invariants while operating on them, eg:

- Types of binary operator parameters are the same

- Terminators (branches) only at the end of basic blocks

- Functions are called with correct argument types

- Instructions belong to basic blocks

- Constants in a switch are the right type

- Entry node has no predecessors (and so on...)

#### **Passes**

- For assignments, don't use provided LLVM passes unless instructed to

- We want you to implement them yourself to understand how they really work

- For projects, use whatever you want

- Two major kinds of passes

- Analysis: provide information

- Transform: modify the program

The mem2reg transform pass

- The LLVM IR is natively SSA

- An Instruction is the same thing as the Value it produces

- %foo = inst in the LLVM IR just gives a name to inst in the syntax; %foo does not exist inside the compiler

- It may be nontrivial for frontends to emit SSA directly

- mem2reg understands certain use patterns that frontends use to emit "variables"

14

#### mem2reg conventions

```

define i32 @ssa1() nounwind {

int ssa1() {

entry:

int z = f() + 1;

%call = call i32 @f()

return z;

%add = add nsw i32 %call, 1

ret i32 %add

alloca in the entry block

define i32 @ssa1() nounwind {

entry:

%z = alloca i32, align 4

%call = call i32 @f()

%add = add nsw i32 %call, 1

only used by load and store

► store i32 %add, i32* %z, align 4

▲ %0 = load i32* %z, align 4

ret i32 %0

```

#### **int** ssa2() { define i32 @ssa2() nounwind { entry:

mem2reg might add SSA features

```

int y, z;

y = f();

if (y < 0)

%call = call i32 @f()

z = v + 1;

%cmp = icmp slt i32 %call, 0

br i1 %cmp, label %if.then, label %if.else

else

z = y + 2;

return z;

%add = add nsw i32 %call. 1

br label %if.end

if.else:

%add1 = add nsw i32 %call, 2

br label %if.end

if.end:

%z.0 = phi i32 [ %add, %if.then ], [ %add1, %if.else ]

ret i32 %z.0

```

18

#### Rules for Phi instructions

- phi type [ val1, inedge1 ], [ val2, inedge2 ]

- Select *val1* if coming from *inedge1*; *val2* if from *inedge2*

- Phi nodes may refer to themselves (loops!) and may select undef (undefined) values for certain in-edges

- Placement requirements:

- must be at the beginning of the block

- must have one entry for each predecessor

- must have at least one entry

# mem2reg confuses easily

```

int ssa3() {

int z:

return *(&z + 1 - 1);

define i32 @ssa3() nounwind {

entry:

%z = alloca i32, align 4

getelementptr

%add.ptr = getelementptr inbounds i32* %z, i32 1

abstracts away

%add.ptr1 = getelementptr inbounds i32* %add.ptr, i32 -1

offset calculation

%0 = load i32* %add.ptr1, align 4

ret i32 %0

```

Why not make mem2reg smarter? (note that compiling with -O2 optimizes this down to ret\_undef)

# Loop information (-loops)

- Analysis/LoopInfo.h

- Basic blocks in a loop

- Headers and pre-headers

- Exit and exiting blocks

- Back-edges

- "Canonical induction variable"

- Starts at 0 and counts up by 1?

- Starts at some number and counts down to 0

- Loop count

## 21

23

# Scalar Evolution (-scalar-evolution)

- Tracks changes to variables through multiple loop nests

- Gives start value, step size, kind of evolution

- Constant

- Add a value each iteration

- Multiply a value each iteration

- More complicated relationships as well

- Useful to aggregate accesses into arrays into larger blocks or to improve cache performance

## Using an analysis pass

- #include "llvm/Analysis/LoopInfo.h"

- AU.addRequired<LoopInfo>();

in qetAnalysisUsage()

- LoopInfo& LI = getAnalysis<LoopInfo>(F); in a function called from runOnModule with function F inside that module

- LI.dump()

"Loop at depth 1 containing:

%for.cond<header><exiting>,%for.body,

%for.inc<latch>" (from loop.c)

- PassManager sequences both kinds of passes using getAnalysisUsage()

# Target Data (-targetdata)

- Endian-ness

- Pointer sizes

- Alignment

- Actual size (in bits) of variables

- Actual layout of structures

- (taking into account platform alignment requirements)

22

## Alias Analyses

%1 = load i32\* %Astore i32 5, i32\* <u>%B</u> %3 = add i32 %1, i32 9store i32 %3, i32\* %C

If we know that %A != %B != %C we have more freedom to reorder code, promote to registers, etc.

- LLVM includes a number of passes that collect various kinds of alias information

- Can get information about both global and local variables

- Included passes take into account the behavior of the C standard library (eg, sin() will not make new aliases)

## Simplify CFG

- A cleanup pass

- Removes unnecessary basic blocks by merging unconditional branches if the second block has only one predecessor

- Removes unreachable blocks

- Removes Phi instructions in blocks with single predecessors

25

26

# Other useful passes

- Liveness-based dead code elimination

- Assumes code is dead unless proven otherwise

- Sparse conditional constant propagation

- Aggressively search for constants

- Correlated propagation

- Replace select instructions that select on a constant

- Loop invariant code motion

- Move code out of loops where possible

- · Dead global elimination

- Canonicalize induction variables

- All loops start from 0

- Canonicalize loops

- Put loop structures in standard form

# Notes on Writing Passes

- Declare which passes you use (and what your pass mutates) in getAnalysisUsage

- The CommandLine library allows you to add command line parameters very quickly

- Conflicts in parameter names won't show up until runtime, since passes are loaded dynamically

- Be mindful of correctness; the module verifier is like a syntax checker

- Does your pass make sense in a multithreaded environment?

# Transformations and memory

For regular loads/stores, LLVM forbids introducing new stores to externally observable locations:

```

int x;

void f(int* a) {

for (int i = 0; i < 100; i++) {

if (a[i])

x += 1;

}

}

x += 1;

}

x = xtemp;

}</pre>

int x;

void f(int* a) {

int xtemp = x;

for (int i = 0; i < 100; i++) {

if (a[i])

xtemp += 1;

}

x = xtemp;

}

```

- volatile marks memory operations that cannot be reordered (wrt volatile operations) or removed

- To support new features in C++11, LLVM provides other atomic orderings that can be applied to loads and stores

#### Links

- When in doubt, read the documentation—and the code!

- http://llvm.org/doxygen/

- Articles on the LLVM site are very useful

- http://llvm.org/docs/Passes.html

- http://llvm.org/docs/ProgrammersManual.html

- http://llvm.org/docs/Atomics.html

- http://llvm.org/docs/LangRef.html

## Projects using LLVM

- Just a few from llvm.org:

- Clang: a C-family language frontend

- LLDB: an improved debugger using Clang data

- vmkit: building Java/.NET VMs

- klee: a symbolic virtual machine for LLVM IR

- Emscripten: LLVM bitcode → JavaScript

- http://emscripten.org/

29

- Vellvm: a formalization of the LLVM IR

- http://www.cis.upenn.edu/~jianzhou/Vellvm/

30

Supplemental

# High-level view of atomic orderings

- NotAtomic ordinary loads/stores; races are undefined

- Unordered races have "somewhat sane" results

- A load cannot see a value which was never stored

- May not be supported for all types on all platforms

- Used for shared variables in Java, "safe" languages

- Monotonic single locations have consistent order

- Acquire/Release when paired together, strong enough to write a lock

- SequentiallyConsistent Acquire loads, Release stores, and all SequentiallyConsistent operations have a total order

- Java volatile

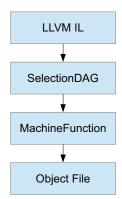

# Your module, post-IL

- LLVM still has to generate machine code!

- Your module goes through ~3 more stages:

## Atomic orderings and you

- If your project is about fine-grained parallelism or lock-free data structures, you need to think about these things

- LLVM also exposes cmpxchg, atomicrmw, fence

- LLVM does not expose LL/SC

- If not, just don't, in general:

- reorder LLVM volatile operations wrt other volatile operations

- introduce new stores to (shared) locations that would not have been previously stored to

- More details at http://llvm.org/docs/LangRef.html#memmodel

33

34

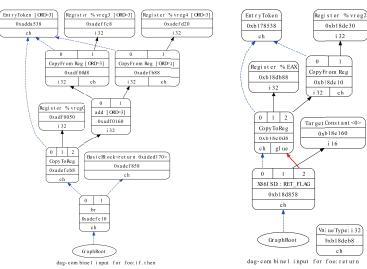

#### LLVM IL → SelectionDAG

#### LLVM IL → SelectionDAG

if.then:

%add = add nsw i32 %a, %b

br label %return

return:

%retval.0 = phi i32 ...

ret i32 %retval.0

#### SelectionDAG transformations

- Build initial DAG from LLVM IR

- Simplify!

- Legalize types (vectors → scalars)

- Simplify!

- Legalize ops (x86 doesn't do byte-size CMOVs)

- Simplify!

- Select instructions

- Schedule instructions

37

38

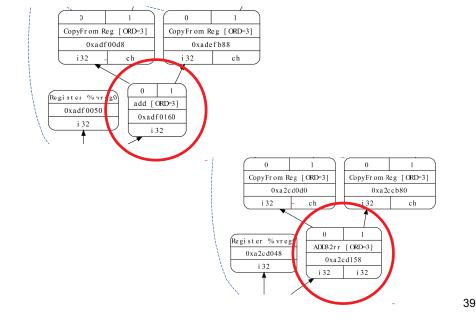

# Instruction selection

# Target-Independent Code Generation

- There are a lot of different machines!

- And even on x86, there are a lot of different ADDs!

- Make the process data-driven

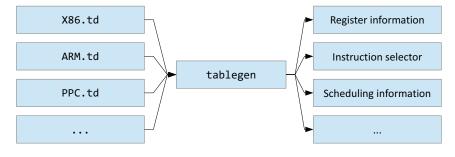

# tablegen

- The tablegen tool is run when compiling the LLVM library for each target

- It accepts a custom text-based record description format and generates C++ definitions using various backends

- defm ADD : ArithBinOp\_RF<0x00, 0x02, 0x04, "add", MRM0r, MRM0m, X86add\_flag, add, 1, 1>;

- ArithBinOp\_RF is actually another macro...

- There is still a lot of human-written code in the backends (X86 instruction encoding, for one)

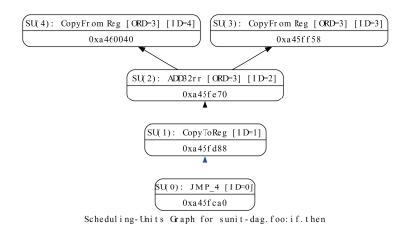

# Scheduling

We have choices to make (here, which CopyFromReg executes first?)

#### ADD32rr

```

def ADD32rr {

Format BinOpRR:f = MRMDestReg;

Domain I:d = GenericDomain;

string Namespace = "X86";

dag OutOperandList = (outs GR32:$dst);

dag InOperandList = (ins GR32:$src1, GR32:$src2);

string AsmString = "add{l} {$src2, $src1|$src1, $src2}";

list<dag> Pattern =

[(set GR32:$dst, EFLAGS,

(X86add_flag GR32:$src1, GR32:$src2))];

list<Register> Uses = [];

list<Register> Defs = [EFLAGS];

list<Predicate> Predicates = [];

InstrItinClass Itinerary = IIC BIN NONMEM;

string Constraints = "$src1 = $dst";

bits<8> Opcode = { 0, 0, 0, 0, 0, 0, 0, 1 };

Format Form = MRMDestReg;

bits<6> FormBits = { 0, 0, 0, 0, 1, 1 };

... lots more ...

```

41 ... lots more ...

# Scheduling

42

44

**Chains** add control dependency. **Glue** forbids breaking up instructions.

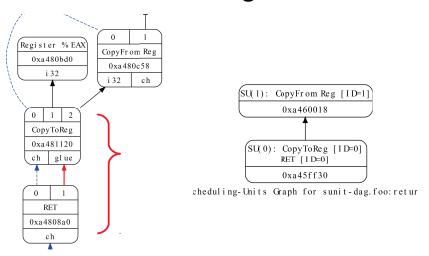

# Lowering to MC

%EAX<def> = COPY %vreg2; GR32:%vreg2

RET

#### MC transformations

- SSA-based MC optimizations

- Register allocation

- 2AC correction and Leave SSA; copy coalescing; add spillcode

- Prolog/epilog insertion

- Stack layout

- Last-chance MC optimizations/spillcode scheduling

- Encoding

Thanks, abstraction!

46