# CS 740, Fall 1998

# Assignment 2:

# Handling Pipeline Hazards

Assigned: Thursday, Sept. 24 Due: Thursday, Oct. 8

#### 1. Policy

You may work in a group of up to 3 people in solving the problems for this assignment. You should turn in a single report for your entire group, identifying all of the group members.

### 2. Logistics

Any clarifications and revisions to the assignment will be posted on the class bboard and Web page. For this assignment, you will want to retrieve the file:

/afs/cs.cmu.edu/academic/class/15740-f98/public/asst/asst2/files.tar

You will hand in a hard copy document for this assignment. Formatted text is preferred to hand written.

You should also provide us with a version of your code file stages.c. Do this by naming your file *last*-stages.c, where *last* is the last name of one of your group members, and copying this file to the directory

/afs/cs.cmu.edu/academic/class/15740-f98/public/asst/asst2/handin

Include as comments near the beginning of this file the identities of all members of your group.

#### 3. Introduction

The purpose of this assignment is to gain a deeper understanding of how pipelined processors are implemented. Our method of doing this will be to create a C program that "simulates" pAlpha, a pipelined implementation of a subset of the Alpha architecture. Although C is not an ideal language for describing and simulating hardware designs, one can get a high level view of how the hardware operates by using an appropriate coding style.

You can pick up the entire set of files by copying and untarring the file files.tar. The source files include the following:

alpha.h: Macros defining the pAlpha instruction format. These are generally consistent with the Alpha architecture.

sim.h. sim.c Simulator framework.

stages.h, stages.c A partial implementation of the pipeline stages. You will need to fix and extend the code in the file stages.c.

In addition, there are some files containing utility routines for the simulator, user interface code, plus a subdirectory called demos containing some sample machine programs.

The code can be compiled to generate two different user interfaces:

alpha\_tty A batch-oriented interface that prints all kinds of trace information out as it executes.

alpha\_tk A graphic-user interface based on Tcl/Tk that lets you watch and control the simulator execution.

The GUI version is far more pleasant to use. The batch interface is provided as the fall-back on systems that do not support Tcl/Tk. Also, the batch version works better for doing systematic testing of your solution.

You may want modify the file alpha\_tk to include pathnames for the directory in which you install your code.

A correctly working version of the simulator that runs on the class alphas has been installed as:

/afs/cs.cmu.edu/academic/class/15740-f98/public/sim/solve tk

You might find it useful as an aid in debugging your own code.

### 4. pAlpha Instruction Set

Refer to page 45 of the lecture 2 notes for a description of the Alpha instruction formats.

The pAlpha instruction set includes only 7 classes of instructions:

**Arithmetic Operations** These are ADDQ, SUBQ, ADDL, SUBL, CMPULT, CMPLT, BIS, ORNOT, XOR, CMOVEQ, and CMOVNE. These instructions can be of either register-register or register-immediate format.

Load The LDO instruction.

**Store** The STQ instruction.

Conditional Branches These are BEQ and BNE.

Unconditional Branches These are BR and BSR.

**Jump** The JMP instruction.

**Call PAL** This instruction is used to halt the simulator.

The intention of the implementation is to use the semantics of the Alpha instruction set. This includes requiring memory references to be aligned, etc. When you complete this lab assignment, all instructions will be fully implemented.

# 5. pAlpha Implementation

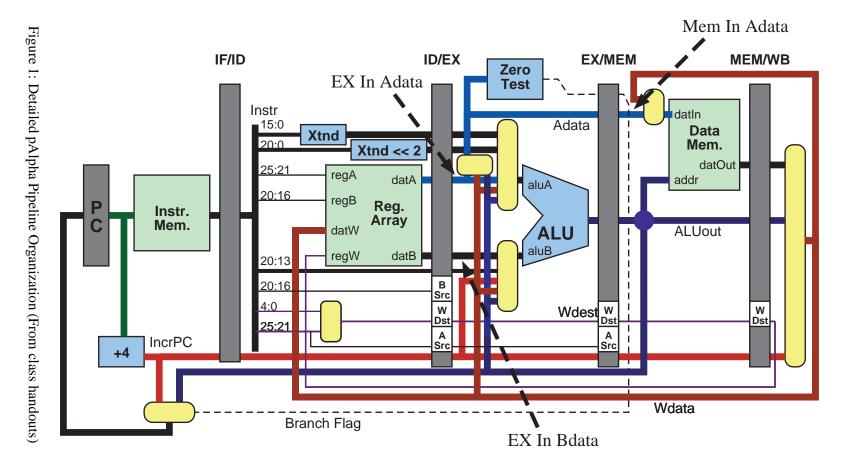

Figure 1 illustrates the structure of the pAlpha implementation. This implementation is styled after the DLX pipeline implementation described in Chapter 3 of the textbook. The figure is taken from the class handouts.

# Branch Flag & Target

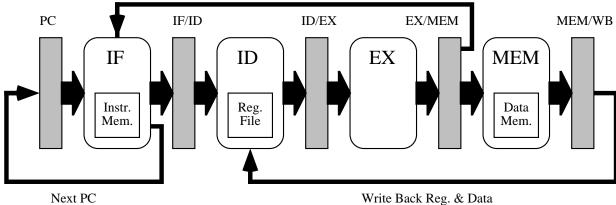

Figure 2: Simplified pAlpha Pipeline Organization

The rectangular blocks in the figure denote *pipe registers*, a set of registers that hold the state used by the pipeline stages. Note that the program counter PC is one such pipe register, while the others are labeled by the states between which they sit. Embedded within the stages are additional state elements: the instruction memory in IF, the register file in ID, and the data memory in MEM. To keep things simple, the instruction data memories are distinct. In the actual processor, there are indeed separate instruction and data caches, but these both access a common main memory. Also shown are the major functional units: an adder in IF to increment the program counter, and an ALU in EX to compute data values, effective addresses, and branch targets, and a "Zero Test" block in EX to compute branch conditions. Also shown are the bypass paths used to support register forwarding.

Figure 2 shows a simplified version of the pipeline structure. The rounded rectangles denote the logic of each of the pipeline stages, while the arcs denote the signal connections.

A pipe register has a current state and a next state. Each pipeline stage takes the current state of one or more pipe registers and generates the next state of one or more pipe registers. One cycle of the pipeline consists of two phases: during the *operate* phase the pipe stages compute new values for the registers, while during the *update* phase, the pipe registers store these values and deliver them as inputs to the next stage.

Note that there is no explicit write-back stage WB. Instead, the write-back logic is incorporated into the decode stage ID, to avoid a conflict at the register file.

The version of the pipeline provided to you has serious deficiencies. In particular, stalling and forwarding are not used to handle hazards. Therefore both data and control hazards are handled incorrectly. Furthermore, none of the conditional move instructions are fully implemented. Otherwise, the design should be correct. **Please notify us if you find any bugs in the code**.

The handling of 64 bit integers within the simulator may seem odd. The reason is that the simulator is designed to operate on multiple platforms, some of which may not support 64-bit values. Therefore 64-bit integers are represented in the simulator by a structure consisting of two 32-bit values:

```

typedef struct {

bit32 high;

bit32 low;

} bit64;

```

Although you will be doing this lab on the class Alphas, you should continue to follow the convention of

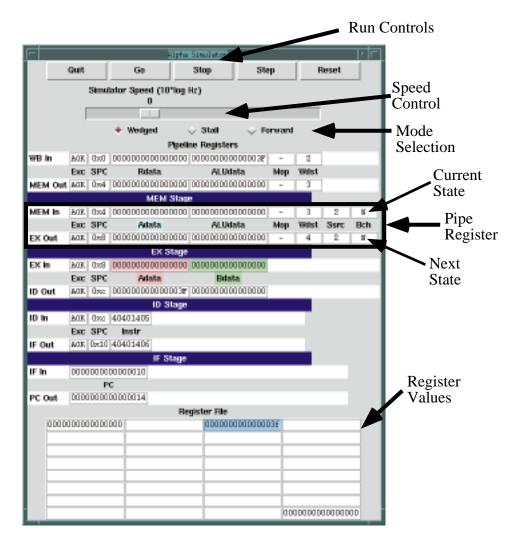

Figure 3: Main Control Panel for Alpha Simulator

using the bit64 structure when making modifications.

# 6. GUI Version of the Simulator

For part of this assignment, you will be working with the GUI version of the simulator.

When you invoke the simulator with a code file (in the '.O' format described below) as a command line argument, two windows will appear on your machine as illustrated in Figures 3 and 4. The first provides the overall control for the simulator as well as displaying the state of the pipeline and the registers. The second provides a listing of the code and tracks the instructions as they progress through the pipeline.

Viewing the control panel in Figure 3 from top to bottom, we find the following regions:

**Run Controls** A set of buttons that control the simulator activity:

**Quit** Exits the simulator

**Go** Starts (or restarts) the simulator. Simulation continues until either an exception condition is encountered, or the **Stop** button is pressed.

**Stop** Stops the simulation.

**Step** Simulates for one clock cycle.

**Reset** Empties the pipeline and resets the program counter to 0.

**Speed Control** Controls how fast the simulator will execute. The control is logarithmic—at the extreme left the simulator runs at 0.1 cycles per second, while at the extreme right it runs at 1000 cycles per second. The default value is 1 cycle per second.

**Mode Selection** Controls the simulation mode. These are:

**Wedged** This is the version you will be given for Lab 3. It lacks any mechanism for handling control or data hazards.

**Stall** This (should) be the version that handles hazards by stalling the pipeline appropriately until the hazard can be resolved.

**Forward** This (should) be the version that handles hazards by forwarding whenever possible.

**Pipeline State** This region displays the state of all of the *pipe registers*, oriented with the PC on the bottom up to the MEM/WB register on the top.

Each pipeline register is represented by two rows of boxes. The upper row indicates the current state of the register and is named after the primary stage which uses it. The lower row indicates the next state of the register and is named after the stage which updates it. For example, the figure shows a box around pipe register EX/MEM. This register is updated by the EX stage and used (primarily) by the MEM stage. The top row, labeled **MEM In**, indicates the current state of the register, while the lower row, labeled **EX Out** indicates the next state of the register.

The *pipeline stages* are indicated in blue: each stage takes input from the current state of the preceding pipe register, and computes the next state of the pipe register following the stage.

**Register State** These are shown as 8 rows of 4 registers each, with the values displayed in hexadecimal. A blank entry is one that has never been updated. Its value is 0. The most recently updated register is indicated in blue.

The fields of the pipeline registers are as follows:

**PC** The program counter register (hex).

**Exc** The exception status for the stage. As an instruction progresses through the pipeline, its condition can go from AOK, meaning everything is fine, to some exceptional condition. Once the exception reaches the WB stage, the simulator will halt.

**SPC** Indicates which instruction is at this stage in the pipeline (hex). This information would not normally be maintained by the hardware. It is included here to aid debugging. A bubble in a stage is indicated by ----.

**Adata** This is the data read from the A port of the register file (hex).

**Bdata** This is the data read from the B port of the register file (hex).

**ALUdata** This is the data generated by the ALU (hex).

**Mop** Indicates the memory operation to be performed, either 'R' (read), 'W' (write), or '-' (none).

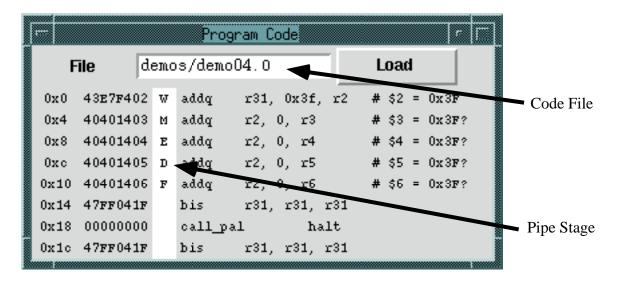

Figure 4: Code Window for Alpha Simulator

**Wdst** The destination register for write back (decimal).

**Ssrc** Identifies the source register for a store operation (decimal). You'll notice that this information is not currently used by the simulator, but you might find it useful in implementing some of the forwarding.

**Bch** Indicates whether (Y) or not (N) a branch will be taken.

To help visualize forwarding there are three colors defined, corresponding to the Adata (pink) and Bdata (green) fields of the EX stage, and the Adata (blue) field of the MEM stage. During normal operation, these operands are taken from the corresponding field of the ID/EX or EX/MEM pipeline register, as indicated by the dashed arrows in Figure 1. In the event of bypassing, however, these operands may be supplied from other locations, using the multiplexors indicated in Figure 1. The color moves to indicate the identity of the source field.

### 7. Object Code

The simulator reads in an ASCII version of object code. We denote these object code files with the suffix '.O'. Each line consists of an address, the instruction (both in hexdecimal) optionally followed by text, containing, for example, an assembly code version of the instruction. The simulator executes using the hexadecimal coded instruction. You can't change the code by simply editing the assembly code comments in the .O file.

Using an Alpha machine, you can generate this code automatically. First, create a .s file. Then assemble this file to get a .o file. Finally, disassemble this code using the program dis, e.g., with the command:

```

dis -h test.o > test.0

```

The code is displayed in a window such as that shown in Figure 4. At the top is an entry box where you can specify the file name and load a file by pressing the **Load** button. Each line of code is displayed giving its location, the hexadecimal code, and any text that appeared on that line in the .O file. Also indicated is the pipeline stage for any instruction being executed.

#### 8. Your Task

For this assignment you have four tasks:

- 1. Complete implementation of the two conditional move instructions.

- 2. Implement the proper handling of hazards in *stall mode*.

- 3. Implement the proper handling of hazards in *forward mode*.

- 4. Generate test code that will test all instruction types and all hazard possibilities.

All of the "hardware" modifications involve changing only the code in the file stages.c. You may change your own versions of the other files, e.g., to print out stuff while debugging, but your simulation should run properly with the original versions, since stages.c is the only file you will be allowed to hand in.

#### 8.1. Conditional Move Instructions

Complete the implementation of these two instructions in a manner consistent with the rest of the design. Note that the simulation of the ALU operation in file sim.c is insufficient to correctly implement conditional moves for all cases. In the file stages.c, you should add additional logic to ensure that these instructions have the correct behavior in all cases. Make sure that you place the additional logic at the location indicated in the comments.

### 8.2. Hazard Handling in Stall Mode

This mode should be followed when the global variable sim\_mode is set to S\_STALL. It should use stalling to correctly handle both data and control hazards. It should cancel instructions only when stalling is insufficient to handle a particular hazard. Excessive use of cancelling in this mode will result in loss of points. Also, performance problems caused by unnecessary stalling will be penalized.

You can implement this version by inserting appropriate code into the procedure do\_stall\_check. At the end of this procedure there is some code that will do the actual stalling for you: you only need to tell it when to stall. You can stall in the IF, ID or EX pipeline stages by setting the appropriate variable to 1. The three variables involved are stall\_if, stall\_id and stall\_ex.

When stalling is insufficient to handle a hazard, cancel instructions by calling the procedure sim\_cancel\_stage.

All the information you need to do a successful job is provided to you: you can get the current pipe-register state by means of the global variables id\_in, ex\_in etc., and the computed next state is available via arguments to the procedure. Both current and next state will be valid, since all of the stages have already computed their outputs by the time do\_stall\_check is called.

To guide your implementation, we have indicated where your code should be located with comment dividers, named START STALL MODE and END STALL MODE. All of your stall-mode code should be located between those two dividers. In addition, you are neither allowed to create any static variables nor to change/create any global variables. There is no need to create or modify new global state to come up with a correct solution.

# **8.3.** Hazard Handling in Forwarding Mode

For forwarding mode, you will need to use the following mechanisms:

- Use forwarding (i.e., bypassing) whenever possible to handle data hazards without incurring any delays.

- Add stalls to handle any data hazards for which forwarding alone does not suffice.

- Handle branches by assuming they will not be taken, and canceling any instructions that should not have been fetched in the event that the branch is taken. The way to do this is to call the procedure sim\_cancel\_stage from within do\_stall\_check.

- You may handle jumps either in the same way as branches (always mispredicting!) or by stalling.

This mode should be used when the global variable sim\_mode is set to S\_FORWARD. You can implement this version by inserting appropriate code into the procedures do\_ex\_stage, do\_mem\_stage, and do\_stall\_check. In the latter procedure, the code will be similar to that of the stalling mode, although you'll need to stall in fewer cases. For the code within the EX and MEM pipeline stages you will implement three "multiplexors" ("muxes"). The A and B muxes in the EX stage can override the Adata operands coming from the ID/EX pipeline register. The S mux in the MEM stage can override the Adata operand coming from the EX/MEM pipeline register. Your code should implement the control for these multiplexors by setting the variables amux, bmux and smux appropriately.

To guide your implementation, we have indicated where your code should be located with comment dividers, named START FORWARD MODE and END FORWARD MODE. All of your forward-mode code should be located between those dividers. In addition, you are neither allowed to create any static variables nor to change/create any global variables, except for amux, bmux and smux. Again, there is no need to create new global state to come up with a correct solution.

#### 8.4. Testing

The test cases in the demos subdirectory are a good start, but they are not comprehensive. You should carefully analyze all of the different instruction types, all of their possible pipeline interactions, and generate test code that will exercise these interactions. Note that you need not consider every possible instruction for all possible data values. Instead you can group instructions into classes and try them for representative data values.

Writing lots of test code by hand and then running them on the GUI interface is not a good idea—it is very time consuming and hard to get reliable results. Instead, you should set up a systematic "test bench," consisting of a semi-automatic way to generate, simulate, and evaluate test cases. Using a scripting language such as Perl or Tcl can be very useful for this task. Refer to the lecture discussion on micro-tests as one possible approach.

For this problem you should hand in the following:

- A description of your testing methodology for conditional move instructions. You should describe

the various outcomes of executing each conditional move, as well as how you test that the expected

outcomes are achieved.

- The results of running your code against these tests.

- A description of your testing methodology for data hazards. You should document your testing methodology by creating table(s) of all the different hazard types, as well as an indication of how you test that this hazard is handled properly. Look at the lecture slides for the sort of table we expect to see here.

- The results of running your code against these tests.

- A description of your testing methodology for control hazards. You should try to devise a systematic way to tabulate possible control hazards, e.g., instructions that should or should not be executed within some distance of a branch or jump.

- The results of running your code against these tests.

Remember that you must also handle hazards induced by a load instruction followed by an instruction requiring the result of the load. Be especially careful to test hazards involving register 31.

### 8.5. Additional Guidelines

- It is important that you do not change any global state other than the mux signals, nor create any new global state.

- For the hazard handling, please make sure that *all* of your code is located between the appropriate comment dividers.

- Although it may be tempting, do not rearrange what gets computed in what stage, or add any additional pipeline state.

- Remember that each stage must obey the protocol of taking pipe register current state and computing pipe register next state that will feed into the next stage. With forwarding, you will find that the EX and MEM stages access the current state of multiple pipe registers.

- The stall logic is implemented by a separate procedure do\_stall\_check that is called between the operate phase of the stages and the update phase of the pipe registers. This procedure can therefore make use of both the current and next state of all the pipe registers, but its only effect should be to cancel or stall some of the pipeline stages.

- Your implementation will require writing roughly 100 lines of code.

#### 9. Hand In

#### Electronic submission:

1. Your version of stages.c. Remember to fill in the structure at the beginning of the file with the names of your group members. Also remember to comment your solutions.

### Hard-copy submission:

- 1. A description of how you implement the conditional move instructions.

- 2. A description of your stall-mode hazard handling mechanism. Document the conditions under which you stall stages. Document the conditions under which you cancel instructions. Don't just show the code!

- 3. A description of your forward-mode hazard handling mechanisms. Document the conditions under which you stall or cancel stages and forward data.

- 4. Documentation of your testing methodology (see above).