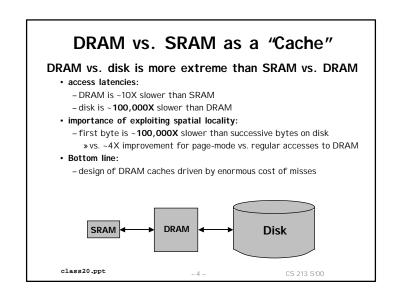

## Motivation #1: DRAM a "Cache" for Disk The full address space is quite large: · 32-bit addresses: ~4,000,000,000 (4 billion) bytes • 64-bit addresses: ~16,000,000,000,000,000,000 (16 quintillion) bytes Disk storage is ~30X cheaper than DRAM storage • 8 GB of DRAM: ~\$12,000 • 8 GB of disk: ~\$400 To access large amounts of data in a cost-effective manner, the bulk of the data must be stored on disk 8 GB: ~\$400 256 MB: ~\$400 4 MB: ~\$400 SRAM DRAM Disk class20.ppt CS 213 S'00

# Impact of These Properties on Design

- If DRAM was to be organized similar to an SRAM cache, how would we set the following design parameters?

- · Line size?

- · Associativity?

- · Replacement policy (if associative)?

- · Write through or write back?

### What would the impact of these choices be on:

- · miss rate

- · hit time

- · miss latency

- tag overhead class20.ppt

- 5 -

CS 213 S'00

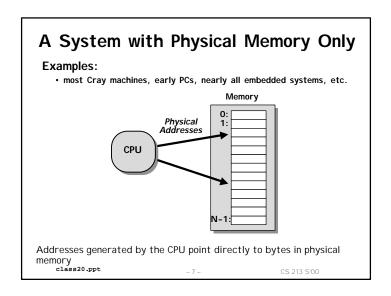

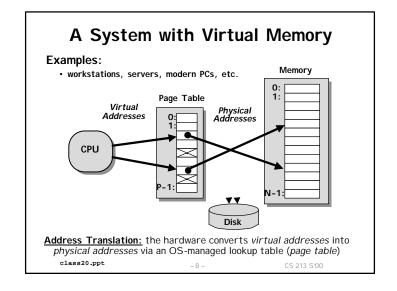

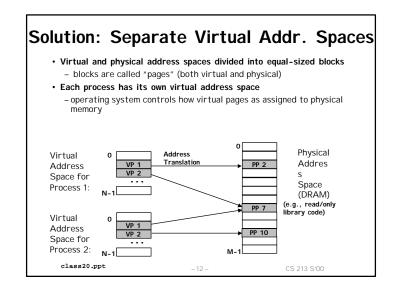

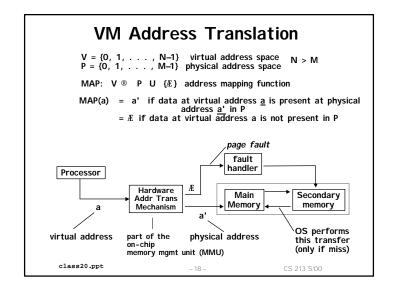

# **Summary: Motivations for VM**

- · Uses physical DRAM memory as a cache for the disk

- · address space of a process can exceed physical memory size

- sum of address spaces of multiple processes can exceed physical memory

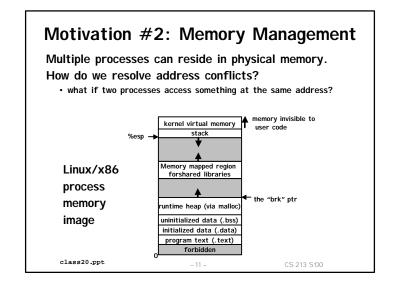

- Simplifies memory management

- · Can have multiple processes resident in main memory.

- Each process has its own address space (0, 1, 2, 3, ..., n-1)

- · Only "active" code and data is actually in memory

- Can easily allocate more memory to process as needed.

- external fragmentation problem nonexistent

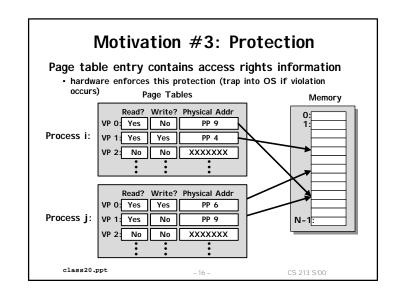

## Provides protection

- · One process can't interfere with another.

- because they operate in different address spaces.

- · User process cannot access privileged information

- different sections of address spaces have different permissions.

**class20.ppt** -17 - CS 213 S'00

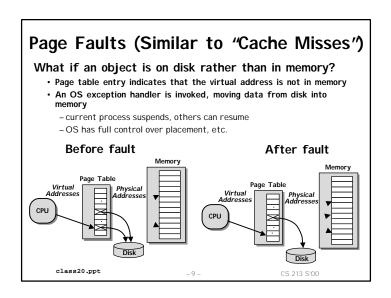

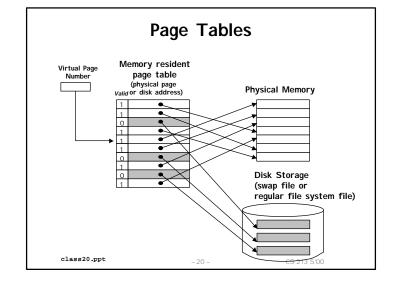

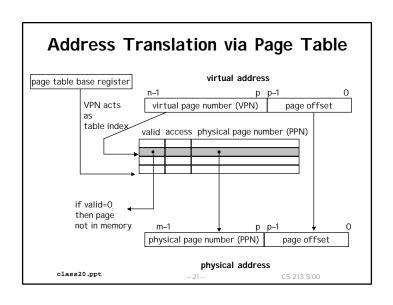

# **Page Table Operation**

#### **Translation**

- · Separate (set of) page table(s) per process

- VPN forms index into page table (points to a page table entry)

#### Computing Physical Address

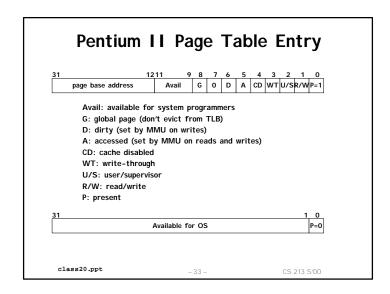

- · Page Table Entry (PTE) provides information about page

- if (valid bit = 1) then the page is in memory.

- » Use physical page number (PPN) to construct address

- if (valid bit = 0) then the page is on disk

- » Page fault

- » Must load page from disk into main memory before continuing

#### **Checking Protection**

- · Access rights field indicate allowable access

- e.g., read-only, read-write, execute-only

- typically support multiple protection modes (e.g., kernel vs. user)

- · Protection violation fault if user doesn't have necessary permission

class20.ppt -22- CS 213 S'00

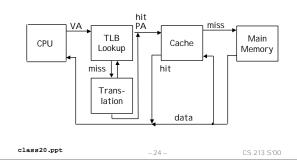

# Speeding up Translation with a TLB

#### "Translation Lookaside Buffer" (TLB)

- · Small hardware cache in MMU

- · Maps virtual page numbers to physical page numbers

- · Contains complete page table entries for small number of pages

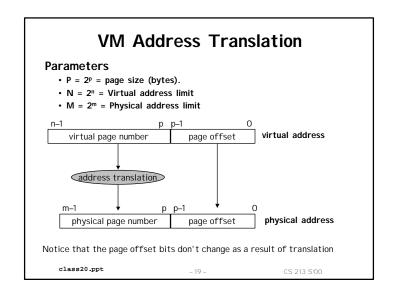

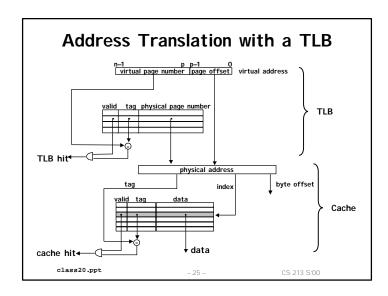

# Address translation summary

### Symbols:

- · Components of the virtual address (VA)

- TLBI: TLB index

- TLBT: TLB tag

- VPO: virtual page offset

- VPN: virtual page number

- · Components of the physical address (PA)

- PPO: physical page offset (same as VPO)

- PPN: physical page number

- CO: byte offset within cache line

- CI: cache index

- CT: cache tag

class20.ppt

CS 213 S'00

# Address translation summary (cont)

#### Processor:

- execute an instruction to read the word at address VA into a register.

- · send VA to MMU

#### • MMU:

- · receive VA from MMU

- extract TLBI, TLBT, and VPO from VA.

- if TLB[TLBI].valid and TLB[TLBI].tag = TLBT, then TLB hit.

- note: requires no off-chip memory references.

- if TLB hit:

- read PPN from TLB line.

- construct PA = PPN+VPO (+ is bit concatenation operator)

- send PA to cache

- note: requires no off-chip memory references

class20.ppt -27 - CS 213 S'00

# Address translation summary (cont)

-26 -

### MMU (cont)

- if TLB miss:

- if PTE[VPN].valid, then page table hit.

- if page table hit:

- » PPN = PTE[VPN].ppn

- » PA = PPN+VPO (+ is bit concatenation operator)

- » send PA to cache

- » note: requires an off-chip memory reference to the page table.

- if page table miss:

- » transfer control to OS via page fault exception.

- » OS will load missing page and restart instruction.

### Cache:

- · receive PA from MMU

- extract CO, CI, and CT from PA

- use CO, CI, and CT to access cache in the normal way.

class20.ppt

– 28 –

CS 213 S'00

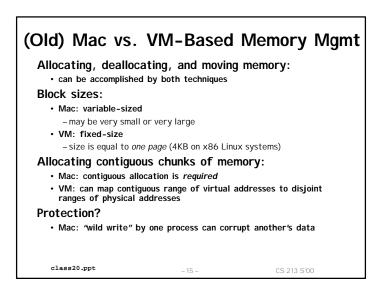

## **Main Themes**

### Programmer's View

- · Large "flat" address space

- Can allocate large blocks of contiguous addresses

- · Processor "owns" machine

- Has private address space

- Unaffected by behavior of other processes

## System View

- · User virtual address space created by mapping to set of pages

- Need not be contiguous

- Allocated dynamically

- Enforce protection during address translation

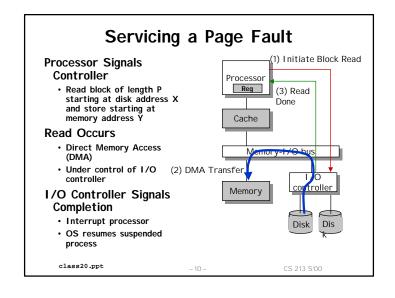

- · OS manages many processes simultaneously

- Continually switching among processes

- Especially when one must wait for resource

- » E.g., disk I/O to handle page fault

**class20.ppt** -34- CS 213 S'00